Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных устройствах.

Известно множительно-делительное устройство 1. В этих устройствах, как правило, не учитывается ногрешность, зависящая от размерности делимого и делителя, а также невозможно выполнять операции деления в случае, если делимое меньше делителя.

Наиболее близким техническим решением к данному предложению является множительно-делительное устройство, содержащее генератор импульсов, первый и второй делители частоты, соединяемые с информационными входами устройства, счетчик результата 2.

Недостатком его является невысокая точность выполнения операций.

Цель изобретения заключается в повышении точности устройства.

Цель изобретения достигается тем, что устройство содержит масштабный преобразователь, блок перезаписи кода, счетчик циклов операций, причем выход генератора импульсов подключен к первым входам масштабного преобразователя и второго делителя частоты, первый выход масштабного преобразователя соединен с первым входом первого делителя частоты, второй вход которого

,., - „ ,...„ . ..соеди ген с выходом блока перезаписи кодг:, а выход с первым управляющим входом масштабного преобразователя, а также с первыми входамп счетчика циклов операций, блока перезаписи кода и счетчика результата, второй вход которого соединен с первым выходом второго делителя частоты, второп выход которого соединен со вторым входом перезаписи, управляющий выход которого соединс со вторым управляющим входом масштабного преобразователя, первый вход счетчика циклов операций соединен со вторым входом масштабного иреобразователя, второй вход счетчика циклов операций соединен с шиной установки точности вычислений.

Таким образом, в предложенном устройстве осуществляется нреобразование делимого Л в эквивалентный интервал времени, заполняемый счетными имнульсами с частотой обратно пропор ;иоиальной значению делителя В, причем Л S, деление производится до получения , значение которого перезаписывается в запоминающий регистр делимого, умножается на коэффициепт 10, где п выбирается из условия Рх 10 -С 5 Я X 10, при А В значение .4 умножается на коэффициент Ю , пде k выбирается из условия А X В А X 10.

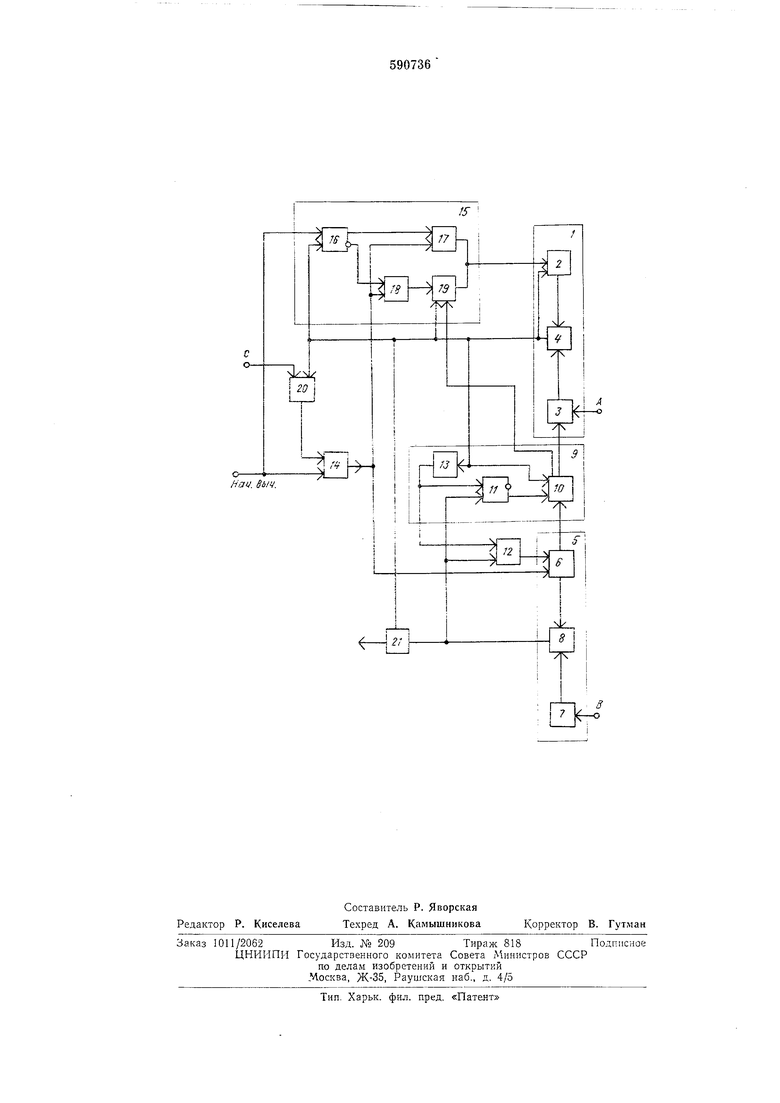

На чертеже представлена блок-схема устройства. Схема содержит первый делитель частоты 1, счетчик 2, запоминающий регистр 3, схему сравнения 4, второй делитель частоты 5, счетчик 6, запоминающий регистр 7, схему сравнения 8, блок перезаписи кода 9, блок трехвходовых схем И 10, триггер //, элемент ИЛИ 12, элемент задержки 13, генератор импульсов 14, масштабный преобразователь 15, триггер 16, элементы И 17, 18, декадный множитель 19, счетчик циклов онераций 20, счетчик результата 21.

Первый делитель частоты / предназначен для формирования временного интервала, проиорционального значению делимого А, содержит счетчик 2 и запоминающий регистр 3, между информационными выхода.ми которых включена схема сравнения 4. Второй делитель частоты 5 предназначен для формирования частоты, обратно пропорциональной величине значения В, содержит счетчик 6 и запоминающий регистр 7, между информационными выходами которых включена схема сравнения 8.

В запоминающие регистры 3, 7 через информационные входы устройства вводятся соответственно значения делимого А и делителя В. Информационные выходы счетчика 6, которые образуют второй выход второго делителя частоты 5, через вторые входы блока нерезаииси 9 и далее через его первый выход соединены с первым входом первого делителя частоты 1, т. е. они соединяются с инфорл1ационными входами запоминающего регистра 3, первого делителя частоты /.

Блок перезаписи кода 9 содержит блок трехвходовых схем И 10. Один вход каждой из них (эти входы образуют второй вход блока перезаписи 9) соединен с выходами соответствующих разрядов счетчика /; (эти выходы образуют второй выход второго делителя частоты 5). Второй вход каждой из блока трехвходовых схем И 10 соединен с единичным выходом триггера //, а третий вход каждой «из схем И блока трехвходовых схем И 10 соединен с выходом схемы сравнения 4, который :является выходом /первого делителя частоты /. Этот выход помимо этого соединен с первым управляющим входом масщтабного преобразователя 15 и далее в нем с декадным множителем 19, а также с первыми входами счетчика циклов операций 20, блока перезаписи кода 9 и далее в нем с элементом задержки 13, счетчика результата , и шиной сброса счетчика 2. Шина сброса счетчика 6 соединена через элемент ИЛР1 }2, ее первый вход с выходом схемы сравнения 8, который является выходом второго делителя частоты 5, этот же выход соединен с нулевым входом триггера 11 и вторым входом счетчика результата 21. Единич 1ый вход триггера // соединен с линией задержки 13 и вторым входом элемента РТЛИ 12. Масштабный преобразователь 15 содержит триггер 16, предназначенный для управления масштабом преобразования, для чего единичный и нулевой входы триггера 16 соединены соответственно с входом устройства «начало вычислений и с выходом устройства сравнения 4, т. е. выходом первого делителя частоты.

Единичный и нулевой выходы триггера 16 соединены с нервымн входами элементов И .17, 18, вторые входы которых соединены с выходом генератора импульсов 14 и счетным входом счетчика 6, являющегося иервым входом второго делителя частоты 5. Выход элемента И 17 неносредственно, а выход элемента И 18 через декадный множитель 19 соединены со счетным входом счетчика 2, являющегося входом первого делителя частоты. Первый управляющий вход декадного множителя 19 соединен с унравляющим выходом блока перезаписи кода 9.

Рассмотрим работу устройства при выполпении операции Л : 5 с точностью до С знаков после занятой: А 4129, В 825, . Значения А и В выбраны таким образом, чтобы в процессе деления возникла ситуация, когда в заноминающий регистр 3 заиишется число меньше, чем в заноминающий регистр 7, что аналогично рассмотрению принципа работы устройства при условии А, В.

Перед началом вычисления в запоминающие регистры 3, 7 вводятся через информационные входы устройства соответственно чнсла 4129 и 825, а в счетчике циклов операций 20 устанавлнвается число К С + I 4 -f 1 5. Поступающий на вход устройства сигнал «начало вычислений включит генератор импульсов 14 и переведет триггер 16 в единичное состояние, в результате чего в счетчик 2 через иервый вход первого делителя частоты / через элемент И 17 и в счетчик 6 через первый вход второго делителя частоты начнут ноступать счетные импульсы с выхода генератора импульсов 14 с частотой fo- При наконленни счетчиком 6 числа 825 срабатывает устройство сравнения 8, на его выходе, т. е. на выходе второго делителя частоты 5 появится сигнал, который:

-запишет единицу в счетчик результата 21;

-установит в «О счетчик 6 через элемент ИЛИ 12;

-переведет триггер 11 в единичное состояние, иодготовив тем самым через блок трехвходовых схем И 10 перезапись кода счетчика 6 в заноминающий регистр 5.

Далее второй делитель частоты 5 работает аналогичным образом, занося каждый 825 импульс в счетчик результата 20, каждый раз после этого срабатывает в «О счетчик 6 и подтверждает состояние «1 триггера //. Когда пройдет 4125 825x5 импульсов от генератора импульсов 14, второй делитель частоты срабатывает пять раз, а в счетчик результата запишется число 5. После 4125 импульса счетчик 6 в очередной (нятый раз) сброснтся в «О. По приходе 4129 импульса,

в счетчик 6 при этом запишется число 4, срабатывает схема сравнения 4, на его выходе, т. е. на выходе первого делителя частоты 1 появится сигнал, который:

-установит в «О счетчик 2;«

-переведет триггер 16 в нулевое состояние, закрыв тем самым элемент И 17 и открыв элемент И 18 для прохождения через нее импульсов с генератора импульсов 14;

-установит в декадном множителе 19 коэффициент деления

-разрешит нерезапись кода счетчика 6 (к этому моменту в счетчике 6 будет записано число 4) в запоминающий регистр 3. При этом в момент перезаписи на управляющем выходе блока перезаннси 9 появляется импульс, который, проходя на второй управляющий вход масштабного нреобразователя

15, подтвердит установку коэффициента «10 в декадном множителе

-запишет единицу в счетчнк циклов онерадий 20;

-зафиксирует положение запятой {определения целой части результата вычислений

в счетчнке результата 21, равной 5,...).

Этот сигнал через некоторое время, необходимое для перезаписи кода, через элемент задержки 13 возвратит триггер 11 ъ нулевое состояние (запрет перезаписи) и через элемент ИЛИ 12 установит в «О счетчик 6.

На этом заканчивается первый цикл деления.

В следующем втором цикле деления при заполнении счетчика 2 импульсами с частотой следования н счетчика с частотой /а

первым сработает схема сравнения 4 (в счетчике 2 записано число 4, в счетчике 6 - число 40), т. к. временной интервал TQ X 10,X 4, формируемый первым делителем частоты 1, меньше временного интервала Го X 825, фор:мируемого вторым делителем частоты 5. При срабатывании устройства сравнения 4, на его выходе (выход первого делителя частоты 1) появится сигнал, который:

-установит в «О счетчик 2;

-подтвердит нулевое состояние триггера 16;

-установит в декадном множителе 19 коэффициент деления 100;

-даст сигнал на перезапись кода с счетчика 6 в запоминающий регистр 3, но так как триггер // в нулевом состоянии, то такая перезапись не произойдет;

-запишет вторую единицу в счетчик циклов операций 20;

-зафиксирует в счетчик результата 21

в разряде десятичных чолей число «О (иро4129 „ ,

межуточный результат деления --, 5,0 . . .)

OZO

Этот же сигнал, пройдя через элемент задержки 13, подтвердит нулевое состояние триггера L1 и установит в «О счетчик 6.

В третьем цикле деления будут выполнены операции, аналогичные операциям второг го цикла с той лишь разницей, что счетчик 2 будет заполняться импульсами с частотой

следования . . Первым срабатывает схема

сравнения 4, т. к. формируемый первым .делитель частоты / временной пптервал TQ X 10 X 4 меньше интервала То X 825,формируемого вторым делителя частоты 5. В счетчике цик.тов операций 20 запишется число «3, в счетчике результата 21 запишется «О в разряд сотых долей (промежуточ4129

ный результат деления --,- 5,00 .. .). В

масштабном преобразователе 15 в декадном множителе 19 устанавливается коэффгщнент деления 1000. Остальные операции аналогичные как и во втором цикле.

В четвертом цикле деления при заполнеt .

НИИ счетчика 2 импульсами с частотой /(р,

а счетчика 6 с частотой, первЫ|М срабатывает схема сравнения 8. При этом пока в счетчик 2 запишется число «4 на счетчик 6 поступит число 4000. При этом из этих 4000 импульсов каждый 825, во втором делителе частоты я импульс, произведет операции, аналогичные операциям первого цикла:

-запишет число 4 после каждого набора числа 825 (825 X 4 3300) в счетчнк результата 21, разряд тысячных долей;

-установит в «О счетчик 6 после каж-дого набора числа 825;-

-переведет триггер // в единичное состояние.

Так будет продолжаться до тех пор, пока в счетчик 2 не запишется число 4 (с часто1о )

1000/

ПИЯ 4. В счетчике 6 прн этом, который заполняется с частотой, то при этом будет числа 700, т. к. он последний раз был сброшен .в «О на 825 X 4 3300 импульсов. Сигнал со схемы сравнения 4 при этом произведет еле-, дующие операции:

-установит в «О счетчик 2;

-подтвердит нулевое состояние триггера 16;

-установит в декадном множителе коэффициент деления 10000;

- осушествит перезапись числа 700 из счетчика 6 в запоминающий регистр 3, при этом в момент перезаписи на управляющем выходе блока перезаписи 9 появляется импульс, который пройдет на второй управляющий вход масштабного преобразователя 15 и далее на декадный множитель 19 и вместо коэффициента деления 10000 установит 10. (Этот сигнал строго предназначен для установления коэффициента 10, независимо от того, какой коэффициент там установлен ранее);

- запишет в счетчик циклов операции очередную единицу, общее число при этом станет равным 4.

Этот же сигнал через элемент задержки 13 установит триггер 11 в нулевое состояние, а также установит в «О через элемент ИЛИ 12 счетчик 6.

,В пятом цикле деления при заполнении счетчика 2 импульсами с частотой следоваА

10

«О первым сработает схема сравнения 8, в результате чего повторяется цикл операций аналогичный первому и четвертому циклам. В разряд десятитысячных долей счетчика результата 21 запишется число 8 (результаг деления 5,0048...). После чего при заполнении счетчика 2 до 700 импульсов сработает схема сравнения 4 и в счетчик циклов операций 20 запишется число 5, что вызовет }ia его выходе появление сигнала, включающего генератор импульсов 14, и фиксируюп 1.его конец вычислений.

2149 Результат деления „. 5,0048 будет

окончательным, т. к. количество циклов деления станет равным величине предустановки y( 5 в счетчике циклов операций 20.

Таким образом, при Л В (делимое больше делителя) вычисляется целая часть частного до получения остатка меньшего В, после чего остаток от деления автоматически умножается на 10 необходимое число раз до значения большего Вив процессе вычисления дробной части частного продолжателя аналогично вычислению целой части и т. д. При вычисление начинается с з множения А на ГО необходимое число раз. В том и в лруго.м случаях количество вычисленных десятичных знаков после запитой будет равно С.

Предложенное устройство может быть особенно эффективно использовано на стадии проведения научного эксперимента, опытов, где невысокое быстродействие компенсируется любой наперед заданной точностью

вычислений и простотой набора сомножителя.

Все элементы схемы представляют собой функционально законченные блоки, что позволяет широко применить интегральные микросхемы. Блочный принцип также создает в эксплуатации и взаимоза.меняемости блоков устройства.

Формула изобретения

10

Множительно-делительное устройство, содержащее генератор импульсов, первый и второй делители частоты, соединенные с информационными входами устройства, счетчик результата, отличающееся тем, что, с целью повышения точности устройства, оно содержит масштабный нреобразователь, блок перезаписи кода, счетчик циклов операций,

причем выход генератора импульсов подключен к первым входам масштабного преобразователя и второго делителя частоты, первый выход масштабного преобразователя соединен с первым входом первого делителя частоты, второй вход которого соединен с выходом блока перезаписи кода, а выход с первым управляющим входом масштабного преобразователя, а также с первыми входами счетчика циклов операций, блока перезаписи

кода и счетчика результата, второй вход которого соедипеи с первым выходом второго делителя частоты, второй выход которого соединен со вторым входом блока перезаписи кода, управляющий выход которого соединен

со вторым управляющим входом масштабного преобразователя, первый вход счетчика циклов операций соединен со вторым входом масштабного преобразователя, второй вход счетчика циклов операций соединен с шиной

установки точности вычислений.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР ДГо 416694, кл. G 06 F 7/39, 10.02.71.

2. Авторское свидетельство СССР № 392495, кл. G 06 F 7/39, 14.09.71.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1621025A1 |

| Множительно-делительное устройство | 1978 |

|

SU746511A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1968 |

|

SU217718A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Устройство синхронизации | 1990 |

|

SU1781835A1 |

| Автоматический следящий делитель периодов следования импульсов | 1981 |

|

SU970705A1 |

| Аналого-цифровое делительное устройство | 1975 |

|

SU533943A1 |

| Устройство для деления | 1986 |

|

SU1363203A1 |

Авторы

Даты

1978-01-30—Публикация

1975-09-01—Подача