Изобретение относится к микроэлектронике, а именно к производству полупроводниковых интегральных схем (ИС) высокой степени интеграции. В технологии ИС перспективным направлением является миниатюризация элементов схем с целью увеличения плотности компановки.

Известно несколько способов изготовления ИС, которые позволяют получить более 10000 элементов на кристалл. В этой связи большие значение приобретает надежность элементов ИС и улучшение их характеристик. Миниатюризация элементов ИС позволяет существенно уменьшить емкости р-n-переходов, повысить предельные частоты усиления, что благоприятно сказывается на динамических параметрах схемы. Но так как на кристалле сосредотачивается большое число элементов, то проблема уменьшения емкостей р-n-переходов остается актуальной.

Наиболее близок к предлагаемому способу способ изготовления интегральных схем, включающий формирование жесткой маски, создание рабочих областей структуры в объеме полупроводниковой подложки, вскрытие контактных окон и металлизацию.

По данному способу в монокристаллической подложке со сформированным локальным скрытым слоем и эпитаксиальной пленкой формируют жесткую маску, методом фотолитографии вскрывают окна для разделительной диффузии и глубокого р+-контакта к базовой области, которые формируют одновременно, вскрывают окна под базу, информируют при этом, базовая область перекрывается с глубоким р+-контактом, в базовом окне травят SiO2 и формируют эмиттер (эмиттерная и базовая области формируются в одном окне).

Однако большие емкости р-n-переходов (эмиттер-база, коллектор-база) ухудшают параметры ИС. При формировании электродов к эмиттеру наблюдаются закорачивания переходов эмиттер-база, что снижает надежность ИС.

Цель изобретения повышение надежности ИС.

Для этого согласно предлагаемому способу вскрывают базовые окна, наращивают поликристаллический кремний (Si*), легированный примесью противоположного типа проводимости эпитаксиальной пленке маскируют Si* диэлектрической пленкой, которая не травится в травителях для SiO2 и Si3N4, создают базовые области диффузией из поликристаллического кремния, методом фотолитографии удаляют диэлектрическую пленку и поликристаллический кремний везде, за исключением участков, где будет формироваться эмиттер под островками Si*, затем в монокристалле формируют меза-структуры для эмиттера травлением открытых участков базовой области, проводят подлегирование базовых областей с термическим окислением, удаляют диэлектрическую пленку, лежащую на участках поликристаллического кремния и формируют эмиттерный переход в меза-структуре так, чтобы он находился на уровне донной части вытравленных областей базы, а контактные окна вскрывают только к базе и глубокому коллектору.

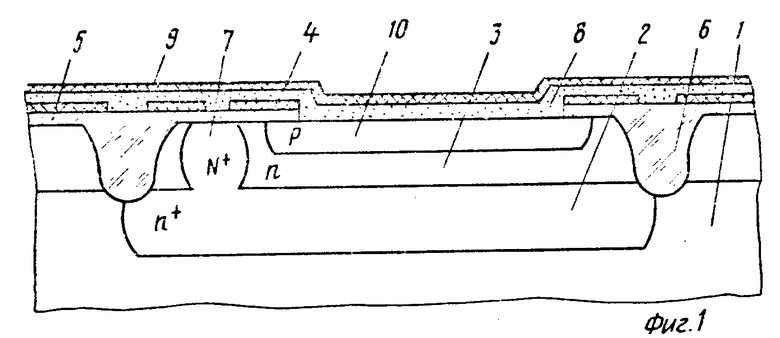

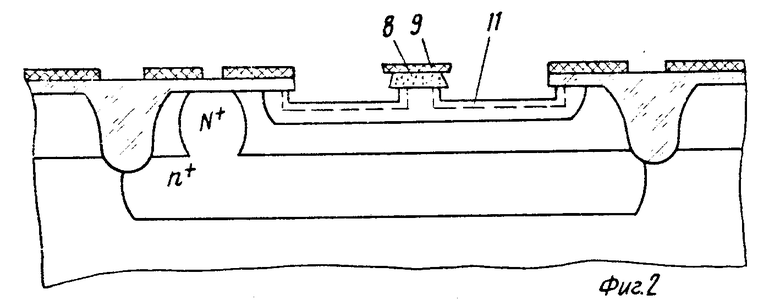

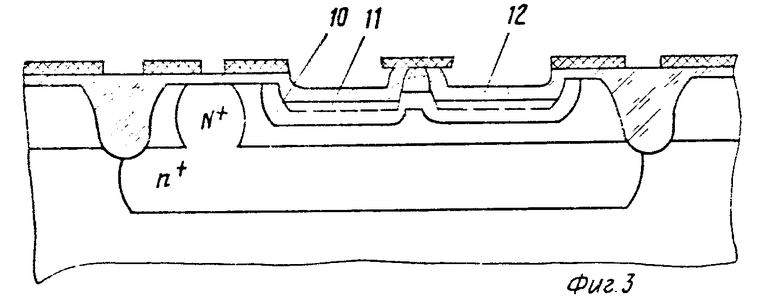

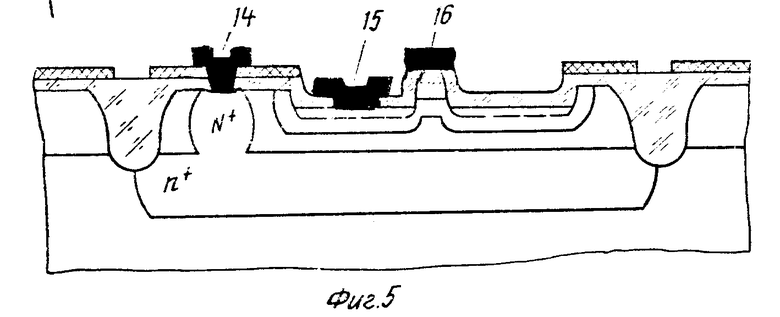

На фиг. 1-5 дана изопланарная технологическая схема изготовления ИС.

В монокристаллической подложке 1 известными методами формируют локальные открытые слои 2, наращивают эпитаксиальную пленку 3, на которой формируется жесткая маска, т.е. в диэлектрическом слое 4 (Si3N4) одновременно вскрывают все окна для формирования рабочих областей структуры. Далее, поочередно, вскрывают необходимые окна в диэлектрическом слое 5 (SiO2), маской при этом служит Si3N4. Все области структуры фиксируют в Si3N4 в одном фотолитографическом процессе. Последовательно (известным способом) формируют разделительные области 6, которые могут быть выполнены диэлектpиком (фиг. 1) или р-n-переходом, и глубокие контакты к коллектору 7.

После вскрытия базового окна выращивают поликристаллический кремний 8, легированный бором. Поликристаллический кремний маскируется диэлектрической пленкой 9 (Al2O3).

Толщина поликристаллического кремния составляет 0,3-0,5 мкм, а Al2O3 0,15-0,25 мкм. Путем термического отжига формируют базовую область 10 из поликристаллического кремния (фиг. 1).

Методом фотолитографии удаляют Al2O3 и поликристаллический кремний со всей поверхности, за исключением тех участков, где будет формироваться эмиттер, вытравляют открытые участки базовой области, примерно на половину глубины сформированной базы и формируют р++-базовые области 11 (фиг. 2) с последующим термическим окислением 12 этих областей и торцов поликристаллического кремния (фиг. 3). В открытую удаляют Al2O3 и формируют эмиттер 13 методом диффузии или ионным легированием (фиг. 4). Глубина эмиттерной диффузии не должна превышать общей толщины поликристаллического кремния и глубины вытравленной базовой области.

Далее вскрывают контактные окна к глубокому коллектору и базе формируют металлизированную разводку к коллектору 14, базе 15 и коллектору 16 (фиг. 5).

Таким образом, получают транзисторную структуру, состоящую из базовой области с низкой концентрацией примеси в активной области базы и по периметру коллекторного перехода, с высокой концентрацией примеси в пассивных областях базы и мезы, окруженной окисью кремния, в которой формируется эмиттер.

Высокоомная базовая область по периметру коллекторного перехода и в активной части базы уменьшает емкость последнего и улучшает коэффициент усиления транзисторных структур. Так как эмиттер по периметру изолирован окисью кремния, то его емкость также значительно уменьшается. Это позволяет значительно улучшить быстродействие ИС.

Поликристалл в областях эмиттера позволяет получать надежный омический контакт, предотвращающий закорачивание перехода эмиттер-база, что повышает надежность ИС.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОНСТРУКЦИЯ ИНТЕГРАЛЬНЫХ СХЕМ С КОМБИНИРОВАННОЙ ИЗОЛЯЦИЕЙ И СПОСОБ ИХ ИЗГОТОВЛЕНИЯ | 1980 |

|

SU824824A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩАЮЩИХСЯ ПЛАНАРНЫХ ТРАНЗИСТОРОВ | 1978 |

|

SU723984A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОСЛОЙНЫХ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ С БОКОВОЙ ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1980 |

|

SU880167A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ С ПРИСТЕНОЧНЫМИ p-n-ПЕРЕХОДАМИ | 1983 |

|

SU1178269A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ С ПРИСТЕНОЧНЫМИ p-n-ПЕРЕХОДАМИ | 1981 |

|

SU1072666A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ С ПРИСТЕНОЧНЫМИ P-N-ПЕРЕХОДАМИ | 1984 |

|

SU1215550A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ ТРАНЗИСТОРОВ | 1985 |

|

SU1371445A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ С БОКОВОЙ ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1982 |

|

SU1060066A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИС НА БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 1988 |

|

SU1538830A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ | 1981 |

|

SU952051A1 |

СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ, включающий формирование жесткой маски, создание рабочих областей структуры в объеме полупроводниковой подложки, вскрытие контактных окон и металлизацию, отличающийся тем, что, с целью повышения надежности интегральной схемы, вскрывают базовые окна, наращивают поликристаллический кремний (Si*), легированный примесью противоположного типа проводимости эпитаксиальной пленке, маскируют Si* диэлектрической пленкой, которая не травится в травителях для SiO2 и Si3N4, создают базовые области диффузией из поликристаллического кремния, методом фотолитографии удаляют диэлектрическую пленку и поликристаллический кремний везде, за исключением участков, где будет формироваться эмиттер под островками Si*, затем в монокристалле формируют меза-структуры для эмиттера травлением открытых участков базовой области, проводят подлегирование базовых областей с термическим окислением, удаляют диэлектрическую пленку, лежащую на участках поликристаллического кремния и формируют эмиттерный переход в меза-структуре так, чтобы он находился на уровне донной части вытравленных областей базы, а контактные окна вскрывают только к базе и глубокому коллектору.

СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ, включающий формирование жесткой маски, создание рабочих областей структуры в объеме полупроводниковой подложки, вскрытие контактных окон и металлизацию, отличающийся тем, что, с целью повышения надежности интегральной схемы, вскрывают базовые окна, наращивают поликристаллический кремний (Si*), легированный примесью противоположного типа проводимости эпитаксиальной пленке, маскируют Si* диэлектрической пленкой, которая не травится в травителях два SiO2 и Si3N4, создают базовые области диффузией из поликристаллического кремния, методом фотолитографии удаляют диэлектрическую пленку и поликристаллический кремний везде, за исключением участков, где будет формироваться эмиттер под островками Si*, затем в монокристалле формируют меза-структуры для эмиттера травлением открытых участков базовой области, проводят подлегирование базовых областей с термическим окислением, удаляют диэлектрическую пленку, лежащую на участках поликристаллического кремния и формируют эмиттерный переход в меза-структуре так, чтобы он находился на уровне донной части вытравленных областей базы, а контактные окна вскрывают только к базе и глубокому коллектору.

| СПОСОБ КОМПЕНСАЦИИ АДДИТИВНОЙ ТЕМПЕРАТУРНОЙ ПОГРЕШНОСТИ ДАТЧИКА С ВИБРИРУЮЩИМ ЭЛЕМЕНТОМ | 2005 |

|

RU2282162C1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Патент США N 3837936, кл | |||

| Раздвижной паровозный золотник с подвижными по его скалке поршнями между упорными шайбами | 1922 |

|

SU148A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

Авторы

Даты

1996-03-27—Публикация

1978-03-31—Подача