Изобретение относится к области микроэлектроники и может быть использовано в производстве полупроводниковых интегральных схем.

В известном способе получения самосовмещающихся полупроводниковых приборов на подложке маскированной диэлектрической пленкой формируют фиксирующую маску, а потом поочередно открывают необходимые окна в фоторезистивной маске и формируются рабочие области прибора, ионным легированием фиксация разделительных областей, глубокого контакта к коллектору осуществляется за счет формирования фиксирующей маски, а фиксация контактов к коллектору, базе и эмиттеру осуществляется дополнительным маскированием нитридом кремния данных областей без применения фотолитографии. Данному способу присущи следующие недостатки:

Большое количество фотолитографических операций для получения транзисторных структур.

Базовая область не фиксирована относительно разделительных и контактных областей.

Известен способ изготовления самосовмещающихся планарных транзисторов, включающий операции маскирования подложки диэлектрической пленкой, вскрытие окон, наращивание поликристаллического кремния, легированного примесью противоположного типа проводимости подложке, формирования базовой области и контакта к ней из поликристаллического кремния, создания эмиттера и металлизации.

В данном способе базовая область формируется из поликристаллического кремния Si*, легированного бором. Si* одновременно выполняет роль самосовмещенного контакта к базе. В Si* вскрывается окно и формируется эмиттерная область. Данный способ является наиболее близким к предлагаемому техническому решению и принимается в качестве прототипа.

Данный способ обладает тем недостатком, что эмиттерная область не фиксируется относительно базового контакта, что снижает плотность компоновки структур, а эмиттерный переход частично формируется в Si*, что вызывает ухудшение характеристик транзисторных структур (повышенные токи утечки перехода эмиттер-база).

Целью изобретения является повышение плотности компоновки структур.

Данная цель достигается тем, что на нижнюю диэлектрическую пленку наносят поликристаллический кремний, травят окна в пленках до подложки, наносят низкотемпературный поликристаллический кремний, легированный примесью противоположного типа проводимости подложке, локально маскируют диэлектрической пленкой не травящейся в травителях для двуокиси кремния и поликристаллического кремния места будущего эмиттера, проводят термообработку для формирования базовой области, удаляют поликристаллический кремний легированный примесью противоположного типа проводимости подложке со всей поверхности за исключением контакта к базе и в местах будущего эмиттера, осуществляют подлегирование базовой области и контакта к ней с выращиванием окиси кремния, травят участки верхней диэлектрической пленки и поликристаллического кремния, лежащего к ней. При формировании совмещенного контакта к базе из Si одновременно фиксируется область эмиттера участками верхней диэлектрической планки, а эмиттерный переход формируется в объеме полупроводника.

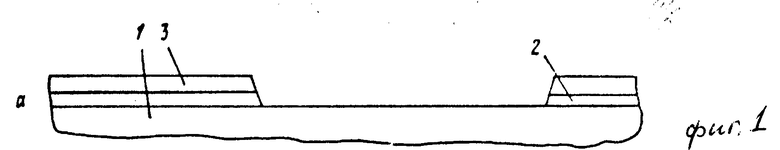

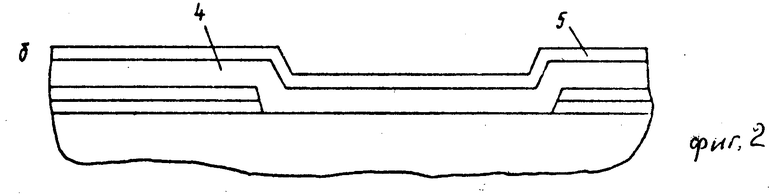

Предлагаемое изобретение иллюстрируется чертежом. На фиг. 1 показан способ изготовления n-p-n-транзистора. Изготовление р-n-p-транзистора не вызывает трудностей. Монокристаллическая подложка n-типа 1 маскируется нитридом кремния 2 и поликристаллическим кремнием 3. Методом фотолитографии вскрывают окна в пленке 3 и 2 (фиг. 1) наращивают поликристаллический кремний, легированный бором 4, последний маскируют нитридом кремния 5 (фиг. 2).

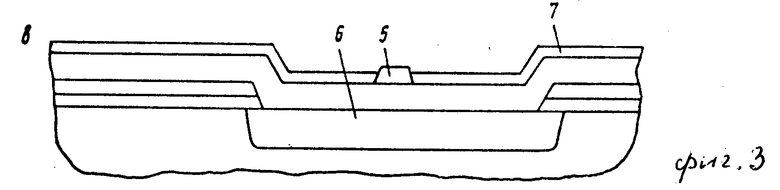

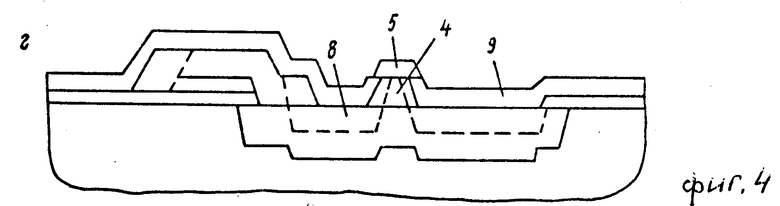

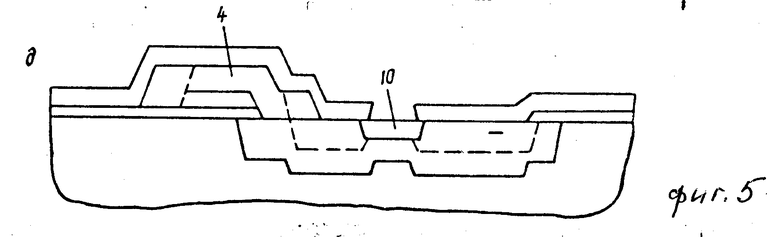

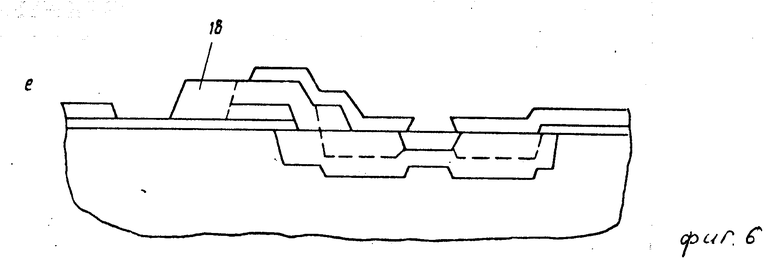

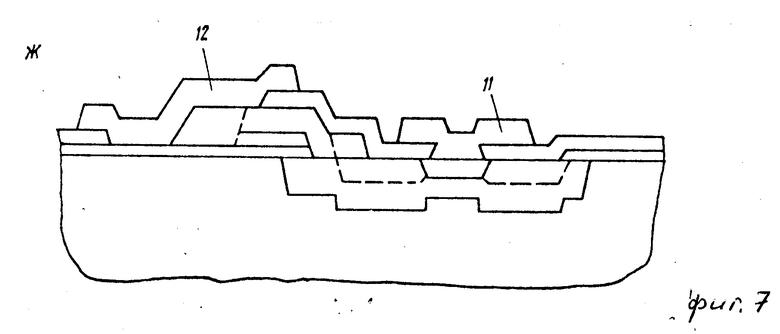

Методом фотолитографии удаляют нитрид кремния 5 со всей поверхности за исключением тех участков, где будет формироваться эмиттер и формируют базовую область 6, источником примеси для которой служит легированный поликристаллический кремний, с выращиванием SiO2-7 в участках, не защищенных нитридом кремния (фиг. 3). Далее удаляют SiO2-7, поликристаллическую пленку 4 везде, за исключением контактов к сформированной базе и мест, маскированных пленкой 5 (на чертеже данная операция не показана). В открытых участках формируют Р+-области с выращиванием SiO2-9, при этом прокисляется поликристаллическая пленка 3 (фиг. 4). Травят в открытую диэлектрическую пленку 5, поликристаллическую пленку 4, открывая окно для эмиттерной области и формируют эмиттер 10 (фиг. 5). Контактные окна для базовой области формируются в поликристаллической пленке 4, которая имеет с базовой областью контакт в местах, где сформирована р+-область 8 (фиг. 6) и производят металлизированную разводку 11, 12 (фиг. 7).

В предлагаемом изобретении достигнуто совмещение базовой области с базовым контактом и с эмиттером. Следует указать, что такое совмещение достигнуто с помощью двух фотолитографических операций, т.е. при первой фотолитографии фиксируются участки под эмиттер (фиг. 3), при второй фотолитографии фиксируется базовая область и контакт к ней и автоматически совмещается эмиттер, так как его участки маскированы нитридом кремния 5.

Предложенный способ пригоден для изготовления транзисторных структур как в отдельности, так и в составе ИС. При изготовлении ИС в диэлектрической пленке 2 создается фиксирующая маска, т.е. вскрываются сразу одновременно окна для разделительных областей, глубокого контакта к коллектору и для базовой области. Последовательно открываются окна и формируются области разделения и глубокий контакт соответственно. Далее операции идентичны предлагаемому изобретению. Области резисторов могут создаваться в поликристаллической пленке 4, в монокристаллической подложке 1 одновременно с подлегированием базовой области, а контакты к резисторам аналогично контактам базовой области.

Таким образом, предлагаемое изобретение позволяет получить транзисторные структуры, обладающие абсолютным самосовмещением как внутри структуры, так и относительно друг друга. В таком случае отсутствуют допуски на совмещение фотошаблонов при их позицировании на пластине и существенно повышается степень компановки транзисторных структур.

Предложенный способ исключает формирование эмиттерного перехода в поликремнии, что улучшает характеристики структур. Расчет топологии структур при следующих допусках: ширина вскрываемых окон 3 мкм, ширина проводящих дорожек 7 мкм; расстояние между проводящими дорожками 4 мкм, показал, что транзисторная структура занимает площадь на пластине 130-160 мкм2, а в составе ИС 500-550 мкм2.

П р и м е р. Монокристаллическая подложка n-типа проводимости маскируется нитридом кремния толщиной 0,1-0,15 мкм и нелегированным поликристаллическим кремнием толщиной 0,15-0,2 мкм.

Методом фотолитографии вскрывают окна в поликристаллическом кремнии и Si3N4 и наращивают поликристаллический кремний легированный бором в процессе эпитакции. Концентрация бора в поликристаллическом кремнии 5·1017 см-3, и его толщина 0,4-0,6 мкм. Поликристаллический кремний, легированный бором, маскируется нитридом кремния толщиной 0,1-0,15 мкм. Методом фотолитографии травят верхнюю пленку нитрида со всей поверхности; за исключением тех участков, где будет формироваться эмиттер и контакт к коллектору. Термическим отжигом при Т 1150оС в течение 15 мин формируют базовую область в монокристаллической пленке n-типа проводимости. Получают параметры диффузионного слоя: x jσ 1-1,1 мкм, поверхностное сопротивление ρ sσ 800-850 Ом/□. Далее методом фотолитографии травят окисел кремния, образовавшийся при формировании базовой области и легированную пленку везде, за исключением контакта к базовой области и участков маскированных Si3N4.

Осуществляют легирование участков немаскированных поликристаллическим кремнием с выращиванием окисла кремния. Глубина подлегирования составляет 0,8-0,85 мкм с поверхностным сопротивлением, равным 290-320 Ом/□, при этом толщина выращенного окисла составляет 0,2-0,25 мкм. При формировании областей подлегирования происходит прокисление нелегированной поликристаллической пленки. В открытую удаляют участки нитрида кремния, травят поликристаллический кремний, находящийся под нитридом кремния, а также нижний слой нитрида кремния, находящийся под коллекторным контактом и методом диффузии формируют эмиттер и контакт к коллектору. Глубина эмиттерного перехода составляет 0,7-0,8 мкм, с поверхностным сопротивлением равным 8-9 Ом/□.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ | 1978 |

|

SU705934A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ | 1981 |

|

SU952051A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОСЛОЙНЫХ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ С БОКОВОЙ ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1980 |

|

SU880167A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ ТРАНЗИСТОРОВ | 1985 |

|

SU1371445A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ С ПРИСТЕНОЧНЫМИ p-n-ПЕРЕХОДАМИ | 1983 |

|

SU1178269A1 |

| КОНСТРУКЦИЯ ИНТЕГРАЛЬНЫХ СХЕМ С КОМБИНИРОВАННОЙ ИЗОЛЯЦИЕЙ И СПОСОБ ИХ ИЗГОТОВЛЕНИЯ | 1980 |

|

SU824824A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ СХЕМ | 1982 |

|

SU1111634A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ С ПРИСТЕНОЧНЫМИ p-n-ПЕРЕХОДАМИ | 1981 |

|

SU1072666A1 |

| Способ изготовления мощных ВЧ транзисторных структур | 1978 |

|

SU705924A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ СХЕМ | 1982 |

|

SU1840163A1 |

СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩАЮЩИХСЯ ПЛАНАРНЫХ ТРАНЗИСТОРОВ, включающий операции маскирования подложки диэлектрической пленкой, вскрытия окон, наращивания поликристаллического кремния, легированного примесью противоположного типа проводимости подложке, формирования базовой области и контакта к ней из поликристаллического кремния, создания эмиттера и металлизацию, отличающийся тем, что, с целью повышения плотности компановки структур, на нижнюю диэлектрическую пленку наносят поликристаллический кремний, травят окна в пленках до подложки, наращивают низкотемпературный поликристаллический кремний, легированный примесью противоположного типа проводимости подложке, локально маскируют диэлектрической пленкой, не травящейся в травителях для двуокиси кремния и поликристаллического кремния, места будущего эмиттера, проводят термообработку для формирования базовой области, удаляют поликристаллический кремний, легированный примесью противоположного типа проводимости подложке, со всей поверхности, за исключением контакта к базе и в местах будущего эмиттера, осуществляют подлегирование базовой области и контакта к ней с выращиванием окиси кремния, травят участки верхней диэлектрической пленки и поликристаллического кремния, лежащего под ней.

СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩАЮЩИХСЯ ПЛАНАРНЫХ ТРАНЗИСТОРОВ, включающий операции маскирования подложки диэлектрической пленкой, вскрытия окон, наращивания поликристаллического кремния, легированного примесью противоположного типа проводимости подложке, формирования базовой области и контакта к ней из поликристаллического кремния, создания эмиттера и металлизацию, отличающийся тем, что, с целью повышения плотности компановки структур, на нижнюю диэлектрическую пленку наносят поликристаллический кремний, травят окна в пленках до подложки, наращивают низкотемпературный поликристаллический кремний, легированный примесью противоположного типа проводимости подложке, локально маскируют диэлектрической пленкой, не травящейся в травителях для двуокиси кремния и поликристаллического кремния, места будущего эмиттера, проводят термообработку для формирования базовой области, удаляют поликристаллический кремний, легированный примесью противоположного типа проводимости подложке, со всей поверхности, за исключением контакта к базе и в местах будущего эмиттера, осуществляют подлегирование базовой области и контакта к ней с выращиванием окиси кремния, травят участки верхней диэлектрической пленки и поликристаллического кремния, лежащего под ней.

| СПОСОБ КОМПЕНСАЦИИ АДДИТИВНОЙ ТЕМПЕРАТУРНОЙ ПОГРЕШНОСТИ ДАТЧИКА С ВИБРИРУЮЩИМ ЭЛЕМЕНТОМ | 2005 |

|

RU2282162C1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| JEE I.Solice State Cireuits, v | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Способ обделки поверхностей приборов отопления с целью увеличения теплоотдачи | 1919 |

|

SU135A1 |

Авторы

Даты

1996-03-27—Публикация

1978-06-19—Подача