Iopa пмпульсои н выход jixoporo триггера соСДинены соответствспло с входамл первого :лемс1гга II, вв1ход которого связан е входо.м распределителя, выход первого элемента ИЛИ - с входом счетч1;ка, ввьчоды KoTOpoiO связаны с дешпфратором. Группа ннформаЦКОННВ1Х выходов дешифратора подключена к ipynnaw нпформацпоппых входов блока формированпя адреса и блока формпровапкя кода, управляющие входы которых еоедпнепы с перввьм уиравляюпдпм входо.м уетропетва, выходы б;юка формирования адреса- к соотвстствуюш,им адресным вв1ходам устройства, а выходы блока фор-мироваппя кода - к пиформацпонным выходам устройства. Первый выход распредсл1гтеля сосдпнен с первв1М входом второго элемента И, ввьход которого подключен к первому входу первого элсме1гга

ИЛИ, второй выход распреде:игтеля -е перBBIM входом первого триггера, выход когорого подключен к второму входу второго элемента И, третпй ВВ1ХОД распределителя - с первв1м входом второго элемента ИЛИ и вторым входом первого элемента ИЛИ. Четвертый вы.ход распределителя соедиасп с иторв1м входом блока формироваппя кода, входом третьего элемента И п трствим входом первого эле.меита ИЛИ, четверты вход которого связа{1 с вторым входо.м второго элемепта ИЛИ, первым входом второго триггера п вторы.м )нравляюгцим входом устройства. Второй вход второго триггера связан с ввьходом третвего элемента И, второй вход которого нодключеп к третвему входу устройства.

Кроме того, блок формирования адреса содержит элементы ИЛИ и элементы И. Еыход каждого элемента ИЛИ соединен с нерввьм зходом одного элемента И, вторВ1е входв элемситоБ И объединены н подключены к управляющему входу блока, ВЫХОДВ1 которого связапв соответственно с ввьходами элементов И. Иерввгй вход первого элемента ИЛИ соединен с первым входом пятого элемента ИЛИ п i: вторым входом блока, третчгй вход которого связан с вторвтми входами первого п пятого элементов ИЛИ и первым входом четвертого .элемента ИЛИ, третий вход первого и первый вход третвего элсмептов ИЛИ - с четверTBiM входом блока, первый вход которого подключен к третвему входу пятого элемента ИЛИ. Иятый вход блока соединен с четверТВ1МИ входами первого н нятого и вторым входом третьего элементов ИЛИ, щестой вход блока - с пятым входом нервого, третвим входом третьего н вторым входом четвертого элементов ИЛИ, седьмой вход блока - с щсстым входом первого, четвертым входом третьего, пятым входом HSiTOio н третьнм входом четвертого элементов ИЛИ. Восьмой вход блока связан е седьмым входом нервого п первым входом второго элементов Р1ЛИ, девятый вход блока - с восьмым входом первого, вторым входом второго п шестым входом нятого элементов Р1ЛИ, десятый вход блока -

Наряду е этим блок формирования кода еодержит б.ток нсреключенпй, счетчик, триггер, четв1ре группы элементов И и э.тсмепты ИЛ1-1. Выход каждого элемента ИЛИ соедпнеп е первым входом одного элемента И первой группы, выходы когорых связаны соответственно с выходамн блока. Вторые входы элементов И нервой группы нодключсны к первому управляющему входу блока, первые входы элементов И второй грунны - к первому выходу трпггера, вторым выходом связанHoio с первв1ми входа.ми элементов И третьей

грунлы, выходы которых соединены соответственно с входа.ми б.тока переключений. Выходы элеме1ггов И второй группы соед11неиы е нервымн входами эле.ментов ИЛИ, вторые входы этнх элементов ИЛИ - с выходами

блока нереключенн, а третьи входы элеменiOB ИЛИ-----с выходами эле.ментов И четвертой группы, нервые входы которых соответственно еоединены е выходами ечстчпка. Вторые входы элемептов И второй п третвей

труни подключепы к еоответствующнм входа.м блока, вторые входы эле.ментов И четверToii группы--к выходу носледнего элемента И rpeTBeii группы и первому входу трпггера, второй вход которого соедипен с входо.м счетчика и вторы.м управляющим входом блока.

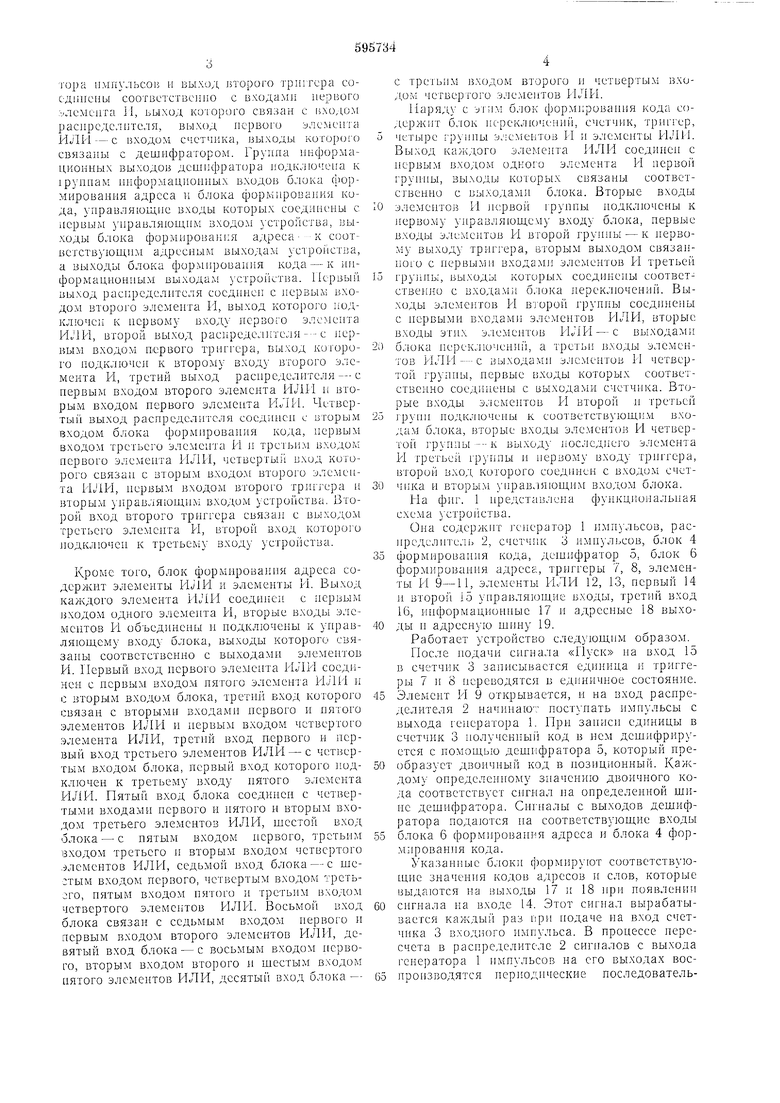

Иа фпг. 1 представлена функциональная схема yeTpoiicTBa.

Она содсржнт генератор 1 имнульсов, раснредел1ггель 2, счетч ш 3 имнульсов, блок 4

формировання кода, дешифратор 5. блок 6 формирования адреса, триггеры 7, 8, элементы И 9-11, элементы ИЛИ 12, 13, первый 14 и второй 15 управляющ.не входы, третий вход 16, информационные 17 н адресные 18 выходы н адресную шину 19.

Работает уетройство следующим образо.м. Иоеле нодачи сигнала «Г1уск на вход 15 в счетчик 3 записывается единица н тррнтеры 7 н 8 иереводятся в единичное состояние.

Элемент И 9 открывается, н на вход распределителя 2 начинаю-:; поступать пмпульсы с ввьхода генератора 1. При записи единицы в ечетчик 3 иолученньи код в ием дешифрируетея с помощью дешифратора 5, который преобразует двоичный код в позиционный. Каждому определенному значению двоичного кода соответствует сигнал иа определенной шипе дешифратора. Спгпалы с выходов дешифратора подаются на соответствующие входы

блока 6 формирования адреса и блока 4 фор.мпрованпя кода.

Указапнв1е блокн формируют соответствующие зпачення кодов адресов н слов, которые выдаются иа выходы 17 и 18 ири появ.тении

сигнала на входе 14. Этот сигнал вырабатывается каждьп раз при нодаче на вход счетчнка 3 вход;к)го пмиульса. В процессе переечета в распределнтеле 2 сигналов с выхода генератора 1 пмп льеов на его выходах воспропзводятся нериодпческие последовательHOCTii сигналов с разной частотою. В случае формнрор.ания инфор гацпи, представляющей собой периодически повторяемые кадры, состоящие каждый из множества строк, каждая из которых содержит некоторое количество слов, сигналы на первом выходе распределителя 2 поступают с частотой повторения слов. Сигналы на втором выходе определяют длительность времени, в течение которого вырабатывается информания, характеризующая строку, сигналы на третьем выходе - периоднчиост1 новтореиня строк, а сигналы на четвертом - иериодичиость всего массива формируемых сообщений.

Первый же сигнал с первого выхода распределителя проходит через открытый элемент И 10 и элемент ИЛИ 13 на счетный вход счетчика 3, в результате чего в счетчике запттсывается двойка. Ири этом сигнал появляется на соответствующем выходе дещифратооа 5, блоки 4 и б формируют соответствуюи,ие коду. записанно гу в счетчике 3. значен1 Я слова 1 адреса. Далее пронесс повторяется. С поступлением каждого последующего сигнала с первого выхода распределителя он проходит на счетный вход счетчика 3, гвелнчпвая его содержимое на единицу. В частном случае, ири необходимости выработки в начале каждой строки то.лько одного адреса (деблокирующего) без сопутствуюигего ему слона второй вглход дешифратора соединяется только с входом блока формирования адреса, а выходы деншфратора, начиная с третьего, подключаются к входам обоих блоков формирования. Если необходима в конце строки выработка только одного (блокирующего) адреса, вопрос также реитается путем нодсоединения последнего значащ.его выхода дешифратора только к блока Аоомирования адреса.

В нпоиесс пересчета в пасиределителе с его первого выходя на счетный вход счетчика 3 проходят сигналы до момента выработки сигна.та на втором выходе распределителя 2. после чего триггер 8 переводится в нулевое состояние н запирает элемент И 10, прекратая подачу сигналов на счетный вход счетчика и лстанавлпвяя его в исходное положение. В таком состоянин схема находится до момента обряяован1гя сигнала на третьем выходе раснпея лителя. Появивтпийся сигнал проходит через элемент ИЛИ 12. переводит триггер 8 R состоян1те «1 и через элемент ИЛИ 13 запттсыварт в счетчик 3 единицу.

Палее, через вновь ОТКРЫТЫЙ элемент И 10 опять 1тач1тиа1от проходить сигналы ня вход счетчика 3, и описанный процесс выработки адресов и слов повторяется. Такая последовательная выдача пнформацнн осуществляется до момента появления сигна.та на четвертом выходе распределителя. Этот сигнал подается на входы элементов И 11, ИЛИ 13 и на вход блока 4 формирования кода. Если на входе 16 имеется сигнал запрета, сигнал с четвертого выхода распределителя 2 проходит через элемент И 11 на вход триггера 7, перовпдя его в Tv.ieuoc состояние. При этом пре кращаютея подача сигналов с генератора илгпульсов па вход распределителя и выдача тсета. В сллчае отс тствия сигнала запрета на входе 16 в момент выработки сигнала па четвертом выходе распределителя 2 с четвертого выхота распределителя через элемент ИЛИ 13 ПРОХОДИТ па вход счетчика 3. записывая в нем СДИ1ПП1У, и далее процесс выдачи информации повторяется. Что касается блока 4 фопмиповаиия кода, то при подаче на его вход сигутала с четвертого выхода распределителя в нем осуществляются необходимые персключгчпя для выдачи новой информап.ии в следующем и,икле выработки теста.

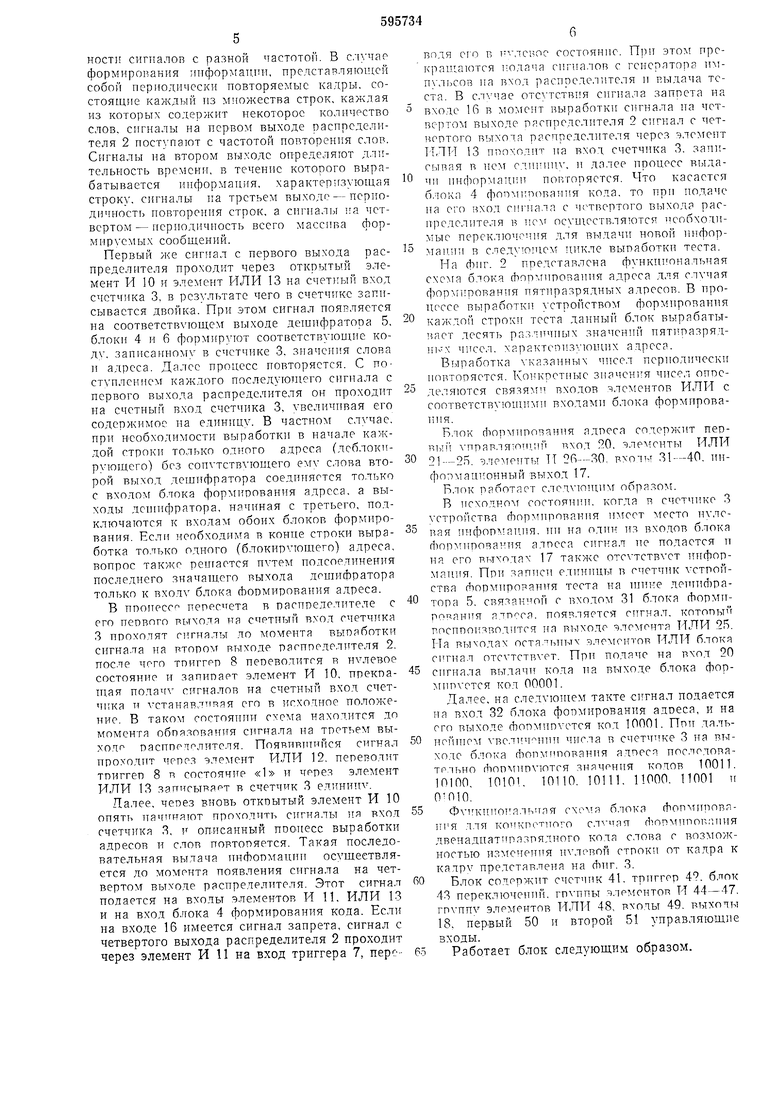

Иа фиг. 2 представлена функциональная схсхга блока (Ьормироваитш адреса для случая форлпфования пятиразряд,ных адресов. В процессе выработки устройством формирования каж:дой строки теста даиный блок вырабатывает десять различных значений пятиразрядньх чисел. характепиз ющих адреса.

Выработка казанных чисел пернодически иовтоояется. Конкретиые зиачения чисел определяются связями входов элементов ИЛИ с соответствующими входами блока формирования.

Блок Фор%уирования адреса содержит первь правляюи,ий вход 20, элементы ИЛИ 2b--2F). элементы И 26-30. вхоты 31-40. инфопмационный выход 17.

Блок работает следхюихим образом.

В исходном состоянии, когда в счетчике 3 устройства Нормирования имеет место нулевая инфор,ацпя. ИИ на один из входов блока rtiopMnpoBai-ия адпсса сигнал Tie подается тт на его выходах 17 также отсутствует инфор aция. При записи единтпгы в счетчик устройства Лормирорания теета на тиине детниАратора 5. связанной с входом 31 б.тока сЬормирования пдпГса. иоявляетея сигнал, КОТОРЫЙ лосиротпводится на выходе эле тентя ИЛИ 25. Иа выходах оста. элементов ИЛИ б.тока сигнал отсутствует. Прн подаче на вход 20 сигнала выдачтт кода Tia выходе блока формируется код 00001.

Лалее, на следующем такте сигнал подается на вход 32 блока формирования адреса, и на его выходе сЬормирУстся код 10001. ПРИ дальНСЙ1НСМ увеличении числа в счетчттке 3 на выходе блока dionMrmoBaHi адреса последовательно г11ОРмирУ1отся значения кодов 10011. 10100, 10101, 10110. 10111. 11000. 11001 It OOIO.

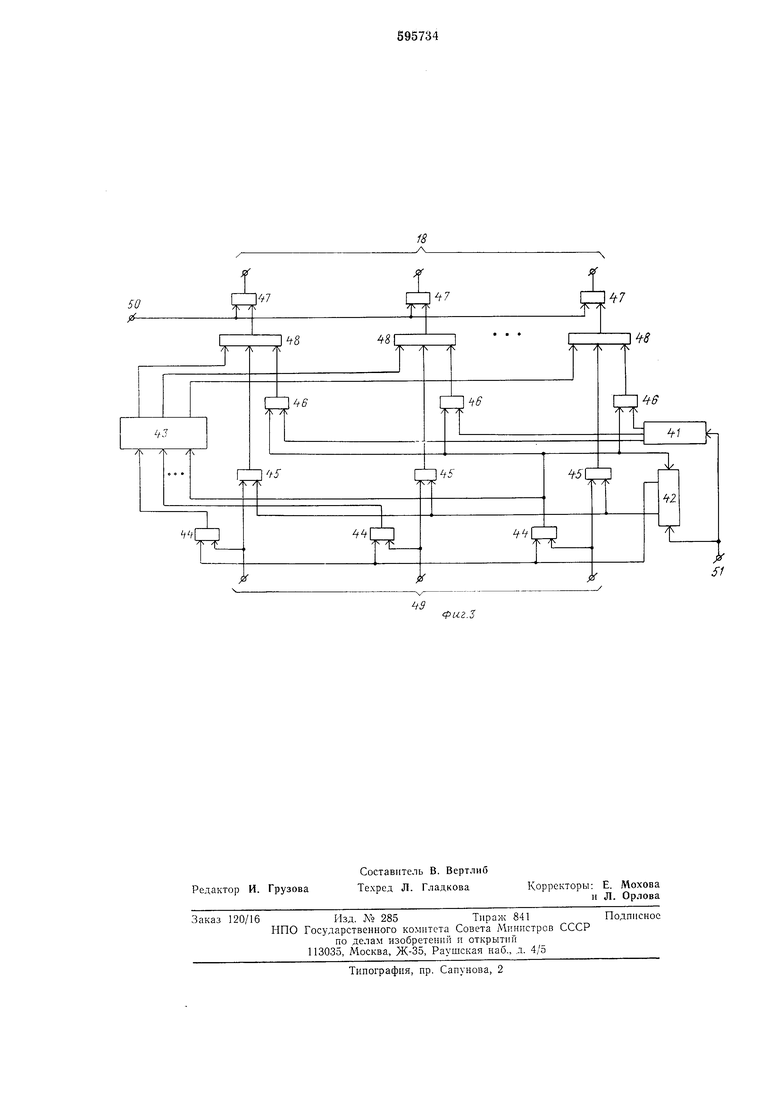

фучкниотяльиля схема блока Формировя Пя для коикротпого diopMnnoBinivm двенадцатиразрядного кода слова с возможностью изменения нллевой строки от кадра к кадру цредставлена на Лиг. 3.

Блок содержит счетчик 41. триггер 4. блок 43 переключенш. элементов И 44-47. ГРУППУ элементов ИЛИ 48, входы 49. выходы 18, первый 50 и второй 51 управляющие входы.

Работает блок следующим образом.

7

В процессе записи сигналов в счетчик 3 . устройства с дешифратора 5 подаются снгпады на входы 49, гачииая с первого слева входа. Первый сигнал нроходит через открытый в дапнв1Й момент соотвстстрлюи иТ элемент Н из группы элементов 44. Далее сигнал с выхода yпoмян тoгo элемента через блок 43 иереключеннн проходит на соответствующие входы элеме-гго) ИЛИ 48. На нх выходах воснроизводится совокунность нулей и единиц, характериз.ющих нервое елово Р, строке. Затем эти сги-налы ноступп от на входы э.тементов И 47 н на выход 18 нри нодаче па вход 50 уппазляюнлсго еоот1;стетву10Н1ей длител ности.

С 11ост -п,1еинсм .и.его сигнала на ,пй вход -стройства формнровання кода он про.ходит через следующий элемент PI из грхнпы элементов 44 н с его вв1хода через блок 43 нереключений па входы элемеитов Г1.ЛИ 48. Затем ирн подаче на вход 50 управляюидего енгнала военронзводимая на выходах элелкчгтов ИЛИ 48 1и- формац1- я. соответств 1ощая второму слову в строке, ггонадает через элементы И 47 на выходв 18. При rrocлeд ющнx сигналах ня выходах 18 блока формирования кода появляются соответствующие слоза г, кол.овом нредставлеинн.

Когда сигнал поступает иа после.ткий вхол 49 (крайний справа),на выходах элементов И 46 воспроизводится 1И1фоп тяиия. харйктер.изующая последнее елово н мевой етрок-и. причем значен1те этого едова онределяется содержанием информацни в ечетчике 41.

Далее осуществляется последователытая выдача на выходе 18 кодов дрлтих строк. Нормируемых через ГРУППУ элементов И 45. С появлением сигнала на четвертом выхо.яе распределителя 2 триггер 42 переводится в едипичное соетояипс (при ;том ппоисходттт переключение ГРУПП элементов И 44 и 45) и в счетч тт 41 зяииеывается елттнптта, что соответетв ет момеиту окончання полного и;нкла выдачи тщгЬорЛтации. Поеле этого ПРИ птг тствии сигтгаля запрета начинаетея новый ннкл выдачи теета. причем в слеп: ютттем ттттк.те последнее слово нулевой строки отличается от значения аналогичного слова в нредщеетвующем цикле, так как содержимое счетчика 41 Б блоке формирования кода изменяется от цнкла к циклу.

Таким обпазом. предложенное устрпйстго обеспечивает раснтиренне Лункциональных возможностей нутем обеспечения возхтжтгости оперативного изменения передаваемой контрольной информации как в статике, так и в динамике. В статике (перет началом передачи) изменение передаваелтой информяидш осуществляется с помощью блока . в блоке формирования кода. В дин.амчк(в нропессе передачи информации) ннформаци изменяется от цикла к циклу с счс:ч1;ка в блохе формирован1:я кеда,

,Я

Кроме того. 1 Сгрпйст;-:е М(;ж1-ю изменять независимо друг от друга адресные и кодовые части.

ф

распределитель, генератор имнульеов, триггер ii блок (Ьорм1 рс)вания кода, отл и чающеее я тем. что, с иелью расигирения функцион; /1ьпь х 1 О:1(/киоете : стройства путем обеспе Г:я вo)ro кпoeт оиратив гого изменения -араметпов н р-жимов пповерки, в него введс-ы счетчик. Д;;чичг1)рато), блок сЬормироваиия адреса, трштер, два элемента ПЛИ-н три элемента И, прстчем )Д генератора имиулг еов : выхо. второго триггера соединены cooTijcTCTBeHFio е входами нервого элемента И. ых()д кодорого связал с входом распределителя. нервогч) элемента ИЛИ соеди1еч с входом счетчик;:, шнходы которого свянаны с Д Н ифраторо :, пуппа ииформациоп Глх выхо.1ог деи1нфрлтора епсдщтена с группами информационных входов блока формирования адреса и бдока формирования кода. уггрэг.-яюп1не вхолы КОТОРЫХ соединены е нерв;:1М н: азля1оии1М вхолом стройства, выходы блока фор(1рован я чрста связаны с соотг тст /.ноп1ИА1 ядпесн)-,ми выходами устройства. .;,хп-тг,т блока фор тировапия кода подклюн ьг к П1 форман1-опным выходам устройства. .тй раепрелелителя еоединен с nepBtjiM ,холпм второго элехтента И, выход которого подключен к первому входу первого элемепта ИЛИ, второй выход раепределителя связан с первым входом первого триггера, которого почк.тгочен к втором второго элелтента И, третий выход распределите.тя соелттнетт г первым входом ВТОРОГО э. ементя ИЛИ V втопым входом первого элемента ИЛИ, четвертый выход распреде.лителя соедипетт с втпрт,т в ото т блока сЬормт-фования кода, псовьиг входом третьего элемента И и , .холом пепрпго элемента ИЛИ, четвертый вход которого соелинен е вторым вхотом втологп э.тгд:онтэ ИЛГГ первым входом второго триггера н вторым управляюнтим входом Стройетпг вход второго триггера связан с выхо.дом третьего элемента И, второй вход которого подключе к третьему входу Стройетва,

2. УСТРОЙСТВО по п. I. отличающееся том. ггтп гЬоп.п рова-1Ия адреса содержит элементы РТЛИ и элементы И. причем выход кяутпгп .тгтя И.ТИ соелинен с первым входом олного элемента И. вторые входы элементов И o6berTr, и подключены к унравляютт емх- блока, пыходы которого соединены соответетвенно с выходами элементов IT, пчтт .--ОД Л- п-ого элемента ИЛИ со литготг с первым входом пятого элемента ИЛИ и с вторым входом блока, третий вход которого соедгптен с втопыми входами первого и :лгогс i.iex::;: ;ов и первым входом четвертого элемента ИЛИ, третий вход первого и первый вход третьего элементов ИЛИ соединены с четвертым входом блока, первый вход которого подключен к третьему входу пятого элемента ИЛИ, пятый вход блока со-5 единен с четвертыми входами первого и пятого и вторым входом третьего элементов ИЛИ, шестой вход блока связан с пятым входом первого, третьим входом третьего и вторым входом четвертого элементов ИЛИ, седь-Ю мой вход блока соединен с шестым входом первого, четвертым входом третьего, пятым входом пятого и третьим входом четвертого элементов ИЛИ, восьмой вход блока связан с седьмым входом первого и первым входом15 второго элементов ИЛИ, девятый вход блока соединен с восьмым входом первого, вторым входом второго и шестым входом пятого элементов ИЛИ, десятый вход блока связан с третьим входом второго и четвертым входом20 четвертого элементов ИЛИ. 3. Устройство по п. 1, отличающееся тем, что блок формирования кода содержит блок переключений, счетчик, триггер, четыре группы элементов И и элементы ИЛИ, причем 25 выход каждого элемента ИЛИ соединен с первым входом одного элемента И первой группы, выходы которых соединены соответственно с выходами блока, вторые входы элементов И первой группы подключены к первому 30 управляющему входу блока, первые входы элементов И второй группы соединены с первым выходом триггера, второй выход которого связан с первыми входами элементов И третьей группы, выходы которых соединены соответственно с входами блока иереключений, выходы элементов И второй группы соединены соответственно с первыми входами элементов ИЛИ. вторые входы которых соединены соответственно с выходами блока переключений, третьи входы элементов ИЛИ соединены соответственно с выходами элементов И четвертой групиы, первые входы которых соответственно соединены с выходами счетчика, вторые входы элементов И второй и третьей групп подключены к соответствующим входам блока, вторые входы элементов И четвертой группы соединены с выходом иоследнего элемента И третьей групиы и первым входом триггера, второй вход которого соединен с входом счетчика и вторым управляюидим входом блока. Р1сточники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР №445074, кл. G 06F 3/00, 1974. 2.Брусиловский К. А. Измерения искал ений импульсов в системах передачи дискретной информации. М.. «Наука, 1965.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для отображения информации | 1986 |

|

SU1319072A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Устройство для дистанционного управления топливораздаточными колонками | 1983 |

|

SU1117678A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Устройство для отображения графической информации | 1987 |

|

SU1474724A1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1981 |

|

SU1080196A1 |

| Устройство для сопряжения | 1983 |

|

SU1129603A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

Авторы

Даты

1978-02-28—Публикация

1975-12-22—Подача