1

Изобретение относится к вычислительной технике и может быть использовано в телеметрии и связи.

Известны буферные запоминающие устройства.

Одно из известных буферных запоминающих устройств содержит регистры, соединенные поразрядно, и элементы управления перезаписью по числу регистров 1.

Наиболее близким техническим решением к изобретению является буферное запоминающее устройство 2, которое содержит «-разрядный регистр, выполненный на / 5-триггерах, элементы управления на каждый разряд .регистра, шины записи, считывания.

К недостаткам такого устройства следует отнести иевысокую надежность и сложность его резервирования.

Цель изобретения - повыщение надежности устройства.

Это достигается тем, что буферное запоминающее устройство содержит для каждого разряда регистра восемь элементов И, элементы задержки и дополнительные ./ 5-триггеры, S-входами подключенные через первый и второй элементы И к элементам задержки и выходам S-триггеров регистра, входы каждого из которых соединены с щинами заииси и считывания, элементами задержки и выходами предыдущего разряда. Прямые выходы дополнительных 5-триггероз соединены соответственно с одними из входов четвертого и восьмого, третьего и седьмого элементов И и шинами записи, считывания, другие входы четвертого и седьмого элементов i-i подключены к входным щинам и элементам задержки, а выходы эле.менгов И каждого разряда - к шинам записи, считывания последующего разряда. Входы третьего и восьмого элементов И соедниены с выходными шинами устройства, инверсные выходы дополнительных / б-триггеров - с одними из входов пятого и шестого элементов И, другие входы которых иодключе 1Ы к одному из входов второго элемента И. Выходы третьего и пятого, шестого и восьмого элементов И каждого разряда подсоединены к соответствующпм входам третьего н восьмого элементов И последующего разряда, н выходным шннам, а выходы четвертого н седьмого элементов И /г-го разряда - к входным шинам.

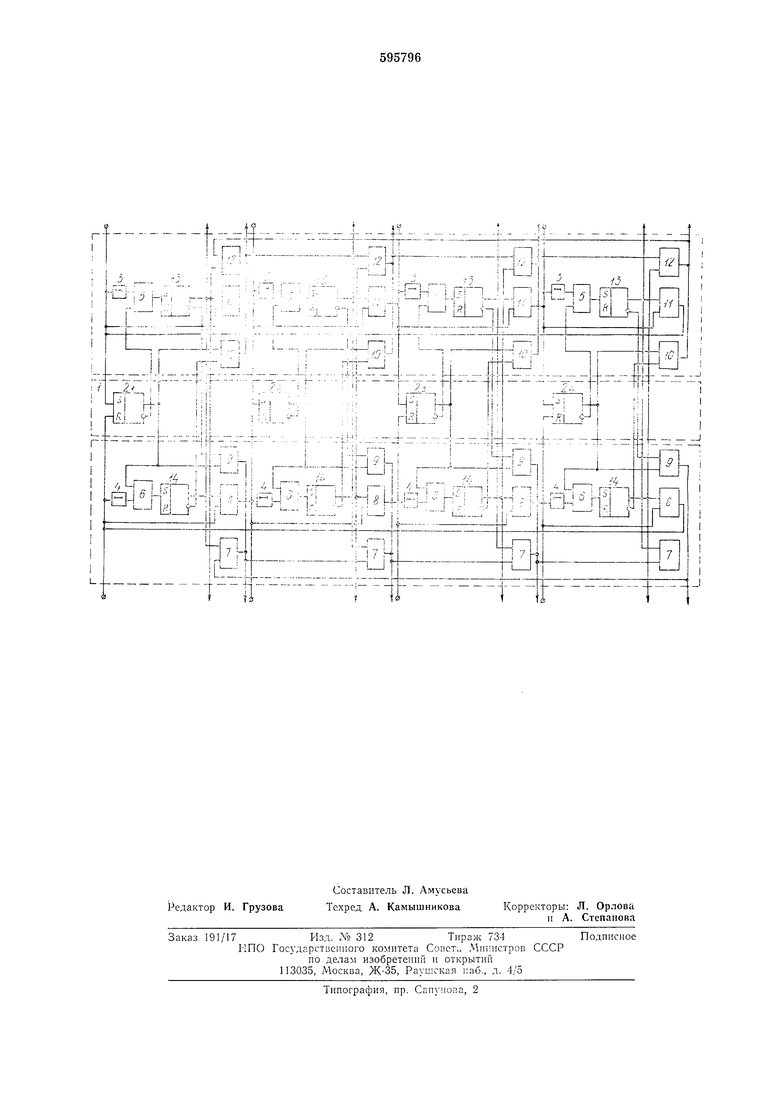

На чертеже нредставлена функпиональпая схе.ма буферного заномииающего устройства с самоконтролем.

Буферное заноминаюшее устройство содержит, например, четырехразрядный регистр 1, выполненный на S-триггерах 2i-24, элементы 3, 4 задерлчки, элементы И 5-12 и дополнительные / 5 триггеры 13, 14 для контроля заннси и считываиия информаппп.

В исходном состоянии S-триггеры 13 и 14 каждого разряда находятся в иулевом состоянии. Первый сигнал заииси поступает через входную шину на 5-вход / 5-триггера 2i.

Одновременно этот же снгнал через элемент 3 задержки нодается на элемент И 5, второй вход которого соединен е инверсным ВВ1ХОДОМ 7i;5-TpHrrepa 2i. Бели -/ 5-триггер 2) иснравлен и нод воздействием первого сигнала заниси перешел в единичное состояиие, то за счет воздействия низкого иотенц1шла инверсного выхода Л -триггера 2i элемент И 5 закрыт. Задержанный сигнал на 5-вход j S-TpHrrepa 13 не проходит. В исходном иоложенин элемент И 10 открыт воздействием потенциала инверсного выхода У 6-трнггера 14, а элемент И 12 закрыт воздействием нотенциала нрямого ввьхода этого же триггера. В еоответстшп; с этим нотеициал с нрямого / б-трн тера 2i иодается иа вход элемента И 10, следующий еигнал заииси ио входной илие следующего разряда иоступает на S-вход / 5-триггера 22. Если 6-триггер 2-2 ие исиравеи, т. е. не переходит в единичное еостояние, то отсутствии элементов И , элемеита -i задержки, дополнительного У 5-трнггера 11, буферное запо1мпнающее уетройетво выходит из строя, так как иодача очередного сигнала на / 5-трнггер 2з второго разряда возможна лнщь тогда, когда У Л-тричер 2-2 г.аходнтся в сд1И-1ичном состоянии.

Второй сигнал записи во 2-.i разряде региетра 1 через элемент 3 задержки попадает на вход элемента И 5, который открыт за счет потеиииала, поступающего с инверсного выхода jRS-трнггера 22, ие иерещедщего в единичное состояиие под воздействием второго сигнала занисн, н иодается иа его выход. Этим сигналом 5-триггер 13 2-го разряда иеобратимо перебрасывается в единичиое состояние и открывает элемеит И И этого же разряда.

Одновременно воздействием 5-триггера 13 закрывается элемент И 9 и открывается элемент И 7. Таким образом, процессом считывания ниформаини с / 5-трнггера 2з управляет не неисправный S-трпггер 22, а исправный / 5-тритгер 2i.

Третий сигиал заииси в 3-Л1 разряде регистра 1 через открытый элемент И И предыдущего разряда иостунает на 5-вход / 5-триггера 2з и перебрасывает, его в единичное состояиие.

Четвертый еигнал заниси во 2-м разряде регистра 1 нодаетея иа 5-вход 5-трпггера 2.

Работа схемы контроля считываиия происходит аналогнчно. В нроиессе считывания используются элемент 4 задержки, элементы И b-9 и донолиителвлый /.S-триггер 14 каждого разряда.

Восетановленпе работоенособности устройства нрн ввиходе из строя одного двоичного элемента дост Иаетея ценой потери только одной единственной выборки как при записи, 1ак и ири считывании.

Ф о j) м л а и 3 о б р е т е и и я

Буферное заио мннающее устройство с самоконтролем, содержащее л-разрядный регнстр, вынолненный на У 5-триггерах, щины заннеи, c ;нть вaния, входные и выходные гиины, о т л п ч а ю Hj, е е с я тем, что с целью новынюния надежности устройства, оно содерЖ1Г1 для каждого )азряда регистра восемь эле.ментов И, элеме1гты задержки и дополнительные / 6-тр1итеры, S-входы которых через первый н второй элемеиты И подключены к элемента.м задержки и выходам 5-триггероз регистра, входы каждого из которых соединены с щинамн заниси и считывания, элементами задержки и выходами иредыдущего разряда, ирямые выходы донолиительных У 6-триггеров соедииены соогветственно с одними из входов четвертого и восьмого, третьего и седьмого элемеишв И и шинами заниси, счнть1ваиия, другие ВХОДВ1 чегеертого и седьмого элементов И подключены к входным шинам и элементам задержки, а выходы элементов И каждого разряда подключены к шинам заиисн, считывания носл(;дующего разряда, входы третьего н восьмого элементов И соединеиы с выходными шинами устройства, ииверсные выходы дополнительных / б-триггеров соединены с одними из входов иятого и шестого элемеитов li, другие входы которых подключены к одному из входов второго элемента И, выходы третьего и пятого, шестого и восьмого элементов И каждого разряда подключены к соответствуюнщм входам третьего и восьмого элементов И носледующего разряда п выходным шинам, а выходы четвертого и седьмого элементов И п-го разряда подключены к входным шинам.

Источиики ииформации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР Аз 375681, кл. G ПС 9/02, опублик. 06.08.70.

2.Патент Великобритании .Чз 1387882, кл. G ПС 19/00, опублик.20.04.72.

::15

tli

4::...:-:-::..:.,:...j...

Г

f

L

IT iV L

Г

,-: U

11

f

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное устройство для сбора и обработки информации | 1976 |

|

SU595725A1 |

| Счетчик на кольцевом регистре | 1978 |

|

SU733111A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЕСТ ПОВРЕЖДЕНИЯ НАПОРНОГО ТРУБОПРОВОДА | 1992 |

|

RU2046251C1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| МНОГОФУНКЦИОНАЛЬНАЯ ЛОГИЧЕСКАЯ СХЕМА В ИНТЕГРАЛЬНОМ ИСПОЛНЕНИИ | 1969 |

|

SU236530A1 |

| Многофункциональный регистр | 1986 |

|

SU1411828A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ ЦИФРОВОЙ ИНФОРМАЦИИ НА МАГНИТНЫЙ НОСИТЕЛЬ | 1970 |

|

SU264462A1 |

| Устройство для ввода информации | 1988 |

|

SU1667121A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

:- LJ Ul i: 7i-tf , .,..±: fe

Авторы

Даты

1978-02-28—Публикация

1976-11-09—Подача