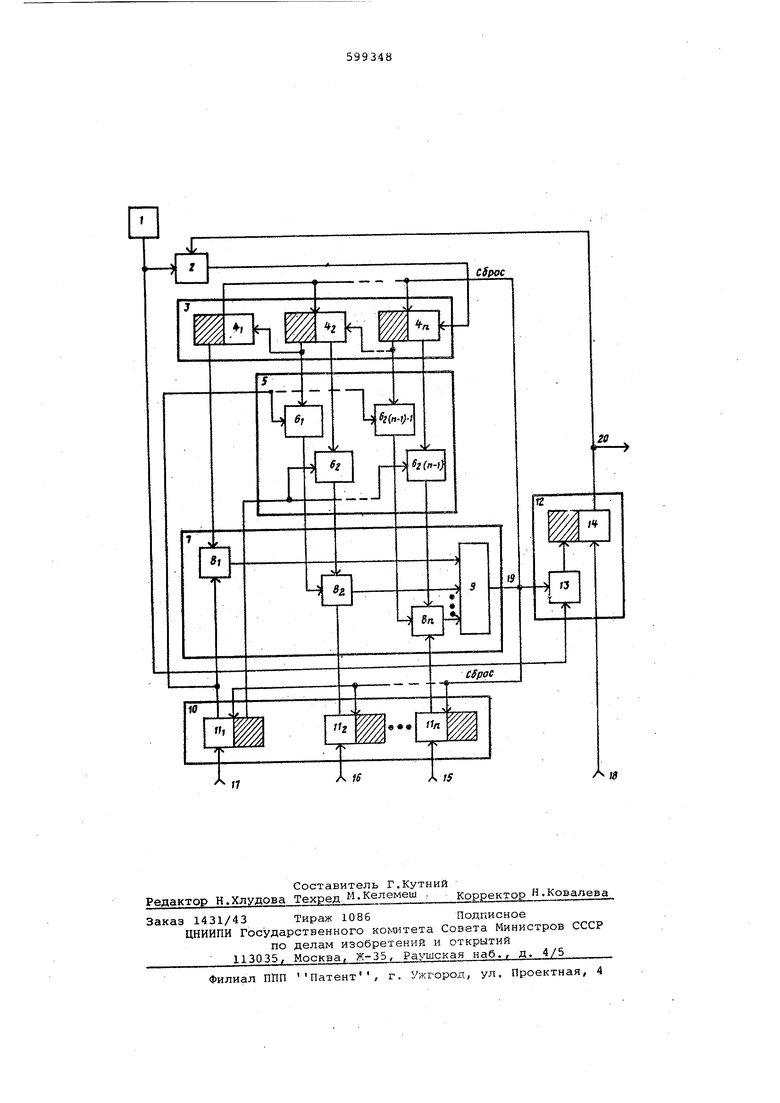

ная схема оредлагаемого преобразонателя Сигналов ИКМ в сигналы ШИМ.

Преобразователь состоит из генератора 1 тактовых импульсов, двухвходового элемента И 2, двоичного счетчика 3, образованного триггерами 4, 42 f.-. узла вентилей 5, состоящего из двухвходовых элементов И 6, б2/ .. Sg (п-1) ; цифрового блока 7 сравнения, содержащего двухвходовой элемент ИЛИ 8 , трехвходовые элементы ИЛИ Sg, р., 8.„ входовых элементов И 9; регистра 10 памяти кода, образованного триггерами 11, 11g ... формирователя 12 .выходного сигнала, содержащего двухвходовой элемент И 13 и триггер 14 с раздельным запуском; шины 15 входа Лз -го (младшего) разряда кода, шины 16 входа втс рого разряда кода, шины 17 входа первого (старшего) знакового разряда кода, шины 18 входа импульса синхронизации по кодовым словам, шины 19 импульса равенства кодовых комбинаций, шины 20 выхода сиг налов ШИМ (выхода преобразователя),

Устройство работает следующим образом.

Импульс синхронизации по кодовым словам поступает на первый вход .(шина 18) триггера 14 и запускает его.

Выходной сигнал триггера 14 поступает на первый вход элемента И 2, разрешая поступление импульсов с генератора I на счетчик 3, который начинает подсчет тактовых импульсов.

Прямые и инверсные выходы счетчика 3 подключены к узлу вентилей 5, управление которыг- осуществляется знаKOBHivi (старшим) разрядом регистра 10 памяти кода с триггера значении старшего разряда кода откроются элементы И 6 , 6, ... 2() подключенные к инверсным выходам счетчика 3.

При значении старшего разряда кода О откроются элементы И 6, б,... 2( подключенные к прямым выводам счетчика 3.

Этим осуществляется преобразование бинарного симметрического кода в бинарный. Цифровой блок 7 сравнения объединяет на элементах ИЛИ 8.|, В..8f сигналы с узла 5 вентилей и реги-стра 10 памяти кода.

На вьлходе элемента 9 И вырабатывается сигнал равенства кодов, который по шине 19 подается на элемент И 13 формирователя 12 выходного сигнала, стробируется там совпадающим тактовым импульсом.

Импульс с выхода элемента И 13 срывает работу триггера 14 и устанавливает в состояние О счетчик 3 и регистр 10 памяти кода.

На выходе формирователя 12 вырабатыв.ается импульс, длительность котоpojio пропорциональна значению кодовой комбинации. По шине 20 он подается на выход.

Формула изобретения

Преобразователь сигналов импульсно-кодовой модуляции в сигналы широтно-импульсной модуляции, содержащий регистр Памяти кода, выходы которого соединены с первыми входами цифрового блока сравнения, выход которого соединен с первым входом формирователя выходного сигнала, генератор тактовых импульсов, выход которого соединен с вторым входом формирователя выходного сигнала и первым входом элемента И, второй вход которЪто соединен с выходом формирователявыходного сигнала, а выход соединен с входом двоичного счетчика, отличающийс я , тем, что, с целью обеспечения возможности преобразования симметричного бинарного кода, в него дополнительно введены 2(,., элементов И, где ; и - число разрядов преобразуемого кода, первые входы нечетных дополнительных элементов И соединены с не инверсными выходами соответствующих разрядов двоичного счетчика, вторые входы - с инверсным выходом триггера первого разряда регистра памяти кода, первые входы четных дополнительных элементов И соединены с инверсными выходами соответствующих разрядов двоичного счетчика, вторые входы - с неинверсным выходом триггера первох о разряда регистра памяти кода.

Источники информации, принятые во внимание при экспертизе:

1. Гитис Э.И. Преобразователи информации для электронных цифровых вычислительных устройств. М., Энергия 1975, с.267-273, рис. 6-96.

11

AW

ts

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

| Цифровое измерительное устройство для обработки сигналов частотных датчиков | 1989 |

|

SU1659891A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2234191C2 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| Формирователь импульсных последовательностей | 1988 |

|

SU1539973A1 |

| Групповой приемник сигналов управления и взаимодействия с адаптивной дифференциальной импульсно-кодовой модуляцией | 1991 |

|

SU1829126A1 |

| Устройство для квантования в установках с импульсно-кодовой модуляцией | 1977 |

|

SU733099A1 |

Авторы

Даты

1978-03-25—Публикация

1977-01-20—Подача