1

Изобретение относится к вычислительной технике и может быть использовано в смете-, мах автоматики и телемеханики.

Известны счетные устройства, сохраняющие информацию при перерывах питания, содержащие триггеры, элементы памяти, генератор одипочных импульсов, причем выход генератора одиночных импульсов подключен к одному из установочных входов триггеров, а выход элементов памяти подключен к второму установочному входу триггеров 1.

Однако общим недостатком известных устройств является то, что запись информации в элементы памяти выполняется по специальному сигналу, который поступает из внешних устройств управления.

При этом существует вероятность потери информации в случае выключения питания до прихода спгнала записи из впешнего устройства управления.

Наиболее близким по технической сущности к изобретению является счетное устройство, содержапдее две линии задержки, триггеры, соединенные последовательно, схемы запрета, элементы памяти и генератор одиночных импульсов, выход которого подключеи к одному из установочных входов триггеров и через линию задержки - к входам считывания элементов памяти 2.

Основным недостатком счетного устройства

является то, что запись информации в элементы памяти выполняется по сигналу окончания счета, при этом существует вероятность потери информации в случае выключения Н1 тання до окончания процесса счета. Кроме того, реальна возможность повторного выключения питания до начала очередного цикла счета, при этом информация, заппсанная в триггерах счетчика не будет перезаписана в элементы памяти, а разрушится.

Целью 11300ретения является повышение надежности работы устройства. При этом возможно расширение области применения устройства.

Это достигается тем, что в уетройство, содержащее две линии задержки, триггеры, соединенные носледовательно схемы запрета, элементы памяти ii генератор одиночных импульсов, выход которого подключен к одному из установочных входов триггеров и через линию задержки - к входам считывания элементов памяти, введены блок разделения цепей регенерации, блоки разрешения записи информации в элементы памяти и блоки разрешения стирания информации в элементах памяти, причем сигнальные входы блоков разрешения записи информации подключены к прямым выходам триггеров, П1версные выходы которых подключены к сигнальным входам блоков разрешения стирания информации в элемеитах памяти, а управляющие входы блоков разрешения записи ииформацпи в элемеиты памяти и Олоков разрешеиия стираиия ипфорЛ1ации в элемеитах памяти через две иоследовательно включенные лииии задержки подключены к геиератору одииочных имиульсов, а также через олок разделения цепей регенерации подключены к счетному входу устройства, при этом выходы блоков разрешедия заипси и ОЛОКОБ разрешения стирания ипформацип в элементах памяти подключены соответственно к входам записи и входам стпраиия элементов памятп, выходы которых подключены к сигнальным входам схем запрета, причем управляющие входы схем запрета через линию задержки подключены к генератору одиночных импульсов, а выходы Схем запрета нодключеиы к вторым установочным входам триггеров.

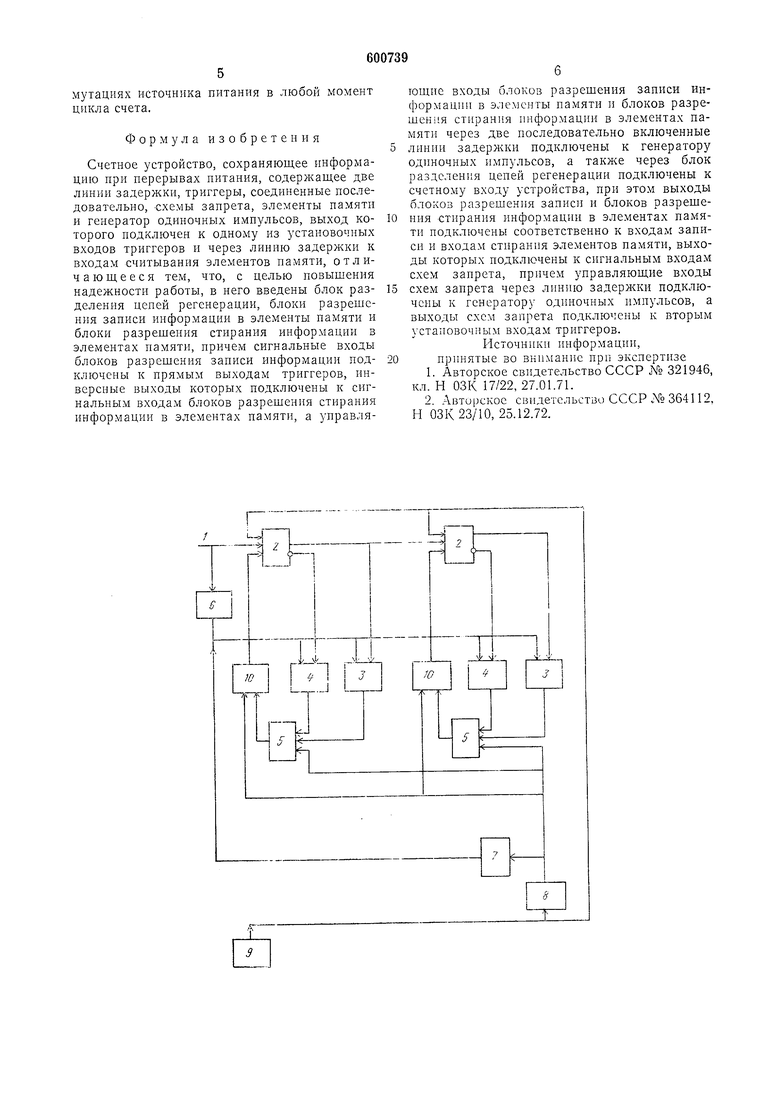

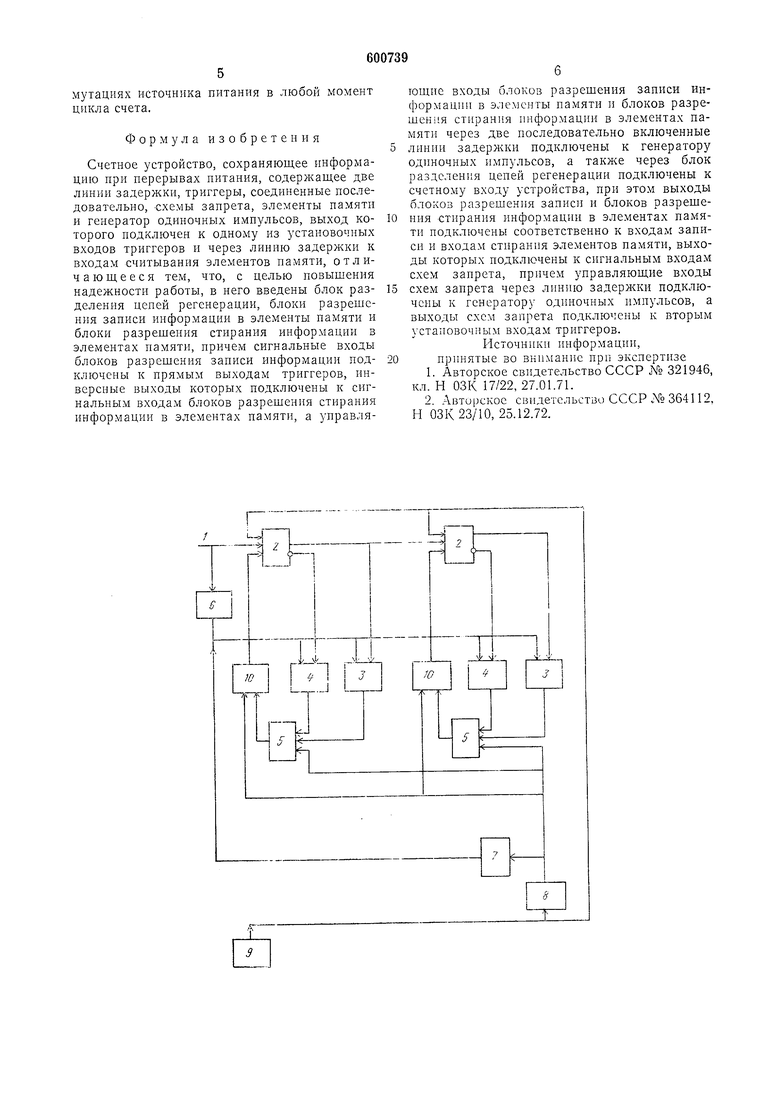

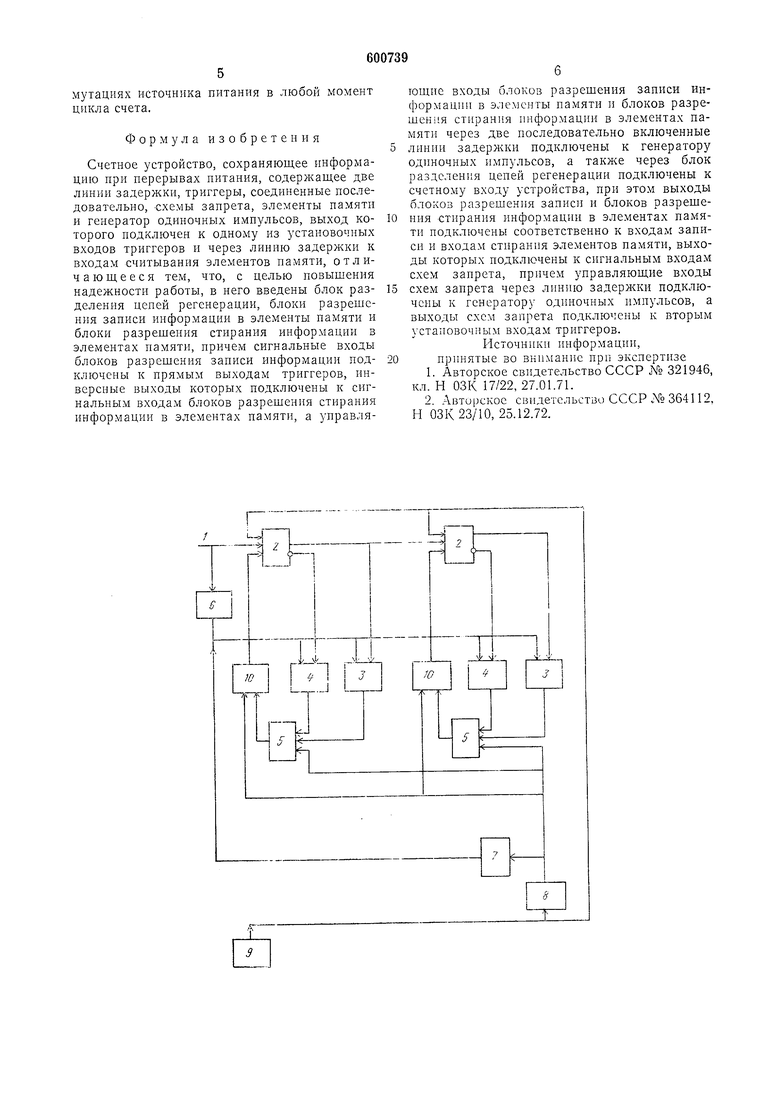

На чертеже иоказаиа блок-схема устройства.

Счетиый вход 1 устройства подключен к триггеру 2 счетчика, при этом прямые выходы триггеров 2 подключены к сигнальным входам блоков о разрешения записи информации, а инверспые выходы триггеров 2 подключены к сигнальным входам блоков 4 разрешеиия стирания информации. При этом выходы блоков 3 разрешепия записи подключены к входам записи элементов 5 памяти, а выходы блоков 4 разрешения стирания подключены к входам стирания элементов 5 памяти. Управляющие входы блоков 3 разрешения записи и блоков 4 разрешения стирания информации подключены через блок б разделения цепей регенерации к счетному входу 1 устройства, а также через последовательно включенные лииии 7 и 8 задержки подключены к генератору У одиночных импульсов.

Генератор 9 подключен также к устаиовочиым входам триггеров 2 и через линию 8 задержки- к входам считываппя элемептов 5 памяти.

Кроме того, генератор 9 через линию 8 задержки подключен к управляющим входам схем 10 заирета, сигнальные входы которых подключены к выходам элемептов 5 памяти. При этом выходы схем 10 запрета подключены к вторым установочным входам триггеров 2.

Устройство работает следующим образом. На его счетный вход 1 поступают импульсы определеииой (иоложительпой) полярпости, количество которых считается триггерами 2, при этом в данный момент времеии каледый триггер 2 находится в состоянии «О либо «1, т. е. па его парафазпых выходах присутствует определенная комбинация уровней выходного сигиала. Если триггер 2 находится в состоянии «1, то на его прямом выходе высокий уровень напряжения (условно принятый за логическую «1), при этом соответствующий блок разрешения записи включается и выполняет запись «1 в элемент 5 памяти, так как на его управляющий вход через блок 6 разделенпя цепей регенерации поступает импульс также положительной полярности со счетного входа 1 устройства.

При этом блок 4 разрешеиия стирания соответствующего разряда счетчика выключен, так как на его управляющем и сигнальном входах присутствует различпая по уровпям комбинация сигналов.

Если триггер 2 данного разряда счетчика переключен в состояние «О счетным импульсом, то на сигиальном входе блока 4 данного разряда счетчика иоявляется потенциал «1, а иа управляющем - импульс положительной полярности. 11ри этом блок 4 стирания даииого разряда включается и выполияет запись «и в элемент 5 иамяти данного разряда счетчика.

Аналогично работают все разряды счетного устройства.

Если в какой-то момеит времени отключается иитание устройства, а затем включается, то ири появлении питания срабатывает генератор 9 одииочиых импульсов. Импульс с выхода геператора 9 устанавливает все триггеры 2 счетчика в состояпие «О и через время, определяемое линией 8 задержки, выполияет считывание информации, записанной ранее в элемеитах 5 памяти. Кроме того, импульс с выхода генератора 9 поступает также на управляющий входы схем 10 запрета. При этом схемы 1U запрета тех разрядов счетчика, в элементах 5 памяти которых была ранее записана «1, открываются в результате воздействия па оба входа одиополяриых импульсов, перекрывающихся во времеии. Открывапие схем 10 запрета вызывает устаиовку соответствующих триггеров 2 в полон ;ение логической «1, т. е. пиформация, заиисанная до отключения питания в триггерах счетчика, восстанавливается.

Далее выходиой импульс геиератора 9 через иромел уток времени, определяемый линией 7 задерлски, поступает на управляющие входы блоков 3 записи и блоков 4 стираиия информации. При этом в элементы 5 памяти тех разрядов счетчика, триггера 2 которых переключаются в состояние «1, записывается «1 - аиалогичио процесеу записи, происходящему в режиме счета и описанному выше.

Для того, чтобы в процессе восстановления информации в элементах 5 иамяти не выполнялся ложный сдвиг счетчика на «+1, введен блок 6 разделения цепей регенерации. Дальнейшая работа устройства выполняется в режиме счета.

При экспериментальной проверке работоспособности предлагаемого устройства логическая часть была полиостью выполнена на интегральных микросхемах широкого применения, а в качестве элементов памяти были исиользованы запомпиающие трансформаторы на ферритовых тороидальных сердечниках.

Предлагаемым счетным устройством обеспечивается надельная работа прп частых коммутациях источника питания в любой момент цикла счета.

Формула изобретения

Счетное устройство, сохраняющее информацию при перерывах питания, содержащее две линии задержки, триггеры, соединенные последовательно, схемы запрета, элементы памяти и генератор одиночных импульсов, выход которого подключен к одному из установочных входов триггеров и через линию задержки к входам считывания элементов памяти, отличающееся тем, что, с целью повыщения надежности работы, в него введены блок разделения цепей регенерации, блоки разрешения записи информации в элементы памяти и блоки разрешения стирания информации в элементах памяти, причем сигнальные входы блоков разрешения записи информации подключены к прямым выходам триггеров, инверсные выходы которых подключены к сигнальным входам блоков разрешения стирания информации в элементах памяти, а управляющие входы блоков разрешения записи информации в элементы памяти и блоков разрешен я стирания информации в элементах памятн через две последовательно включенные

линии задернски подключены к генератору одиночных импульсов, а таклче через блок разделения цепей регенерации подключены к счетному входу устройства, при этом выходы блокоз разрешения записи и блоков разрешеиия стирания информации в элементах памяти подключены соответственно к входа1М записи и входам стирания элементов памяти, выходы которых подключены к сигнальным входам схем запрета, причем управляющие входы

схем запрета через линию задержки подключены к генератору одиночных импульсов, а выходы схем запрета подключены к вторым установочным входам триггеров.

Источнпки информации,

нринятые во внимание при экспертизе

1.Авторское свидетельство СССР № 321946, кл. Н ОЗК 17/22, 27.01.71.

2.Автирское свидетельство СССР № 364112. Н ОЗК 23/10, 25.12.72.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО КОДИРОВАНИЯ | 1972 |

|

SU354409A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Счетное устройство,сохраняющее информацию при отключении питания | 1980 |

|

SU946001A1 |

| Устройство для контроля многоканального аппарата магнитной записи | 1986 |

|

SU1420615A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| Устройство для ввода информации | 1982 |

|

SU1089566A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Счетное устройство,сохраняющее информацию при отключении питания | 1981 |

|

SU1010731A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

Авторы

Даты

1978-03-30—Публикация

1975-12-10—Подача