Изобретение относится к области автоматики и вычислительной техники, прядназначено для формирования суммы и разности квадратов двух величин, представленных в цифровой или аналоговой форме, и является усовершенствованием квадратора по авт.св. № 1180885.

Цель изобретения заключается в расширении функциональных возможностей путем формирования суммы и разности квадратов двух величин.

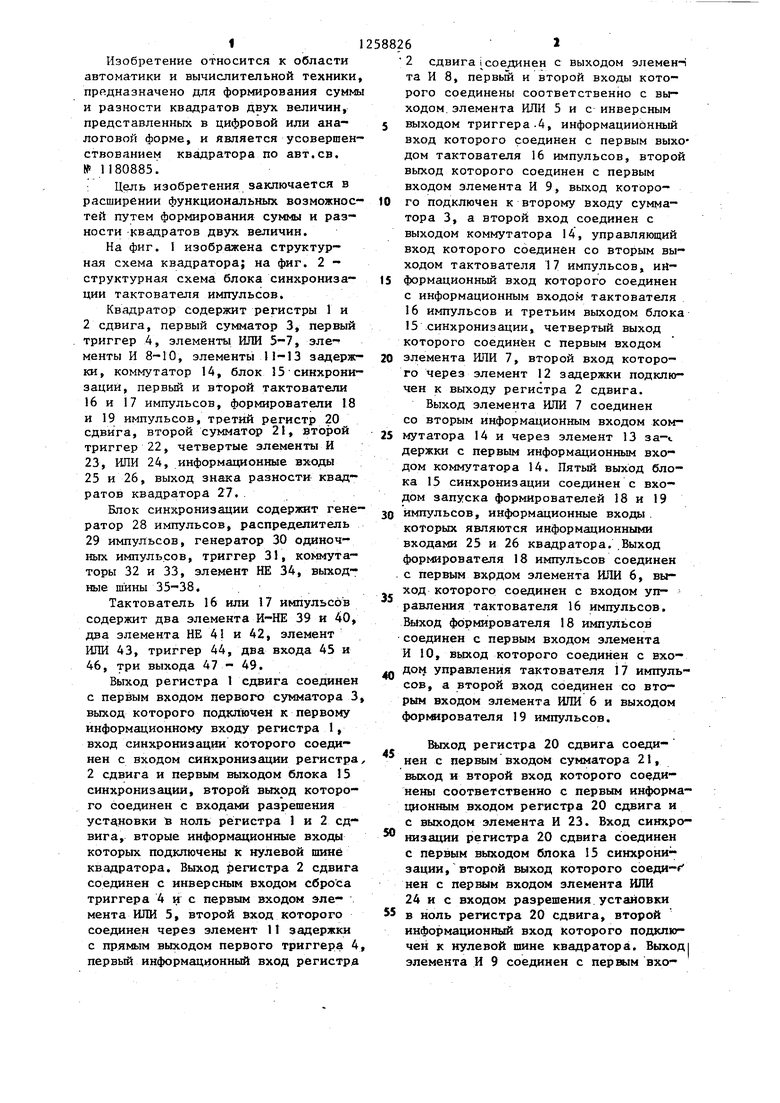

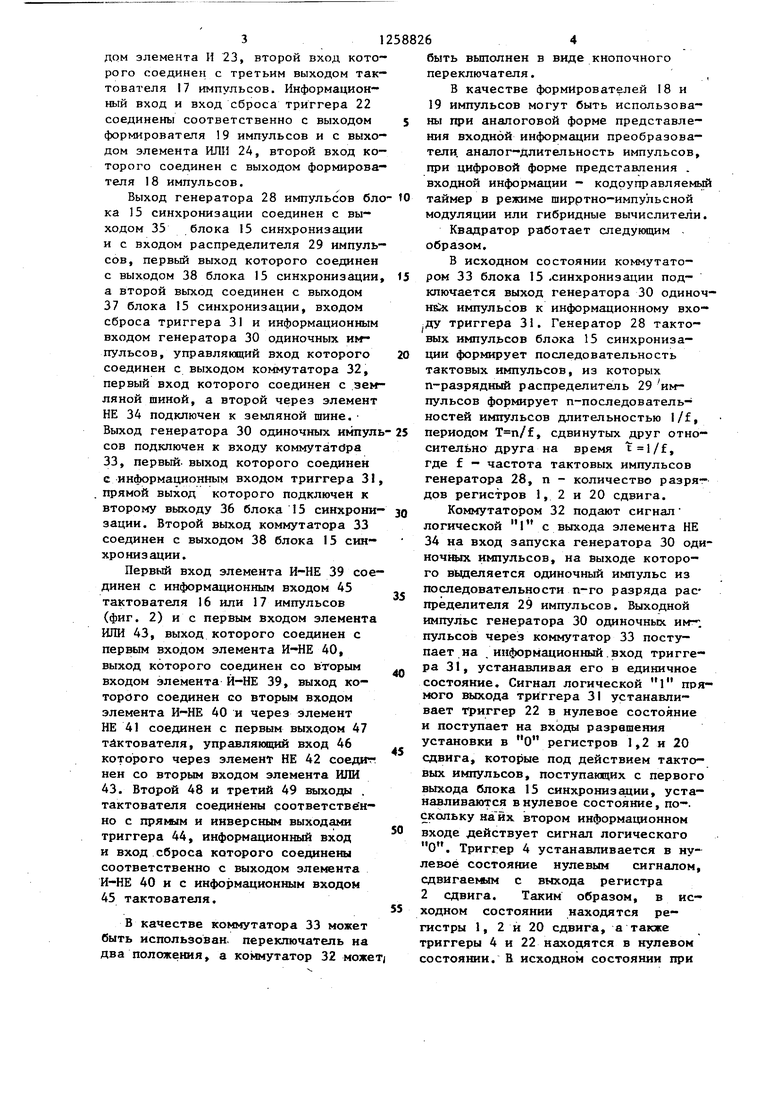

На фиг. 1 изображена структурная схема квадратора; на фиг. 2 - структурная схема блока синхронизации тактователя импульсов.

Квадратор содержит регистры 1 и 2 сдвига, первый сумматор 3, первый триггер 4, элементы ИЛИ 5-7, эле- менты И 8-10, элементы 11-13 задержки, коммутатор 14, блок 15 синхронн- заций, первый и второй тактователи 16 и 17 импульсов, формирователи 18 и 19 импульсов, третий регистр 20 сдвига, второй сумматор 2, второй триггер 22, четвертые элементы И 23, ИЛИ 24, информационные входы 25 и 26, выход знака разности квадратов квадратора 27..

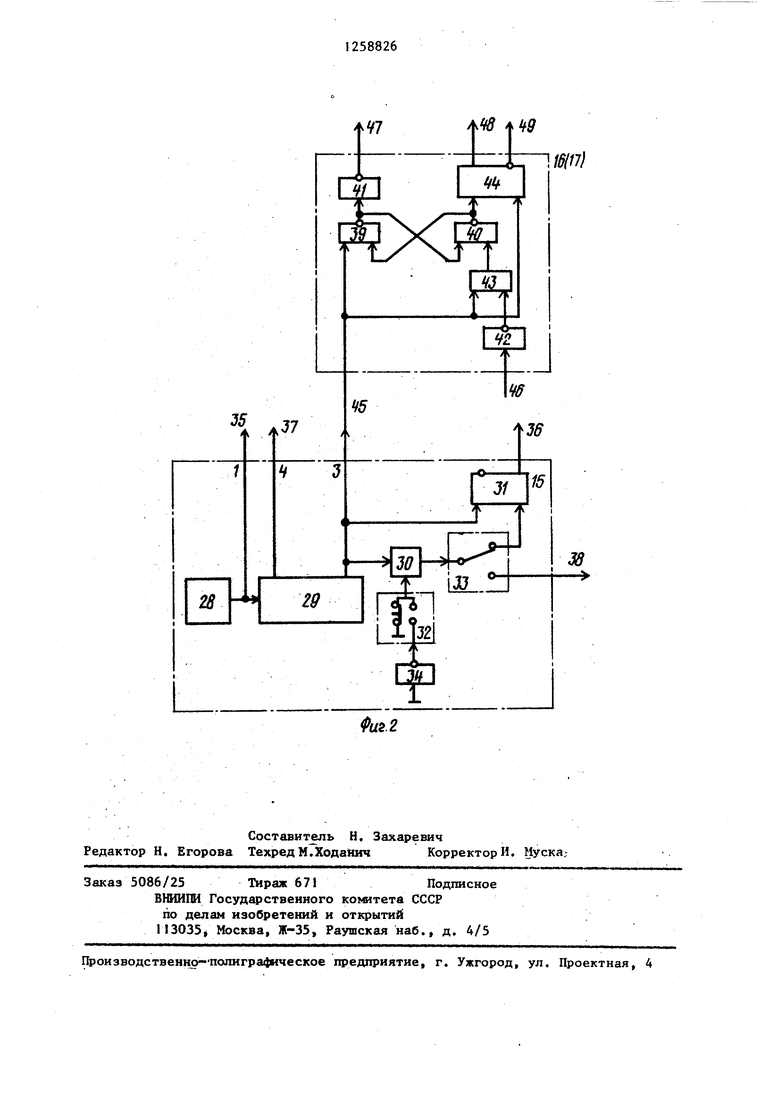

Блок синхронизации содержит генератор 28 импульсов, распределитель 29 импульсов, генератор 30 одиночных импульсов, триггер 31, коммутаторы 32 и 33, элемент НЕ 34, выходные шины 35-38.

Тактователь 16 или 17 импульсов содержит два элемента И-НЕ 39 и 40, два элемента НЕ 4 и 42, элемент ИЛИ 43, триггер 44, два входа 45 и 46, три выхода 47 - 49.

Выход регистра 1 сдвига соединен с первым входом первого сумматора 3 выход которого подключен к первому информационному входу регистра 1 вход синхронизации которого соединен с входом синхронизации регистра 2 сдвига и первым выходом блока 15 синхронизации, второй выход которого соединен с входами разрешения установки ь ноль регистра 1 и 2 сд вига, вторые информах онные входы которых подключены к нулевой шине квадратора. Выход регистра 2 сдвига соединен с инверсным входом сброса триггера 4 и с первым входом элемента ИЛИ 5, второй вход которого соединен через элемент 11 задержки с прямым выходом первого триггера 4 первый информационный вход регистра

2 сдвига(соединен с выходом элеменН та И 8, первьй и второй входы которого соединены соответственно с выходом, элемента ИЛИ 5 и с инверсным

выходом триггера.4, информациионный вход которого соединен с первым выходом тактователя 16 импульсов, второй выход которого соединен с первым входом элемента И 9, вькод которого подключен к второму входу сумматора 3, а второй вход соединен с выходом коммутатора 14, управляющий вход которого соединен со вторым выходом тактователя 17 импульсов, информационный вход которого соединен с информационным входом тактователя 16 импульсов и третьим выходом блока 15 синхронизации, четвертый выход которого соединён с первым входом

элемента ИЛИ 7, второй вход которого через элемент 12 задержки подключен к выходу регистра 2 сдвига.

Выход элемента ИЛИ 7 соединен со вторым информационным входом ком-

мутатора 14 и через элемент 13 за-«. держки с первым информационным входом коммутатора 14. Пятый выход блока 15 синхронизации соединен с входом запуска формирователей 18 и 19

импульсов, информационные входы которых являются информационными входами 25 и 26 квадратора. .Выход формирователя 18 импульсов соединен с первым вхрдом элемента ИЛИ 6, выход которого соединен с входом управления тактователя 16 импульсов. Выход формирователя 18 импульсов соединен с первым входом элемента И 10, выход которого соединен с входом управления тактователя i 7 импульсов, а второй вход соединен со вторым входом элемента ШШ 6 и выходом формирователя 19 импульсов.

алход регистра 20 сдвига соединен с первым входом сумматора 21, выход и второй вход которого соединены соответственно с первым информа- ционшлм входом регистра 20 сдвига и с выходом элемента И 23. Вход синхрониэации регистра 20 сдвига соединен с первым выходом блока 15 синхронизации, второй шлход которого соеди-f нен с первым входом элемента ШШ 24 и с входом разрешения установки

в ноль регистра 20 сдвига, второй информационный вход Которого подключен к нулевой шине квадратора. Выход элемента И 9 соединен с вхо

дом элемента И 23, второй вход которого соединен с третьим выходом так- тователя 17 импульсов. Информационный вход и вход сброса триггера 22 соединены соответственно с выходом формирователя 19 импульсов и с выходом элемента ИЛИ 24, второй вход которого соединен с выходом формирователя 18 импульсов.

Выход генератора 28 импульсов блока 15 синхронизации соединен с выходом 35 блока 13 синхронизации и с входом распределителя 29 импульсов, первый выход которого соединен с выходом 38 блока 15 синхронизации, а второй выход соединен с выходом 37 блока 15 синхронизации, входом сброса триггера 31 и информационным входом генератора 30 одиночных импульсов, управляющий вход которого соединен с выходом коммутатора 32, первый вход которого соединен с .земляной шиной, а второй через элемент НЕ 34 подключен к земляной шине. Выход генератора 30 одиночных Hfhiynb сов подключен к входу коммутатЬра 33, первый- выход которого соединен с информационным входом триггера 31, прямой выход которого подключен к второму выходу 36 блока 15 синхронизации. Второй выход коммутатора 33 соединен с выходом 38 блока I5 синхронизации.

Первый вход элемента И-НЕ 39 соединен с информационным входом 45 тактователя 16 или 17 импульсов (фиг. 2) и с первым входом элемента ШШ 43, выход которого соединен с первым входом элемента И-НЕ 40, выход которого соединен со ь торым входом элемента Й-НЕ 39, выход которого соединен со вторым входом элемента И-НЕ 40 и через элемент НЕ 41 соединен с первым выходом 47 тйктователя, управляющий вход 46 которого через элемент НЕ 42 соедитг ней со вторым входом элемента ШШ 43. Второй 48 и третий 49 выходы . тактователя соединены соответстве н- но с прямым и инверсным выходами триггера 44, информационный вход и вход сброса которого соединены соответственно с выходом элемента И-НЕ 40 и с информационным входом 45 тактователя.

В качестве коммутатора 33 может быть использован, переключатель на два положения, а коммутатор 32 может

быть вьшолнен в виде кнопочного переключателя.,

В качестве формирователей 18 и 19 импульсов могут быть использова- 5 ны при аналоговой форме представления входной информации преобразователи, аналог-длительность импульсов, при цифровой форме представления . входной информации - кодоуправляемьй

o таймер в режиме ширртно-импульсной модуляции или гибридные вычислители.

Квадратор работает следующим образом.

В исходном состоянии коммутато5 ром 33 блока 15 .синхронизации подключается выход генератора 30 одиноч- HBix импульсов к информационному вхо- :ДУ триггера 31. Генератор 28 тактовых импульсов блока 15 синхрониза0 ции формирует последовательность тактовых импульсов, из которых п-разрядный распределитель 29 импульсов формирует п-последователь- ностей импульсов длительностью l/f,

5 периодом , сдвинутых друг относительно друга на время , где f - частота тактовых импульсов геиератора 28, п - количество разрядов регистров 1, 2 и 20 сдвига.

0 Коммутатором 32 подают сигнал логической 1 с выхода элемента НЕ 34 на вход запуска генератора 30 оди- ночщлх импульсов, на выходе которого вьвделяется одиночный импульс из последовательности п-го разряда распределителя 29 импульсов. Выходной импульс генератора 30 одиночных икг-: пульсов через коммутатор 33 поступает на . информационный.вход триггера 31, устанавливая его в единичное состояние. Сигнал логической 1 прямого выхода триггера 31 устаиавли- вает триггер 22 в нулевое состояние и поступает на входы разрешения установки в О регистров 1,2 и 20 сдвига, которые под действием тактовых импульсов, поступающих с первого выхода блока 15 синхронизации, устанавливаются в нулевое состояние, по-, скольку на йх втором информационном

входе действует сигнал логического О. Триггер 4 устанавливается в нулевое состояние нулевым сигналом, сдвигаемым с выхода регистра 2 сдвига. Таким образом, в ис5 ходном состоянии находятся регистры 1, 2 и 20 сдвига, а также триггеры 4 и 22 находятся в нулевом состоянии. R исходном состоянии при

5

0

5

нулевом сигнале на входе управления коммутатор 14 подключает выход элемента ИЛИ 7 ко второму входу элемента И 9.

Режим вычислений устанавливается коммутатором 33 путем подключения выхода генератора 30 одиночных импульсов к входам запуска формирователей 18 и 19 импульсов. Вычисления в квадраторе начинаются после запуска с помощью коммутатора 32 генератора 30 одиночных импульсов, выходной импульс которого запускает формирователи 18 и 19 импульсов.

На выходах формирователей 18 и 1 импульсов формируются импульсы, длительность которых пропорциональна сигналам (аналоговым или цифровым), действующим на информационных входах 25 и 26 устройства.

Если длительность выходных импульсов формирователей 18 и 19 импу сов различна, то наибольший по длительности импульс выделяется на выходе элемента ИЛИ 6, а импульс меньшей длительности - на выходе элмента И 10, под действием которого тактователь i 7 импульсов формирует из последовательности импульсов п-го разряда распределителя 29 импульсов строб-пачки импульсов, количество которых пропорционально наименьшей величине, действующей на одном из информационных входов 25 или 26 устройства. Строб тактовате- ля 17 импульсов переключает коммутатор 14 в состояние, в котором выход элемента 13 задержки подключается ко второму входу элемента И 9. Под действием наибольшего пульса выхода элемента ИЛИ 6 и послдовательности импульсов п-го разряда распределителя 29 импульсов тактователь 56 импульсов формирует на втором выходе строб-пачки импульсов а на первом выходе - пачку импульсо количество которых пропорционально наибольшей величине, действующей на одном из информационных входов 25 или 26 устройства. Строб второго выхода тактователя 16 импульсов открывает элеме(нт И 9, а пачка импульсов с первого выхода тактователя 16 импульсов поступает на информационный вход триггера 4.

Первый импульс пачки устанавливает в единичное состояние триггер 4 в п-ом такте (соответствующем сдвигу п-х разрядов кодов с выходов регистров 1, 2 и 20 сдвига) . Установка триггера 4 в единичное состояние приводит к формирова- нию на его инверсном выходе нулевого сигнала, блокирующего элемент И8, а на прямом выходе - единичного сигнала, который, спустя время задержки элементом 1I задержки на такт,

начнет действовать через элемент ИЛИ 5 на первом входе элемента И 8. Под действием тактовых импульсов первого выхода блока 15 синхронизации с выхода регистра 2 сдвига в

первом такте сдвигается младший разряд начального нулевого кода, сигнал которого поступает на инверсный вход сброса триггера 4 и уста- навлипает его в нулевое состояние.

Q нулевом состоянии на инверсном

выходе триггера 4 формируется единичный сигнал, которьш снимает блокировку элемента И 8. Благодаря задержке элементом 11 задержки на такт сиг-

нала прямого выхода триггера 4, на выходе элемента И 8 формируется импульсный сигнал, которьш в первом такте записывается в качестве млад- .шего разряда кода в регистр 2 сдвига под действием тактовых импульсов первого выхода блока 15 синхронизации.

В течение первого такта выходной сигнал первого разряда распределителя 29 импульсов, действующий на четвертом выходе блока 15 синхронизации, поступает через элемент ИЛИ 7 на вход элемента 13 задержки. В следующем такте выходной сигнал элемента 13 задержки через коммутатор 14, элемент И 9, сумматор 3 поступает на информационный вход регистра 1 сдвига. Под действием тактовых импульсов первого выхода блока 15 тшнхрснизации во втором такте в регистр 1; сдвига записьтается единичный сигнал в качестве второго разряда кода. В течение п тактов (первый шаг вычислений) разряды кодов с первого по п-й под действием тактовых импульсов первого выхода блока 15 синхронизации сдвигаются на . выход регистров I и 2 сдвига.

Таким образом, после первого шага вычислений в течение тактов и регистрах сдвига I и 2 сформировались соответственно двоичные коды квадратичной функции и аргумента

х,1. На втором и последующих шагах вычислений -до окончания действия наименьшего импульсного сигнала на выходах формирователей 18 и 19 Им- пульсов квадратор формирует в ре- гистрах 1 и 2 сдвига соответственно двоичные коды квадратичной функции и аргумента согласно соотношению

+4х.., +2, (1) где X и X. - значения аргумента квадратичной .функции на i и на i-1 шагах вычислений соответственно.

Например, установка триггера 4 в единичное состояние i-ым импульсом пачки, действующим на первом выходе тактователя 16 импульсов, обеспечивает формирование в регистрах 1 и 2 сдвига двоичных кодов величин 2х. и X, соответственно согласно соотношению (1) следующим образом.

Под действием тактовых импульсов первого выхода блока 15 оснхрониза- ции на, первый вход сумматора 3 сдай- . гаётся двоичный код величины 2х., iквадратичной функции на предьщущем шаге вычислений, а с выхода регистра 2 сдвига через элементы 12 и 13 держки иа такт, элементы ИЛИ 7, И 9 .и коммутатор 14 на второй вход сумматора 3 сдвигается двоичный код аргу- мента 4х,.

Последовательная задержка элеме

таьи 12 и 13 задержки иа два такта обеспечивает сдвиг на два разряда двоичного кода х- аргумента на предыдущем шаге вьгчислений по отношению к двоичному коду функции 2х , сдвигаемому с выхода регистра 1 сдвига. Сумматор 3 формирует согласно соотношению (1) двоичный код квадратичной функции 2х на i-гом шаге вычислений, который последовательно., начиная с ютадшего разряда, сдвигается с выхода сумматора 3 в регистр 1 сдвига. Сигнал двух единиц млгщшего разряда поступает с четвертого выхода блока 15 синхронизации через элементы ИЛИ 7, И 9, элемент 13 задержки и коммутатор 14 иа второй вход тора 3.

В это время в регистре 2 двоичный код величины х. увеличивается . на единицу. Действительно, установка триггера 4 в единичное состояние обеспечивает разрыв цепн циркуляции кодов с выхода регистра 2 сдвига на его вход, так как элемент И 8 за

s 0

5 Q

5

крыт нулевым сигналом инверсного выхода триггера 4. Следовательно, до возврата триггера 4 в нулевое состояние в младшие разряды кода регистра 2 свдига записываются нулевые сигналы. Триггер 4 вернет в нулевое состояние первый, начиная с младшего разряда, нулевой сигнал кода, ко- торый сдвигается с выхода регистра 2 сдвига. Переход триггера 4 из единичного состояния в нулевое приведет к формированию.на выходе элемента И 8 импульсного сигнала благодаря задержке элементом 11 задержки единичного сигнала прямого выхода триггера 4 его предьщущего состояния. Сл эдовательно, вместо сдвигаемого с выхода регистра 2 сдвига нулевого сигнала на информационный вход регистра 2 сдвига поступает единичный сигнал с выхода элемента И 8. Остальные разряды двоичного кода, сдвигаемого с выхода регистра 2 сдвига, переписываются в регистр 2 сдвига .без изменения через элементы ИЛИ 5 и И 8, так как триггер 4 находится в нулевом состоянии.

Таким образом, двоичный код в регистре 2 сдвига на каждом шаге вычислений увеличивается на единицу и соответствует количеству импульсов, действующих на первом выходе тактователя 16 импульсов.

После окончания действия наименьшего импульса на выходе формирователя 18 или 19 импульсов элемент И 10 закрывается, и на втором выходе тактователя 17 устанавливается нулевой сигнал. Нулевой сНгнал второго выхода тактователя 17 импульсов обеспечивает возврат коммутатора 14 в (Исходное состояние, в котором выход элемента ИПИ 7 подключается ко втог- рому входу элемента И 9, на первом входе которого продолжает действовать строб второго выхода тактователя 16 импульсов до окончания действия наибольшего импульса на выходе формирователя 18 или 19 импульсов.

На интервале времени от момента окончания наименьшего до момента окончания.наибольшего импульса на выходах формирователей 18 и 19 импульсов квадратор формирует сумму квадратов двух величин согласно следующему соотношению:

.+1 (2) где X - наименьшая входная величина; у - наибольшая входная величина.

9

К моменту окончания .наименьшего импульса (соответствующего наимень шей входной величине; в регистре 1 сдвига формируется согласно соотношению (1) двоичный код 2х удвоен- ного значения квадрата наименьшей входной в.еличины, а в регистре 2 сдвига - двоичный код х наименьшей величины.

Допустим, что наименьший импульс величины X окончился на i-ом шаге г

-,г 2

вычислений, тогда и х у. . Поэтому после i-ro шага вычислений Б регистре 1 сдвига coдejDжитcя двоичный код величины 2х у-+х , а в регистре. 2 сдвига двоичный код величинь у. , который с помощью элементя 12 задержки удваивается. Ни выходе элемента ИЛИ 7 формируется последовательный код двоичной величины 2у.+1, так как в младший разряд кода записывается единичный сигнал четвертого выхода блока 15 синхронизации. Последовательный двоичный код величины поступает с выхода элемента ИЛИ 7 через коммутатор 14 и элемент И 9 на второй вход сумматора 3, на первый вход которого с выхода регистра 1 сдвига сдвигается последовательный двоичный код величины у. +х . Результат суммирования, который соглано соотношению (2) равен величине у. х, записывается, начиная с младшего разряда, в регистр I сдвига под действием тактовых импульсов первого выхода блока 15 синхронизации. В зто же время на i+1-ом .шаге вычислений в течение п тактов двоичный код в регистре 2 сдвига в процессе перезаписи с выхода на вход через элементы ИЛИ 5 и И В увеличивается на единицу, как было ранее описано.

На всех последуюа91х шагах вычис- ления.выполняются аналогичным обра- зом до момента окончания наибольшего импульса входной величины у. В этом случае на выходе элемента ИЛИ 6 устанавливается нулевой сигнал, который устанавливаете на перво И втором выходах тактователя 16 импульсов нулевые сигналы. Нулевой сигнал второго выхода тактовате- ля 16 импульсов блокирует элемент И 9, В регистре 1 сдвига динамическим способом путем циркуляции двоичного кода через сумматор 3

j

o

5

0

5

0

5

5

10 фиксируется сумма квадратов двух

2. О

ВХОДНЫХ величин у -1-х .

Одновременно с процессом формирования суммы квадратов двух величин квадратор формирует разность квадратов двух величин у -х следующим образом,

С момента запуска формирователей 18 и 19 импульсов и до момента окончания наименьплего импульса на выходе одного из них элемент И 23 закрыт. Элемент И 23 блокируется нулевым сигналом, формируемым на третьем выходе тактователя 17 импульсов.

Если на информационном входе 25 устройства действует сигнал,пропорциональный величине у, а на информационном входе 26 квадратора - величине х, то при , после окончания наименьшего импульса на выходе формирователя 19 импульсов R- триггер 22 сохранит нулевое состояние, которое соответствует положительному знаку разности у -х .

В случае , после окончания наименьшего импульса на -выходе формирователя 18 импульсов R-триггер 22 устанавливается в единичное состояние наибольшим импульсом, который действует на выходе формирователя 19 импульсов.

Единичное состояние триггера 22 соответствует отрицательному знаку разности у -x. В случае равенства триггер 22 сохраняет начальное нулевое состояние.

Двоичный код абсолютной величи- разности ( формируется в регистре 20 сдвига следующим образом.

Как описывалось ранее, к моменту окончания наименьшего импульса на выходах формирователей 18 и 19 импульсов в регистре 1 сдвига уста- навливается двоичный код удвоенного значения квадрата наименьшей величины, например 2х , а в регистре 2 сдвига - двоичный код наименьшей величины X. После окончания наиме.ньшего импульса на выходе элемента И 10 на втором выходе тактова- теля 17 импульсов формируется нулевой сигнал, который с помощью коммутатора 14 подключает второй вход элемента И 9 к выходу элемента.ШШ 7. На третьем выходе тактователя 17 импульсов формируется инверсный сигнал строба, который открывает

элемент И 23, так как строб наименьшей величины закончил действовать на втором выходе тактователя 17 им-у пульсов.

В этом случае устройство с помощью регистра 20 сдвига и сумматора. 2-1 реализует соотношение

уД, -х()+2у.-И (3) где X - наименьшая входная величина; у - наибольшая входная величина, с начальных условий, которые определяются соотношениями в момент окончания импульса наименьшей величины X на i-OM шаге вычислений: у. -X 0,

У; Х.

Действительно, в течение п тактов на i+l-oM шаге вычислений последовательный двоичный код величины сдвигается под действием тактовых импульсов первого выхода блока 15 синхронизации с выхода регистра 2 сдвига и через элемент 12 задержки на такт, элемент ИЛИ 7, коммутатор 14, элементы И 9 и 23; сумма - тор 21 поступает на первый информационный вход регистра 20 сдвига и последовательно во времени записывается в него, начиная с младшего разряда.

I

Одновременно импульс четвертого

выхода блока 15 синхронизации через элемент ИЛИ 7, коммутатор 14, элементы И 9 и 23, сумматор 21 записывает в младший разряд двоичного кода, сдвигаемого в регистр 20 сдвига, единичный код. Таким образом на i+1-ом вычислений в регистре 20 сдвига сформировался двоичный код величины

уД, . +1.

В течение следующих п тактов на i+2-ом шаге вычислений с выхода регистра 20 сдвига под действием тактовых импульсов первого выхода . блока 15 синхронизации последовательный двоичньш код величины у -X сдвигается на первый вход сумматора 21, на второй вход которого поступает с выхода элемента И 23 последовательный двоичный код величины 2у(, +1, формируемой следующим образом. С выхода регистра 2 сдвига под действием тактовых импульсов блока 15 синхронизации сдвигается двоичный код величины у- , который удваивается с помощью элемента 12 задержки на такт. Импульс четвертого выхода блока 15 синхронизации добавляет единицу младшего разряда к двоичному коду величины, и на выходе элемента ИЛИ 7 формируется

последовательный двоичный код величины. 2у. +1, который, начиная с младшего разряда, поступает через коммутатор 14, элементы И 9 и 23, на второй вход сумматора 21. Сумма-

тор 21 выполняет последовательное суммирование двоичных кодов и на i+2-ом шаге вычислений в течение п тактов на выходе суммы сумматора 21 формируется; последовательный

двоичньй код величины

..- У,, -- ),, +1, который под действием тактовых импульсов первого выхода блока 15 синхрони3ации записывается, начиная с мпадшего разряда, в регистр 20 сдвига.

На всех последунвдих шагах вычисления выполняются аналогичным образом до момента окончания наибольшего

импульса входной величины у. 1осле окончания наибольшего импульса на выходе элемента ИЛИ 6 устанавливается нулевой сигнал, который формирует нулевой сигнал на втором выходе так-

тователя 16 импульсов, блокирующий элемент И 9. Нулевой сигнал выхода элемента И 9 бло1сирует элемент И 23. В регистре 20 сдвига 4 1ксируется динамическим способом путем циркуля-

цин двоичного кода через сумматор 21 разность квадратов двух входных величин .

В случа е, когда , в соотношении (3) следует поменять местами

обозначения х и у. Процесс формирования двоичного кода абсолютной величины разности квадратов двух величин |х в регистре 20 сдвига выполняется аналогичным образом. Как бьшо

ранее описано, в случае , триггер 22 устанавливается в единичное состояние, соответствующее отрица-i тельному знаку разности .

В регистре 2 сдвига запоминается динамическим способом путем циркуля- ции кода через элементы ИЛИ 5 и И 8 двоичный код наибольшей входной величины у.

Тактователь 16 или 17 импульсов (фиг. 2) работает следуювсЕИм образом.

На вход 45 поступает последовательность импульсов, а на вход 46 - сигнал упра)8ления.

В случае отсутствия сигнала)управления на входе 46 и на выходе элемента НЕ 42 устанавливается сигнал логической 1, поступающий через элемент ИЛИ 43 на один из входов элемента И-НЕ 40. Во время паузы между импульсами на входе 45 на выходе элемента И-НЕ 39 формируется сигнал логической 1, который совместно с единичным сигналом выхода элемента ИЛИ 43 устанавливает на выходе элемента И-НЕ 40 сигнал логического О, блокирукиций элемент И-НЕ 39 во время действия импульса на входе 45. Сигнал логической 1 с выхода элемента И-НЕ 39 поддерживает сигнал логического О на выходе элемента НЕ 41. Триггер 44 находится, в нулевом состоянии, в которое его устанавливают импульсы, действуюрще на входе 45.

В случае действия единичного сигнала на входе 46 управления на выходе элемента НЕ 42 устанавливается сигнал логического О. Во время пауэы между импульсами на входе 43 на выходе элемента ИЛИ 43 устанавливается сигнал логического О, Лор 4ирующий на выходе элемента И-НЕ 40 единичный сигнал, который пропускает последо- вательность импульсов входа 45 через элементы И-НЕ 39 и НЕ 41 на выход 46 тактователя импульсов. В .этом режиме во время действия импульса на входе 45 нулевой сигнал на выходе элемента И-НЕ 39 блокирует элемент И-НЕ 40, на выходе которого поддерживается сигнал логической

III и

1 ё

Триггер 44 S-типа предназначен для формирования прямого и инверсного сигналов строба.

Импульс строба, действующий на выходе элемента И-НЕ 40, устанавливает триггер 44 в единичное состояние, в котором он находится до тех пор, пока на выходе элемента И-НЕ 40 действует импульс. В нулево состояние триггер 44 сбрасывается импульсом п-го разряда распределителя 29 импульсов после окончания строба.

Предлагаемый квадратор может использоваться в режиме формирования квадратичной функции, если на один из входов 25 или 26 устройства пост пает входной сигнал (аналоговый или

цифровой), а на другом информационном входе устройства действует нулевой сигнал. Если сигналы на входах 25 и 26 устройства действуют

Одновременно, то квадратор формирует двоичный код. суммы и разность двух входных величин.

Технико-экономическое преимущество предлагаемого квадратора по

сравнению с известным, который фор-г мирует только сумму квадратов двух величин, заключается в расширении функциональных возможностей путем одновременного формирования суммы .

и разности квадратов двух величин, представленных в аналоговой или цифровой форме.

Фор My ла изобретения

Квадратор по авт.св. № 1180885, отличающийся тем, что,, с целью расширения функциональных , возможностей за счет одновременного формирования суммы и разности квадратов двух чисел, в него введены третий регистр сдвига, второй сумматор , второй триггер, четвертый элемент И и четвертый элемент ИЛИ, причем выход третьего регистра сдвига соединен с входом первого слагаемого второго сумматора, выход и вход второго слагаемого которого соединены соответственно с первым информа-; ционным входом третьего регистра и

с выходом четвертого элемента И, вход синхронизации третьего регистра сдвига соединен с первым выходом блока синхронизации, второй выход которого соединен с первым входом

четвертого элемента ИЛИ и с входом разрешения установки в О третьего регистра сдвига, второй информационный вход которого подключен к

шине установки в О квадратора,выход второго элемента И соединен с пер-.

вым входом четвертого элемента И, второй вход которого соединен с третьим выходом второго тактователя импульсов,информационный вход и вход установки в О второго триггера соединены соответственно с выходом второго формирователя импульсов и с выходом четвертого элемента ИЛИ, второй вход которого подключен к выходу первого формирователя импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Квадратор | 1983 |

|

SU1180885A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Квадратор | 1986 |

|

SU1322273A1 |

| Устройство для вычисления полинома второй степени | 1983 |

|

SU1109743A1 |

| Устройство для вычисления суммы квадратов трех величин | 1988 |

|

SU1580356A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Интегро-дифференциальный вычислитель | 1983 |

|

SU1108445A2 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

| Устройство для вычисления полинома второй степени | 1982 |

|

SU1026140A1 |

| Вычислительное устройство | 1983 |

|

SU1144105A2 |

Изобретение относится к области автоматики и вычислительной техники, предназначено для формирования суммы и разности квадратов двух величин, представленных в цифровой или аналоговой форме, и является усовершенст-, рованием устройства по авт. св. № 1180885. Цель изобретения расширение функциональных возможностей путем одновременного формирования суммы и разности квадратов двух чисел. Эта задача решается тем, что квадратор дополнительно содержит регистр сдвига, сумматор, триггер, элементы И и ИЛИ. Информационный выход регистра свдига подключен к первому информационному входу сумматора, выход которого подключен к информационному входу регистра сдвига. Информация в устройстве представляется в число- импульсном коде. В результате работы кольцевой структуры сумматор - регистр сдвига на выходе последнего формируется разность квадратов двух двоичных кодов. Фиксируется знак разности и случай равенства операндов. 2 ил. с SS (Л ISO

| Квадратор | 1983 |

|

SU1180885A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1985-01-29—Подача