(54) ПРОЦЕССОР

ные группы с одинаковыми кодовыми характеристиками. Передача ведется по всем каналам связи данной группы в одном коде или разными кодами, у которых количество и длина стартовой, знаковых и стоповых посылок одинаковы; группа объединяет 16 каналов связи. Передача последовательных посылок знаков во все каналы связи данной группы ведется синфазно, т.е. все одноименные посылки передаются одновременно. Формирование группы посылок осуш.ествляется центральным процессором программным способом. Выполняется это следующим образом.

Из оперативного запоминающего устройства (ОЗУ) выбирается слово, состоящее из двух байтов информации, подлежащих выдаче в два разных канала связи. Из этих байтов выделяются соответствующие одноименные биты и посредством последовательных сдвигов передаются в один из регистров процессора в разряды, соетветствующие номерам тех каналов связи, в которые требуется передать выбранные из ОЗУ байты.

Далее процедура повторяется для новых двух байтов информации и так до тех пор, пока не будет сформирована полная группа (16 разрядов) одноименных битов для передачи их в данную группу каналов связи. После выдачи сформированной группы битов в каналы процедура повторяется для последующих, битов тех же передаваемых знаков, пока знаки не будут выданы полностью. Таким образом, осуществляется групповое преобразование кода знаков.

Недостатком такого процессора является невысокая производительность, связанная с необходимостью выполнения больщого количества логических операций и обращений в ОЗУ.

Целью изобретения является повыщение производительности процессора при работе с телеграфными каналами связи.

Поставленная цель достигается тем, что в предлагаемом процессоре выходы одноименных разрядов регистров блока регистров общего назначения соединены со входами соответствующих разрядов регистра данных оперативной памяти, управляющий вход которого соединен с выходом блока управления.

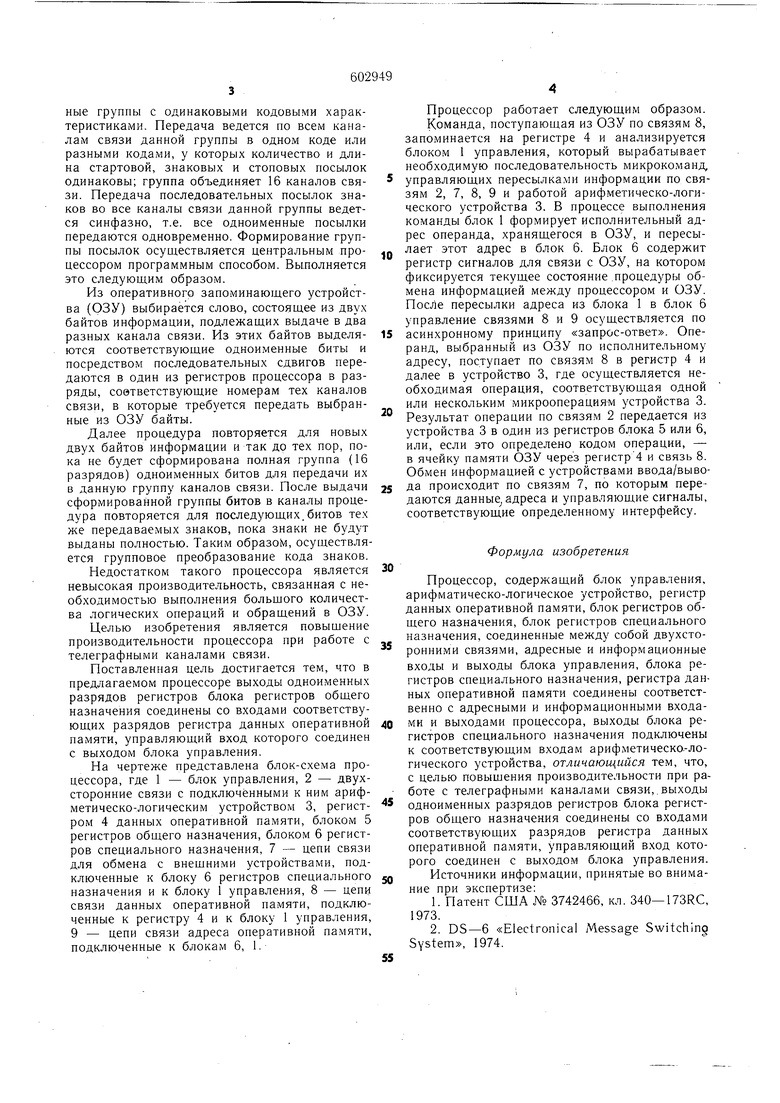

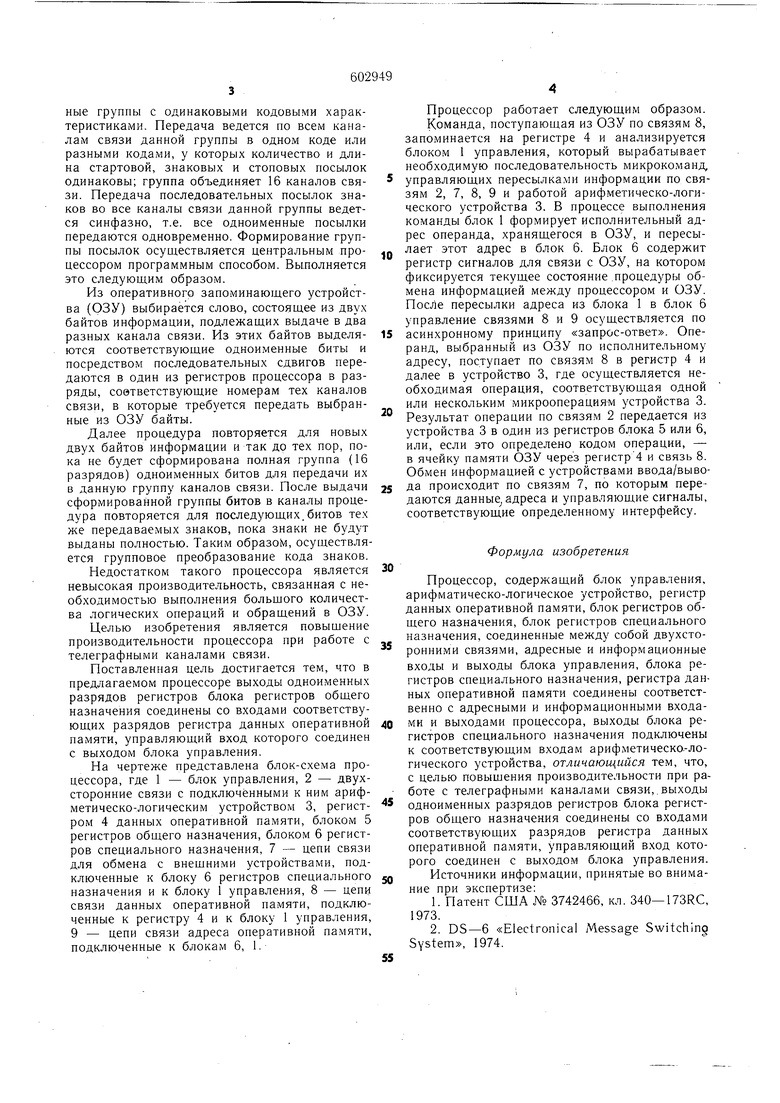

На чертеже представлена блок-схема процессора, где 1 - блок управления, 2 - двухсторонние связи с подключенными к ним арифметическо-логическим устройством 3, регистром 4 данных оперативной памяти, блоком 5 регистров общего назначения, блоком 6 регистров специального назначения, 7 - цепи связи для обмена с внещними устройствами, подключенные к блоку 6 регистров специального назначения и к блоку 1 управления, 8 - цепи связи данных оперативной памяти, подключенные к регистру 4 и к блоку 1 управления, 9 - цепи связи адреса оперативной памяти, подключенные к блокам 6, 1.

Процессор работает следующим образом. Команда, поступающая из ОЗУ по связям 8, запоминается на регистре 4 и анализируется блоком 1 управления, который вырабатывает необходимую последовательность микрокоманд, 5 управляющих пересылками информации по связям 2, 7, 8, 9 и работой арифметическо-логического устройства 3. В процессе выполнения команды блок 1 формирует исполнительный адрес операнда, хранящегося в ОЗУ, и пересы- лает этот адрес в блок 6. Блок 6 содержит регистр сигналов для связи с ОЗУ, на котором фиксируется текущее состояние .процедуры обмена информацией между процессором и ОЗУ. После пересылки адреса из блока 1 в блок 6 управление связями 8 и 9 осуществляется по

5 асинхронному принципу «запрос-ответ. Операнд, выбранный из ОЗУ по исполнительному адресу, поступает по связям 8 в регистр 4 и далее в устройство 3, где осуществляется необходимая операция, соответствующая одной или нескольким микрооперациям устройства 3. Результат операции по связям 2 передается из устройства 3 в один из регистров блока 5 или 6, или, если это определено кодом операции, - в ячейку памяти ОЗУ через регистр4 и связь 8. Обмен информацией с устройствами ввода/вывода происходит по связям 7, по которым передаются данные адреса и управляющие сигналы, соответствующие определенному интерфейсу.

Формула изобретения

Процессор, содержащий блок управления, арифматическо-логическое устройство, регистр данных оперативной памяти, блок регистров общего назначения, блок регистров специального назначения, соединенные между собой двухсторонними связями, адресные и информационные входы и выходы блока управления, блока регистров специального назначения, регистра данных оперативной памяти соединены соответственно с адресными и информационными входами и выходами процессора, выходы блока регистров специального назначения подключены к соответствующим входам арифметическо-логического устройства, отличающийся тем, что, с целью повыщения производительности при работе с телеграфными каналами связи,.выходы

одноименных разрядов регистров блока регистров общего назначения соединены со входами соответствующих разрядов регистра данных оперативной памяти, управляющий вход которого соединен с выходом блока управления.

Источники информации, принятые во внимание при экспертизе:

1.Патент США № 3742466, кл. 340-173RC, 1973.

2.DS-6 «Electronical Message Switching System, 1974.

/7

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1247884A1 |

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| СИСТЕМА ТРЕВОЖНОЙ СИГНАЛИЗАЦИИ | 1994 |

|

RU2103744C1 |

| СШТШДА ОБРАБОТКИ ДАННЫХ1 Т Бii^f;'- ViJ- i^ О г^ ал | 1970 |

|

SU433484A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

Авторы

Даты

1978-04-15—Публикация

1976-08-17—Подача