. Изобретение относится к вычислительнои технике

Известны системы обработки данных, содержащие селекторные каналы, щ-льтиплексный канал, пульт

:управления и процессор, включающий оперативную память, адресный и информационные регистры, арифметическо-логическое устройство,

блок регистров, блок защиты памя.ти и устройство микропрограммного управления. Однако известная сиетема имеет большой состав обор дования и недостаточное быстродействие. Цель предлагаемого изобретения - сократить состав оборудования и повысить быстродействие системы.

Это достигается тем, что сис|Тема содержит дополнительно блок

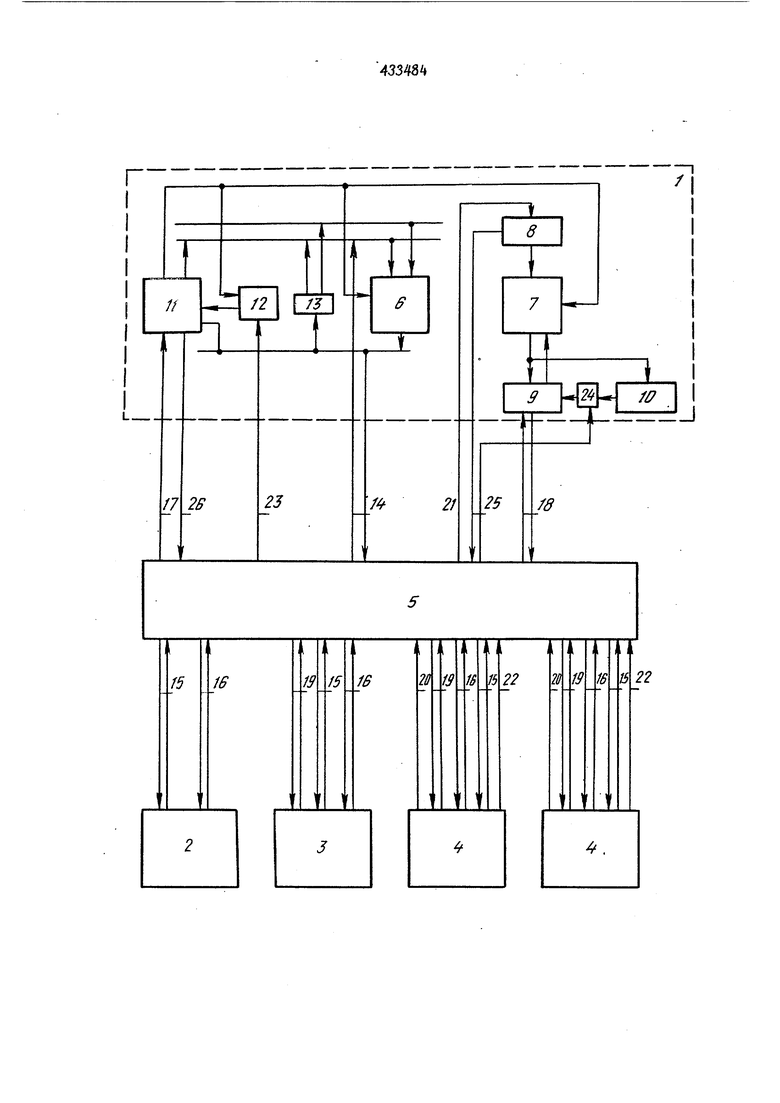

I у правления каналами, информацион- ные и управляющие входы и зыходы которого соединены соответственно с информационными и управляющими выходами и входами пульта управления, г льтиплексного канала и селекторных каналов, адресные входы и выходы защиты- с адресными выходами и выходами защиты селекторных каналов, выход запросов с входом запросов устройства микропрограммного управления, выходы считывания которого.под1слючены к одноименным входам блока управления каналами, выходы защиты которого соединены с информационным входом блока защиты памяти, вторые информационные входы и выходы - с информационными выходами и входами арифметическо-логического устройства, адресные выходы- с входами адресного регистра, одш из выходов которого подключен к ком1уутационноц7 входу блока управления каналами, третьи информационные входы и выходы которого соединены со вторыми выходами и входами информационного регистра, дополнительный информационный регистр, ко входу которого подключен выход оперативной памяти, и . олок связи, информационный вход которого соединен с выходом дополнительного информационного регистра, выход - с третьим входом информационного регистра, а управля зщии вход - с выходом управ.ления передачами связи блока упра ления каналами, Система обработки данных состоит из процессора I, пульта уп§авления 2, мультиплексного канала и двух селекторных каналов 4, подключенных к процессору I через блок 5 управления каналами. Процессор предлагаемой систем предназначен для управления процео сами обработки, хранения и передачи данных. Процессор содержит арифметическо-логическое устройство 6, оперативную память 7 с адресным регистром 8, основным.и дополнительным информационными регистрами 9 и 10, соответственно устройст во II микропрограммного управления (с постоянной памятью), блок 12 защиты памяти и блок 13 регистров. Пульт управления 2 содержит органы управления и индикации, необходимые для работы и управления системой обработки дан1шх. 1 льтиплексный канал 3 предназначен для подключения к процессору устройств ввода-вывода малой и средней скорости и может работать в й/огльтиплексном или монополь ном режиме. Селекторные каналы 4 предназначены для под1шоченш к процессору быстродействующих устройств вво да-вывода и могут работать только в монопольном режиме. Блок 5 управления каналами поз воляет рассматривать пульт управле ния и каналы ввода-вывода как один физически подключенный к процессеру канал, Операция передачи данных начинается по специальной инструкции, которая задает адрес канала и устройства ввода-вывода и при помощи специальных управляющих слов указывает код команды, начальный адрес основной памяти, количество байтов данных, которые необходимо передать, управлякхцие признаки и ключ защиты. 1(анал формирует управляющее слово устройства и хранит его на своих регистрах: в селекторных каналах на схемных регистрах, а в мультиплексном - в специальной области основной памяти, называемой ь глвтиплексной памятью. Передача управляющей информации мелодг процессором I и регистрами каналов 2, 3, 4 производится через арифметическо-логическое устройство 6, информационные шины 14 арифметическо-логического устройства процессора, блок 5 управления каналами и информационные шины 15 арифметическо-логического устройства каналов Получив команду, канал освобож-, дает процессор для выполнения других инструкции, 1 / льтиплексный канал при готовности принять или передать байт или группу байтов данных возбуждает запрос, который через соответствующую шину 16 управления каналами, блок 5 управления каналами и шины 17 запросов на микропрограммное прерывание поступает в блок il микропрограммного управления. По этол/у сигналу выполняется специальная микропрограмма, которая запоминает содержимое регистров процессора в специальной области оперативной памяти, называемой ло1сальной паг штью; считывает управляющее слово из мультиплексной памяти на регистры процессора и производит обмен данными между оперативной памятью 7 и каналом через информационные шины 18 оперативной памяти процессора, блок 5 управления каналами и информационные шины 19 оперативной памяти каналов, Ддрес данных и счетчик байтов модифицируются микропрограммно через арифметическо-логическое устройство В, затем управляющее слово устройства записывается на свое место в ь/1ультиплексную память и продолжается выполнение прерванной микропрограммы.

При передаче данных между оелекто рными каналами и оперативной

памятью работа блока микропрограммного управления по. запрооу канала, поступающегду через блок 5 управления и шины 17 запросов на микропрограммное прерывание, приостанавливается на цжл передачи данных между оперативной памятью и каналами через информационные шины 18 оперативной памяти процессора, блок 5 управления каналами и информационные шины 19 оперативной памяти каналов. При этом адрес основной памяти передается из канала через адресные шины 20 оперативной памяти канала, блок 5 управления каналами и адресные шины 21 оперативной памяти процессора в адресны регистр 8 оперативной памяти, а также ключ защиты памяти из канала через шины 22 защиты канала, блок 5 управления каналами и шины 23 защиты процессора в выходной регистр блока 12 защиты памяти.

Так как цикл передачи данных селекторного канала может быть выполнен после любого цшша записи в основную намять, а содержимое инфорглационного регистра оперативной naMfiTM часто используется последующими микрокомандами, в системе обработки данных имеется дополнительный информационный регистр 10, инфорг иция в который поступает из оперативной памяти 7 одновременно с занесением ее в основной информационный регистр 9 и, таким образом, содер;;шмое дополнительного регистра 10 при микpoпpoгpa лмEюм обращении к оперативной памяти является копией основного регистра 9. При выполнении цшиюв передачи данных селекторных каналов всегда используется основной информационный регист 9, поэто после окончания этого цикла для восстановления исходног состоятся информацион1шх регистро содержимое дополнительного информационного регистра 10 оперативной памяти передается через схему передачи 24 в основной информаЦИОН1ШИ регистр 9 по сигналу, посту пающецу из блока 5 управления каналами по одной из шин 25 управления передачами в основную паглять.

После окончания передачи данных канал (г ультиплексный или селекторный) возбуадает запрос на микропрограммное прерывание и передает в процессор информацию о состоянии канала и устройства -ввода-вывода.

Адреса регистров и каналов, в которые должна приниматься или из которых должна передаваться информация, указываются в микрокомандах и через шины 26 считывания полей микрокоманды, блок 5 управления каналами и шины 16 управления канала1м поступают в каналы.

nPEJCvET ИЗОБРЕТШИЯ

Система обработки данных, содержащая пульт управления, л/ультиплексный канал, селекторные каналы и процессор, включающий оперативную пакшть, адресный и информационные регистры арифметическо-логическое устройство, блок регистров блок защиты памяти и устройство микропрограшлного управления, управляющий выход которого подключен к управляющим входам блока защиты памяти, арифметическо-логического устройства и оперативной памяти, информационный выход устройства микропрограммного управления соединен с первым информационным входом арифметическо-логического устройства и с одним из инсЬорглационных выходов блока регистров, другой информационный выход которого соединен со вторым информационным входом, арифметическо-логического устройства, информационный выход которого подключен к информационным входам блока регистров и устройства микропрограмм1-юго управления, управляющий вход которого соедиЕ1ен с выходом блока защиты памяти, адресный вход .оперативной памяти подключен к выходу адресного регистра, а информационные входы и выходы ее соединены соответственно с выходами и входами информационного регистра, отличающаяся тем, что,с целью сокращения состава оборудования и повышения быстродействия систегш, она содержит дополнительно блок управления каналами, информационные и управляющие входы и выходы которого соединены соответственно с информаЦИОННЫЛ1И и управляющими выходами

пульта управления мультиплексного канала и селекторных каналов, адресные входы и входы защиты - с адресными выходами и выходами зашиты селекторных каналов, выход запросов - с входом запросов устройства мшфопрограммного управления, выходы считывания которого подключены к одноименным входам блока управления каналами, выходы зашиты которого соединены с инфорг;1ационным входом блока защиты памяти, вторые инсрормационные входы и ВЫХОД. - с информационными выходами и входами арифметическо-логического устройства, адресные выходы - с входами адресного регистра,

один из выходов которого подх лхочеп к коШ4утационно1уу входу блока управления каналами, третьи информационные входы и выходы которого соединены со вторыш;; выходами и входами информационного регистра, дополнительный информационный регистр, ко входу которого подключен выход оперативной памяти, и блок связи, информационный вход которого соединен с выходом дополнительного инфорглационного регистра, выход с третьим входом инфоргиационногорегистра, а управшпощий вход --с выходом управления передачами связи блока управления каналами.

19

15

16

f5

1B

22

19

15

22

2Q

19

15

IB

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления каналами | 1973 |

|

SU518769A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КАНАЛАМИ | 1973 |

|

SU386395A1 |

| Мультиплексный канал | 1973 |

|

SU517022A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для управления диагностикой каналов | 1973 |

|

SU526876A1 |

| Селекторный канал | 1973 |

|

SU519703A1 |

| Селекторный канал | 1973 |

|

SU517019A1 |

| Устройство управления каналами | 1972 |

|

SU545983A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Мультиплексный канал | 1980 |

|

SU879580A1 |

Даты

1974-06-25—Публикация

1970-08-12—Подача