(54) N-РАЗРЯДНЫЙ ПАРАЛЛЕЛЬНЫЙ СУММАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

| Последовательный сумматор | 1983 |

|

SU1149248A1 |

| Последовательный сумматор | 1977 |

|

SU696452A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| Последовательный сумматор | 1987 |

|

SU1411734A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для сложения чисел | 1982 |

|

SU1035599A1 |

| КОМБИНАЦИОННЫЙ СУММАТОР СТРУКТУРНЫХ КОДОВ | 1991 |

|

RU2023288C1 |

| Устройство для сложения в избыточной двоичной системе счисления | 1977 |

|

SU696450A1 |

| Обратимый п-разрядный сумматор | 1979 |

|

SU824204A1 |

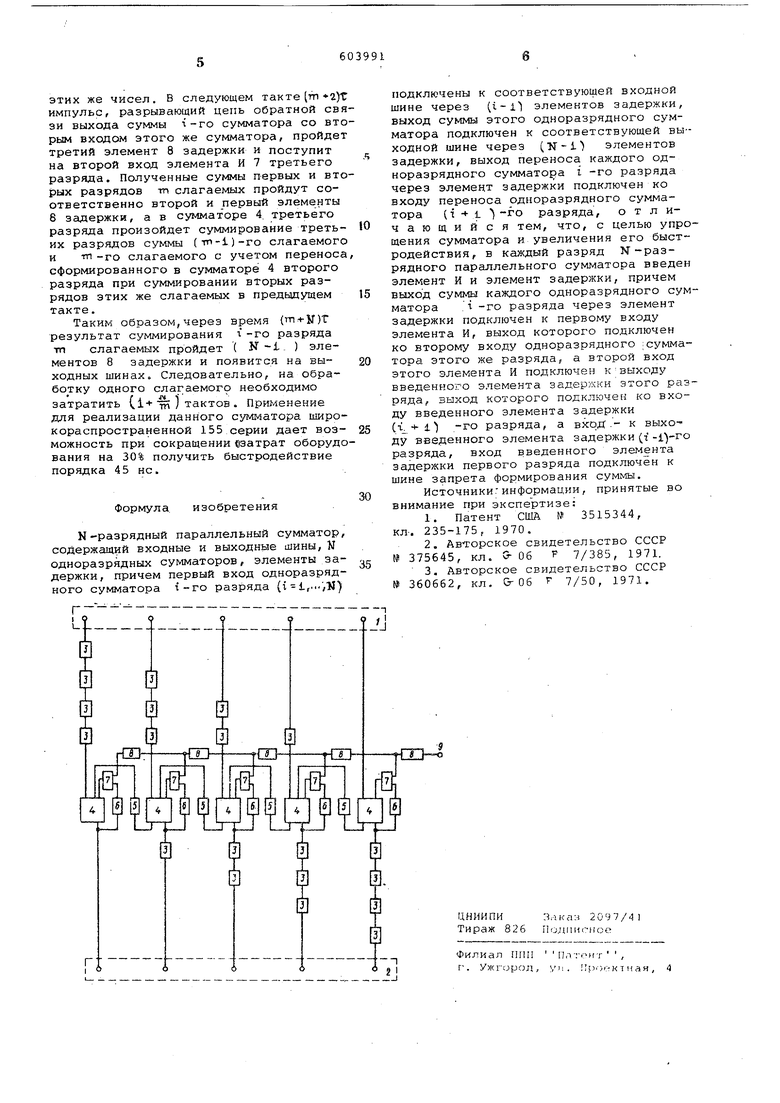

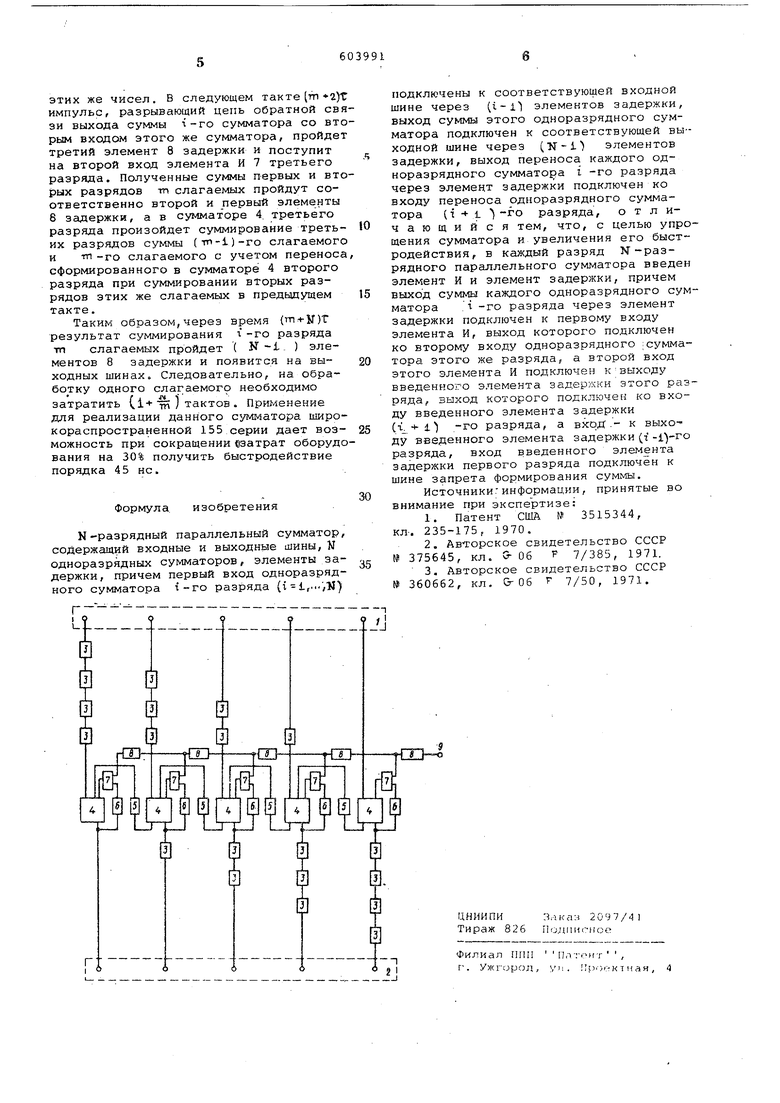

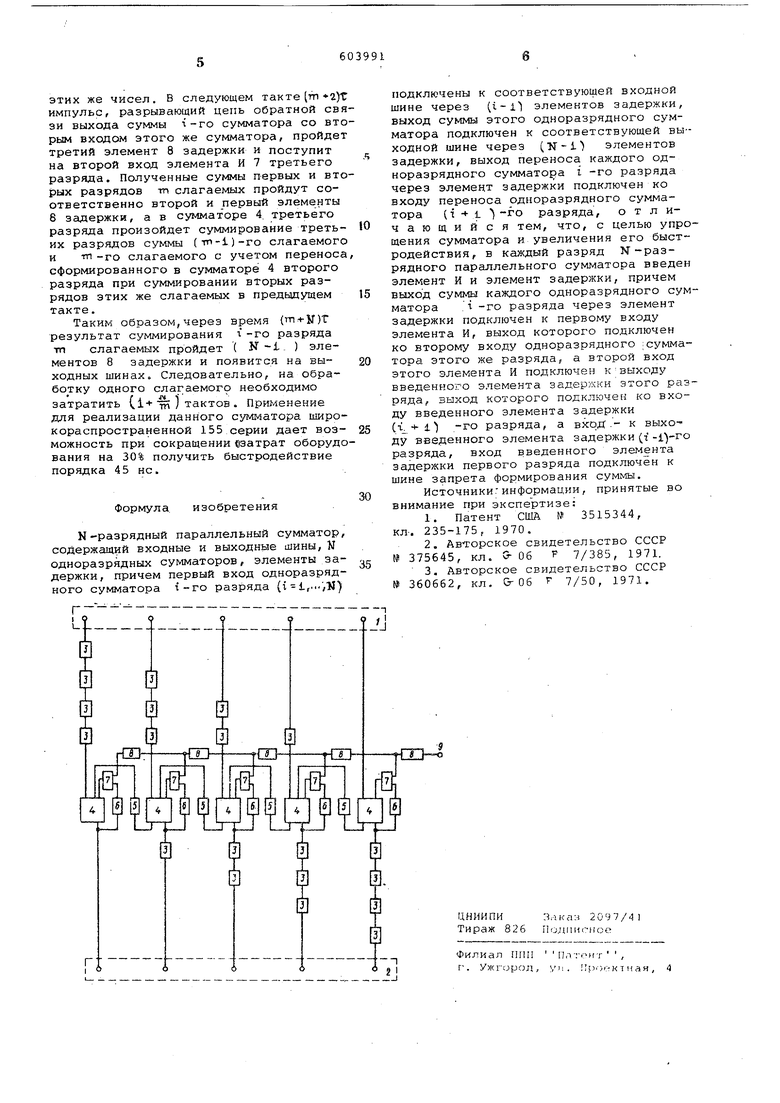

Изобретение относится к вычислитель Ной технике и может быть использовано ё арифметических устройствах ЦВМ и специализированных вычислительных машинах большой производительности. Известен многоступенчатый сумматор накапливающего типа с сохранением переноса, состоящий из нескольких сумма торов с сохранением переноса, соединен Иых в структуру, которая допускает сум мирование множества многоразрядных чисел 1 . Недостатком такого сумматора являются значительные аппаратурные затраты. Известен параллельный двоичный сумматор накапливакнцего типа, содержащий триггера,элементы задержки и входную логику, формирующую сигналы сдвига нуж ных разрядов 2 , Такой сумматор имеет низкое быстродействие, Прототипом изобретения является 1 разрядный параллельный сумматор, содер жащий входные и выходные шины, N одноразрядных сумматоров, элементы задержки, причем первый вход одноразрядного сумматора L-го разряда (,...,) подключен к соответствующей входнрй шине через (L-1) элементов задержки. выход суммы этого одноразрядного сумматора подключен к соответствующей выходной шине через (N-i )элементов задержки , выход переноса каждого одноразрядного сумматора i-го разряда Через элемент задержки подключен ко входу переноса одноразрядного сумматора ( i +1)-го разряда 3. в этом сумматоре необходимо использовать блок сдвига числа и блок промежуточной памяти, составляющие около 35% оборудования всего устройства. Кроме того, производительность сум- . матора,когда число слагаемых тп близко к N, например m ы, число тактов необходимых на обработку одного слагаемого, не может быть меньше (1+ ( ). Целью изобретения является .упрощение cyMviaTopa и повышения его быстродействия. Достигается она тем, что в каждый разряд N-разрядного пйраллельного сумматора введен элемент И и элемент з-адержки, причем выход суммы каждого одноразрядного сумматора i. -го разряда через элемент задержки подключен к первому входу элемента И, выход которого подключен ко второму входу одноразрядного сумматора этого же разряда, а второй вход этого же элемен-та И подключей к выходу введенного элемента задержки этого разряда, выход которого подключен ко входу введенного элемента задержки ( i +1)-го разряда, а вход к выходу введенного элемента задержки ( г -1)-го разряда, вход введенного элемента задержки первого разряда подключен JC шине запрета формирования сум мы. Яа чертеже дана функциональная схема пятиразрядного параллельного сумматора. Входные и выходные шины 2 сумматора через последовательно Соединенные элементы 3 задержки подключены к . одному из входов и выходу суммы, соответственно, каждого одноразрядного сум матора 4. Выход переноса каждого t-ro одноразрядного сумматора 4 соединен че рез элемент 5 задержки (такой,что сигнал на его выходе появляется через лреМя Т, равное интервалу подачи слагаемых на входные шины) со входом переноса ( г +1)-го одн-оразрядногр сумматора 4 . Выход суммы каждого -го одноразрядного сумматора 4 через элемент 6 задержки (такой, что сигнал на его выходе появляется также через время Т. ) элемент И 7, второй вход которого ч.ереэ последовательно соединенные элементы 8 задержки подключены к шине запрета формирования суммы. В исходном положении на входных шинах 1 присутствуют нулевыесигналы. В процессе суммирования на входные шины 1 через интервалы времени, равные С, подаются суммирующие числа. Через время Т первый разряд первого слагаемого пройдет через сумматор 4 перво го разряда, элемент б задержки и элемент 7 первого разряда и попадает на второй вход сумматора 4 первого разряда. В это же время т на входные шины подается второе слагаемое. В следующем такте ( 2t.) происходит суммирование в сумматоре 4 первого раз ряда первых разрядов первого и второго слагаемых и сумма их через элемент б задержки и.элемент И 7 первого разряда поступит на второй вход сумматора 4 пе вого разряда, В это же время ( 2 ) второй разряд rsepBoro слагаемого, про дя через элемент 3 задержки,сумматор второго ряда, элемент 6 задержки и Элемент И 7 второго разряда поступит на второй- вход сумматора 4 второго ра ряда. Перенос, сформированный при суммировании первых разрядов, через элемент 5 задержки поступит на вход пере носа сумматора 4 второго разряда; вто рой разряд второго слагаемого, пройдя элемент 3 задержки, попадет на. ,;ервый вход сумматора 4 второго разряда. В последующем такте (ЗГ ) происхо дит суммирование первых разрядов суммы предьопуиих двух слагаемых и третье го слагаемого,, поданного на входные ш ны, суммирование вторых разрядов первых даух слагаемых с учетом переноса Сформированного при суммированнии первых разрядов этих же слагаемых.В это же время (ЗТ ) полученные суммы поступают соответственно через элемент б задержки и элемент И 7 первого разряда на второй вход сумйатора 4 первого разряда; через элемент 6 задержки и элемент И второго разряда на второй вход сумматора 4 второго разряда. Перенос, сформированный в сумматоре 4 первого разряда, пройдя через элемент задержки 5, поступит на вход переноса сумматора 4 второго разряда, а перенос, сформированный сумматором второго разряда 4, через элемент задержки 5 - на вход переноса сумматора 4 третьего разряда. В этот же момент времени (ЗТ ) третий разряд первого слагаемого, пройдя два элемента задержки 3, сумматор 4 третьего разряда, элемент б задержки, элемент И 7 третьего разряда, попадет на второй вход сумматора 4 третьего разряда, а на первый вход этого же сумматора, пройдя два элемента задержки 3 поступит третий разряд второго слагаемого; на первый вход сумматора 4 второго разряда, пройдя элемент задержки 3 поступит второй разряд третьего слагаемого, а на входные шины подается четвертое слагаемое . Таким образом, в каждом последующем такте, происходит суммирование i -X разрядов результата от сложения ( тп- ц ) слагаемых, где , m-i , - - 3,2,1, и (m-k-t-i )-го слагаемого. Через время ( тп - i )Т на втором входе сумматора 4 первого разряда появится сумма первых разрядов (m-i ) слагаемого, а на первом входе этого же сумматора первый разряд тп -го слагаемого. В следующем такте -mt происходит суммирование этих разрядов. Для очистки сумматоров 4 перед суммированием следующего массива чисел на второй вход элементов И 7 подаются импульсы запрета-.формирования суммы с шины 9 запрета формирования суммы. Схема подачи этого импульса может быть реализована, например, следующим образом. В момент времени тлг через- элемент 8 задержки на второй вход элемента И 7 первого разряда подается необходимый импульс, разрывающий цепь обратной связи выхода суммы сумматора 4 первого разряда со вторым входом этого сумматора. В следующем такте ( )Г импульс, разрывающий цепь обратной связи выхода суммы л-го сумматора со вторым входом этого же сумматора, пройдет второй элемент 8 задержки и поступит на второй вход элемента и 7 второго разряда. Полученная сумма первых разрядов проходит элемент 8 задержки, а в сумматоре 4 второго разряда пройдет суммирование вторых разрядов суммы (т i)pQ слагаемого и тп-го слагаемого с учетом переноса, сформированного в предыдущем такте при сложении

Авторы

Даты

1978-04-25—Публикация

1976-06-04—Подача