22

Изобретение относится к вычисли™ тельной технике и может быть использовано в процессорах вычислительных машин для обработки графической ий- формации, а также при создании специализированных векторных вычислительных машин, j Цель изобретения - расширение Фзшкциональных возможностей за счет сложения чисел в кодах с иррациональным основанием v2.

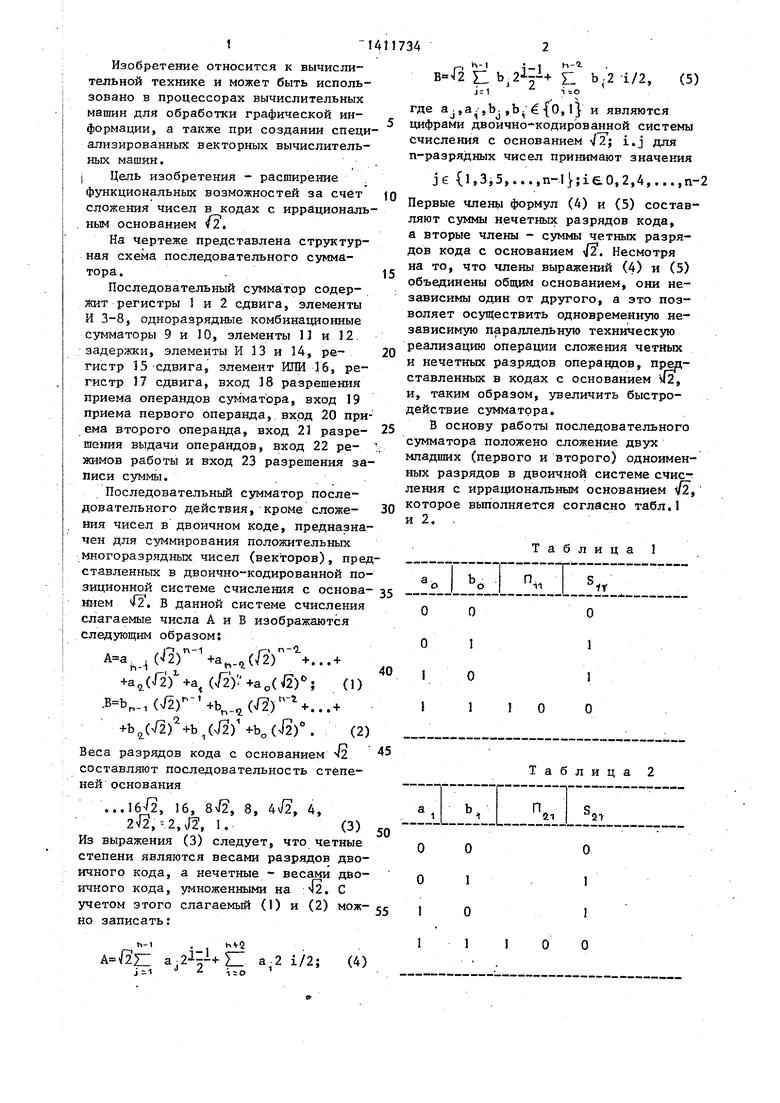

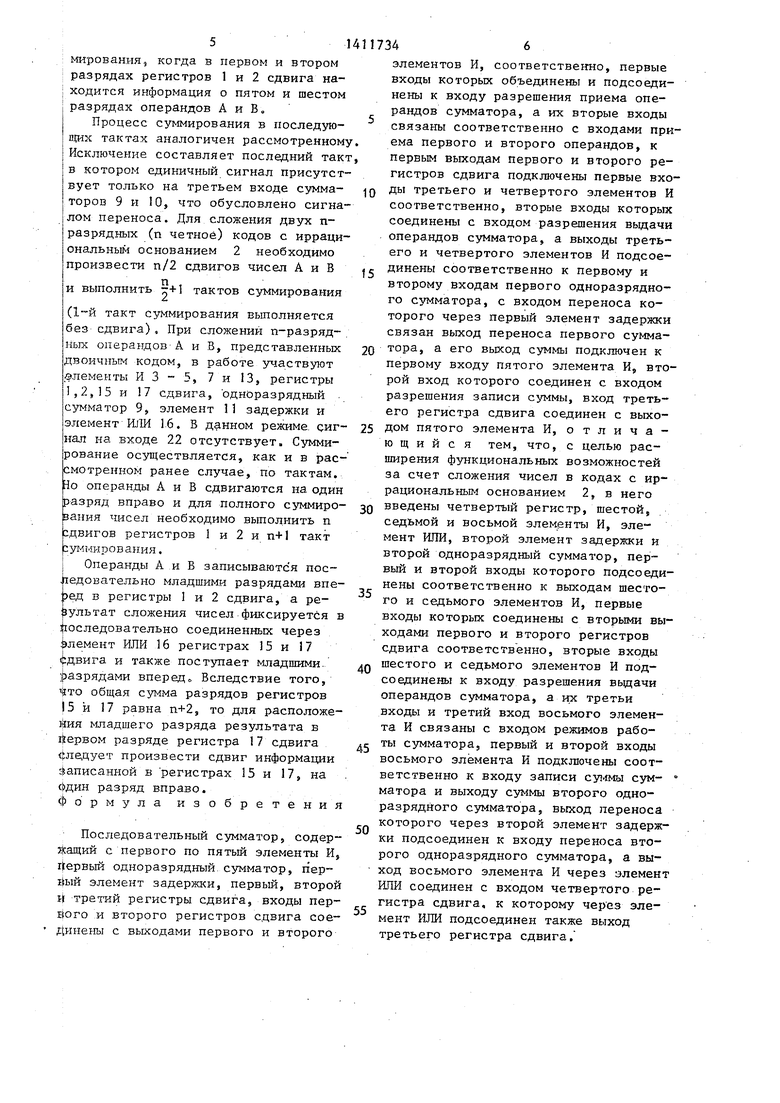

На чертеже представлена стрз ктур- ная схема последовательного сумматора..

Последовательный сумма:тор содер- жит регистры } и 2 сдвига, элементы И 3-8, одноразрядные комбинационные сумматоры 9 и 10, элементы П и 12. задержки, элементы И 13 и 14, ре- гистр 15 сдвига, элемент ИЛИ 16, регистр 17 сдвига, вход 18 разрешения приема операндов сумматора, вход 19 приема первого операнда, вход 20 приема второго операнда, вход 21 разре- шения выдачи операндов, вход 22 ре- жимов работы и вход 23 разрешения записи суммы.

Последовательный сумматор последовательного действия, кроме сложа- ния чисел в двоичном коде, предназначен для суммирования положительных многоразрядных чисел (векторов), представленных в двоично-кодированной позиционной системе счисления с основа-

,-I

кием 42. В данной системе счисления слагаемые числа А и В изображаются следующим образом:

I П-1r (J2) +а.(Г2) +...+

+а,,(Г2 ) +а(/2 ) +а„(Я) ; (1) .,.,(N r +b.(/)...+ Ь(Л)+Ь /V/2) +Ь„ (& . (2)

Веса разрядов кода с основанием х2 составляют последовательность степеней основания

...16, 16, бх/, 8, 4v/2, 4,

2vf3, r2,f2 , I.(3)

Из выражения (3) следует, что четные степени являются весами разрядов дво

h-1

-(2 il Ь.

С b.2 i/2, (5)

где a ., a ., b. , b € { 0,1} и являются цифрами двоично-кодированной системы счисления с основанием /2; i.j для п-разрядных чисел принимают значения

J6 (l,3,5,...,n-l};i6.0,2,4,...,nПервые члень формул (4) и (5) составляют суммы нечетных разрядов кода, а вторые члены - суммы четных разрядов кода с основанием . Несмотря на то, что члены выражений (4) и (5) объединены общим основанием, они независимы один от другого, а это позволяет осуществить одновременну независимую параллельную техническую реализацию операции сложения четных и нечетных разрядов операндов, представленных в кодах с основанием У2, и, таким образом, згвеличить быстродействие сумматора.

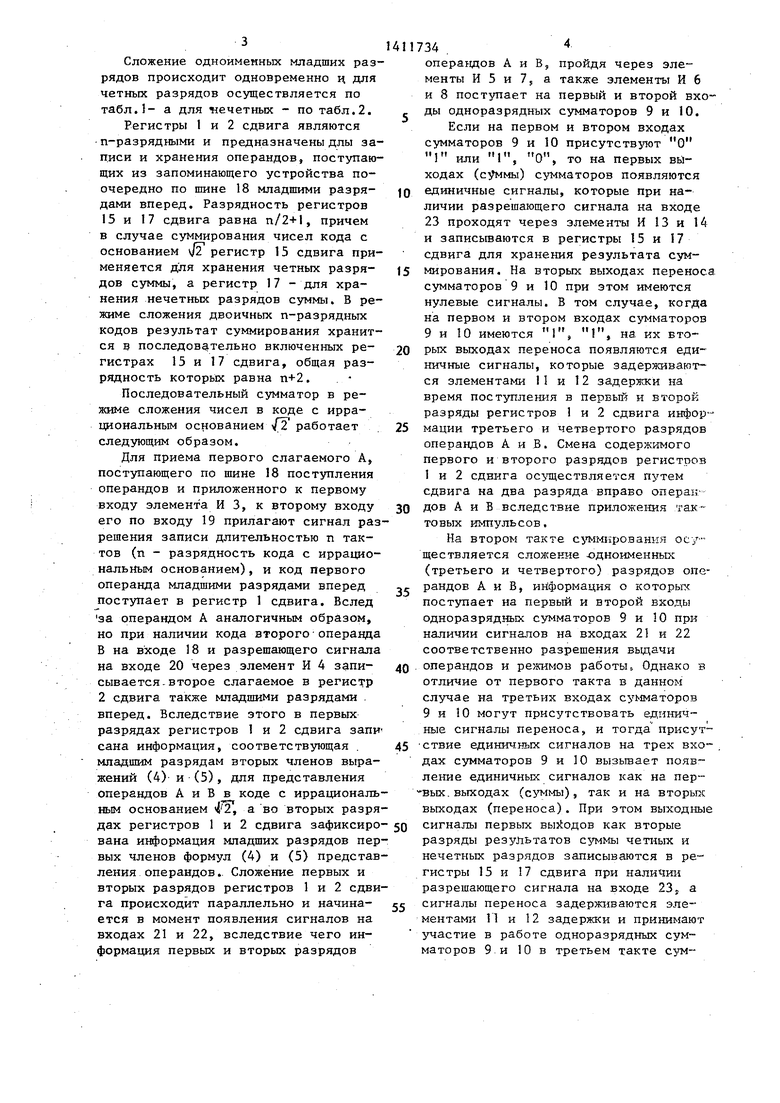

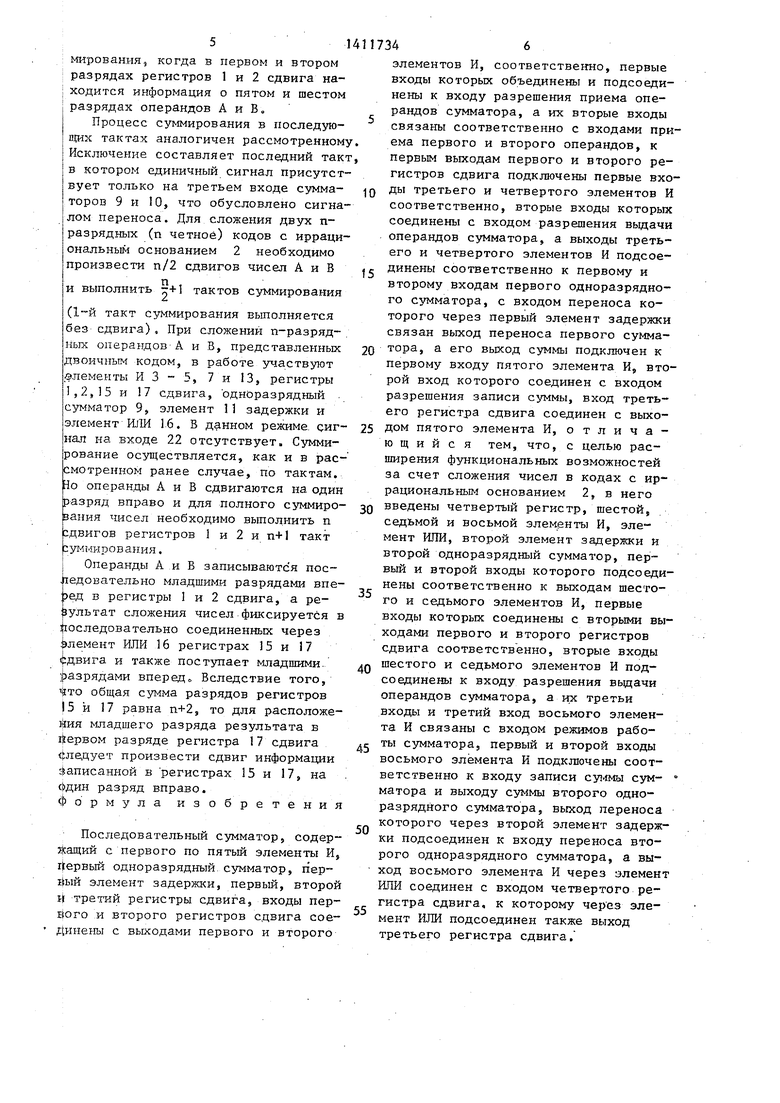

В основу работы последовательного сумматора положено сложение двух младших (первого и второго) одноименных разрядов в двоичной системе счис-; ления с иррациональным основанием v2, которое выполняется согласно табл,1 и 2. .

Таблица 1

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Сумматор п-разрядных комплексныхчиСЕл | 1979 |

|

SU817699A1 |

| Параллельный накапливающий сумматор | 1988 |

|

SU1578710A2 |

| Устройство для суммирования двоичных чисел | 1988 |

|

SU1578709A2 |

| Последовательный сумматор кодов с иррациональными основаниями | 1983 |

|

SU1170449A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1985 |

|

SU1259249A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных процессорах для обработки графической информации, а также при создании специализированных векторных вычислительных машин. Целью изобретения является распшрение функциональных возможностей за счет сложения чисел в кодах с иррациональным основанием Г2. Последовательный сумматор содержит регистры сдвига 1 и 2, злементы И 3-8, одноразрядные комбинационные сумматоры 9 и 10, элементы задержки 11 и 12, элементы И 13 и 14, регистр сдвига 15, элемент ИЛИ 16 и регистр сдвига 17. Сумматор имеет вход 18 разрешения приема операндов, вход 19 приема первого операнда и вход 20 приема второго операнда, вход 21 разрешения вьщачи операндов вход 22 режимов работы и вход 23 разрешения записи суммы. 1 ил., 2 табл. (g aseis

ичного кода, 1-гчного кода, учетом этого но записать г

а нечетные - весами дво- умноженными на N2. С слагаемый (1) и (2) мож

чгО

а 2 1

i/2; (4)

3

Сложение одноименных младших разрядов происходит одновременно ц для четных разрядов осуществляется по табл.- а для нечетных - по табл.2.

Регистры 1 и 2 сдвига являются п-разрядными и предназначены длы записи и хранения операндов, поступающих из запоминающего устройства поочередно по шине 18 младшими разрядами вперед. Разрядность регистров 15 и 17 сдвига равна n/2+l, причем в случае суммирования чисел кода с основанием v/ регистр 15 сдвига применяется для хранения четных разрядов суммы, а регистр 17 - для хранения нечетных разрядов суммы. В режиме сложения двоичных п-разрядных кодов результат суммирования хранится в последов«1тельно включенных регистрах 15 и 17 сдвига, общая разрядность которых равна п+2. .

Последовательный сумматор в режиме сложения чисел в коде с иррациональным основанием /2 работает следующим образом.

Для приема первого слагаемого А, поступающего по шине 18 поступления операндов и приложенного к первому входу элемента И 3, к второму входу его по входу 19 прилагают сигнал разрешения записи длительностью п тактов (п - разрядность кода с иррациональным основанием), и код первого операнда младшими разрядами вперед поступает в регистр 1 сдвига. Вслед за операндом А аналогичным образом, но при наличии кода второго-операнда В на входе 18 и разрешающего сигнала на входе 20 через элемент И 4 записывается -второе слагаемое в регистр 2 сдвига также младшими разрядами . вперед. Вследствие этого в первых разрядах регистров 1 и 2 сдвига запи сана информация, соответствующая . младшим разрядам вторых членов выражений (4) и (5), для представления операндов А и В в коде с иррациональным основанием ( 2, а во вторых разрядах регистров 1 и 2 сдвига зафиксирована информация младших разрядов первых членов формул (4) и (5) представления операндов.. Сложение первых и вторых разрядов регистров 1 и 2 сдвига происходит параллельно и начинается в момент появления сигналов на входах 21 и 22, вследствие чего информация первых и вторых разрядов

операродов А и В, пройдя через элементы И 5 и 7s а также элементы И 6 и 8 поступает на первый и второй вхо - ды одноразрядных сумматоров 9 и 10.

Если на первом и втором входах сумматоров 9 и 10 присутствзлот О

Г

или

Г

О , то на первых выходах (суммы) сумматоров появляются единичные сигналы, которые при наличии разрешающего сигнала на входе 23 проходят через элементы И 13 и 14 и записьшаются в регистры 15 и 17 сдвига для хранения результата сум- мирования. На вторых выходах переноса сумматоров 9 и 10 при этом имеются нулевые сигналы. В том случае, когда на первом и втором входах сумматоров

9 и 10 имеются 1

tt 1II 1111t

на их вторых выходах переноса появляются единичные сигналы, которые задерживаются элементами 11 и 12 задержки на время поступления в первьй и второй разряды регистров 1 и 2 сдвига инфор-мации третьего и четвертого разрядов операндов А и В. Смена содержимого первого и второго разрядов регистров 1 и 2 сдвига ос:,тцествляется путем сдвига на два разряда вправо операидов А и В вследствие приложехтая тактовых импульсов.

На втором такте суммирования осуществляется сложение -одноименных (третьего и четвертого) разрядов операндов А и В, информация о которых поступает на первый и второй входы одноразрядных сумматоров 9 и 10 при наличии сигналов на входах 21 и 22 соответственно разрешения вьщачи

операндов и режимов работы. Однако в отличие от первого такта в данном случае на третьих входах сумматоров 9 и 10 могут присутствовать единичные сигналы переноса, и тогда присут-ствие единичных сигналов на трех входах сумматоров 9 и 10 вызьтает появление единичных сигналов как на пер- ВЫХ. выходах (сз ммы), так и на вторьпс выходах (переноса). При этом выходные

сигналы первых выводов как вторые разряды результатов суммы четных и нечетных разрядов записываются в регистры 15 и 17 сдвига при наличш разрешающего сигнала на входе 23j а

сигналы переноса задерживаются элементами 11 и 12 задержки и принимают участие в работе одноразрядных сумматоров 9-и 10 в третьем такте суммирования, когда в первом и втором разрядах регистров 1 и 2 сдвига находится информация о пятом и шестом разрядах операндов А и В.

Процесс суммирования в последую- пдах тактах аналогичен рассмотренному Исключение составляет последний такт в котором единичный сигнал присутствует только на третьем входе сз мма- торов 9 и 10, что обусловлено сигналом переноса. Для сложения двух п- разрядных (п четное) кодов с иррациональным основанием 2 необходимо произвести п/2 сдвигов чисел А и В

п , и выполнить -+1 тактов суммирования

( такт суммирования выполняется без сдвига). При сложений п-разряд- иых операндов А и В, представленных двоичным кодом, в работе участвуют элементы И 3 - 5, 7 и 13, регистры 1,2,15 и 17 сдвига, одноразрядный . сумматор 9, элемент 11 задержки и элемент Ш1И 1.6, В данном режиме, сиг- нал на входе 22 отсутствует. Суммирование осуществляется, как и в рассмотренном ранее случае, по тактам. Но операнды А и В сдвигаются на один разряд вправо и для полного суммиро- вания чисел необходимо выполнить п сдвигов регистров 1 и 2 и п+1 такт уг- мирования.

I Операнды А и В записываются последовательно младшими разрядами вперед в регистры 1 и 2 сдвига, а ре- :зультат сложения чисел фиксируется в последовательно соединенных через Элемент ИЛИ 16 регистрах 15 и 17 |:двига и также поступает младпшми.. 1|зазрядами вперед Вследствие того, iftTO общая сумма разрядов регистров 15 и 17 равна п+2, то для расположе- Йия младшего разряда результата в ijtepBOM разряде регистра 17 сдвига 4ле,цует произвести сдвиг информации ; аписанной в регистрах 15 и 17, на фдин разряд вправо, с о рмула изобретения

Последовательный сумматор, содер- Кащий с первого по пятый элементы И, «ервый одноразрядный.сумматор, первый элемент задержки, первый, второй И третий регистры сдвига, входы пер- його и второго регистров сдвига сое- ДинеШ с выходами первого и второго

элементов И, соответственно, первые входы которых объединены и подсоединены к входу разрешения приема операндов сумматора, а их вторые входы связаны соответственно с входами приема первого и второго операндов, к первым выходам первого и второго регистров сдвига подключены первые входы Третьего и четвертого элементов И соответственно, вторые входы которых соединены с входом разрешения выдачи операндов сумматора, а выходы третьего и четвертого элементов И подсоединены соответственно к первому и второму входам первого одноразрядного сумматора, с входом переноса которого через первый элемент задержки связан выход переноса первого сумматора, а его выход суммы подключен к первому входу пятого элемента И, второй вход которого соединен с входом разрешения записи суммы, вход третьего регистра сдвига соединен с выходом пятого элемента И, отличающийся тем, что, с целью расширения функциональных возможностей за счет сложения чисел в кодах с иррациональным основанием 2, в него введены четвертый регистр, шестой, седьмой и восьмой элементы И, элемент ИПИ, второй элемент задержки и второй одноразрядный сумматор, первый и второй входы которого подсоединены соответственно к выходам шестого и седьмого элементов И, первые входы которьгх соединены с вторыми выходами первого и второго регистров сдвига соответственно, вторые входы шестого и седьмого элементов И подсоединены к входу разрешения вьщачи операндов сумматора, а их третьи входы и третий вход восьмого элемента И связаны с входом режимов работы сумматора, первый и второй входы восьмого элемента И подключены соответственно к входу записи сум- матора и выходу суммы второго одноразрядного сумматора, выход переноса которого через второй элемент задержки подсоединен к входу переноса второго одноразрядного сумматора, а выход восьмого элемента И через элемент РШИ соединен с входом четвертого регистра сдвига, к которому чер ез элемент ИЛИ подсоединен также выход третьего регистра сдвига.

| Последовательный сумматор | 1983 |

|

SU1149248A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Справочник по цифровой вычислительной технике./Под ред | |||

| Б.Н.Малиновского, Киев: Техника, 1974, с | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-07-23—Публикация

1987-01-12—Подача