Изобретение относится к измерительной технике, в частности к преобразователям линейных перемещений, и может быть использовано в информационно-измерительных системах.

Цель изобретения - расширение диапазона и повышение быстродействия при1 измерении перемещений за счет выбора постоянной интегрирования.

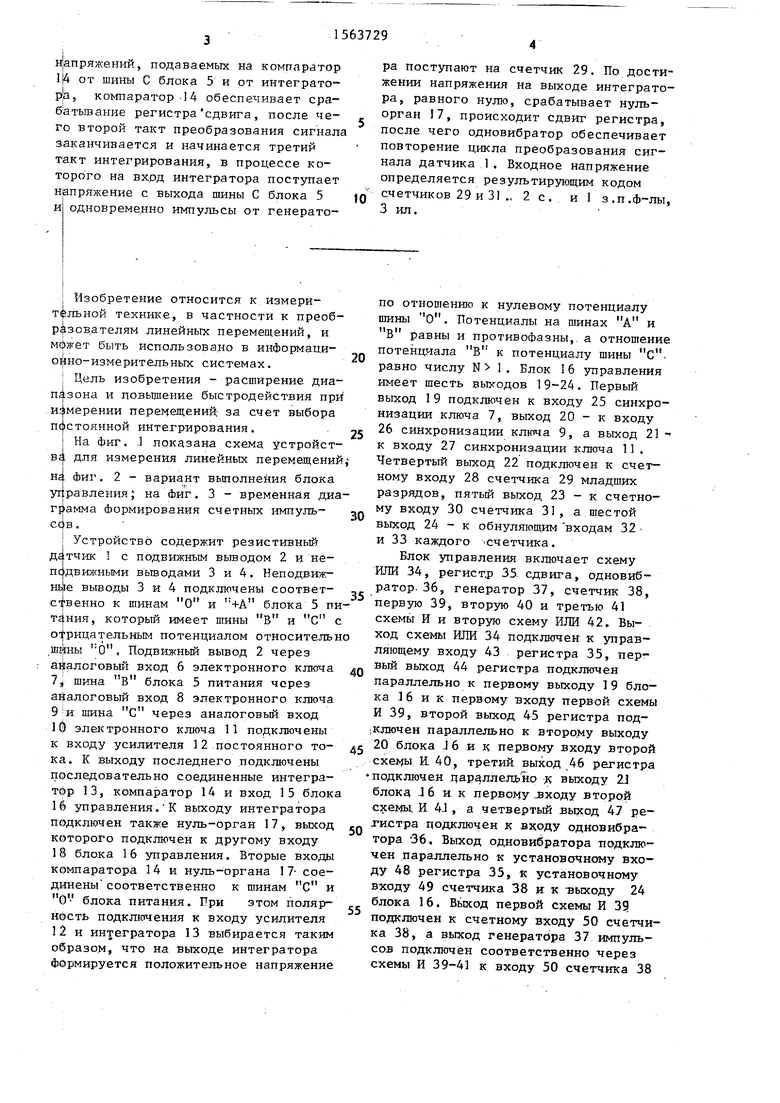

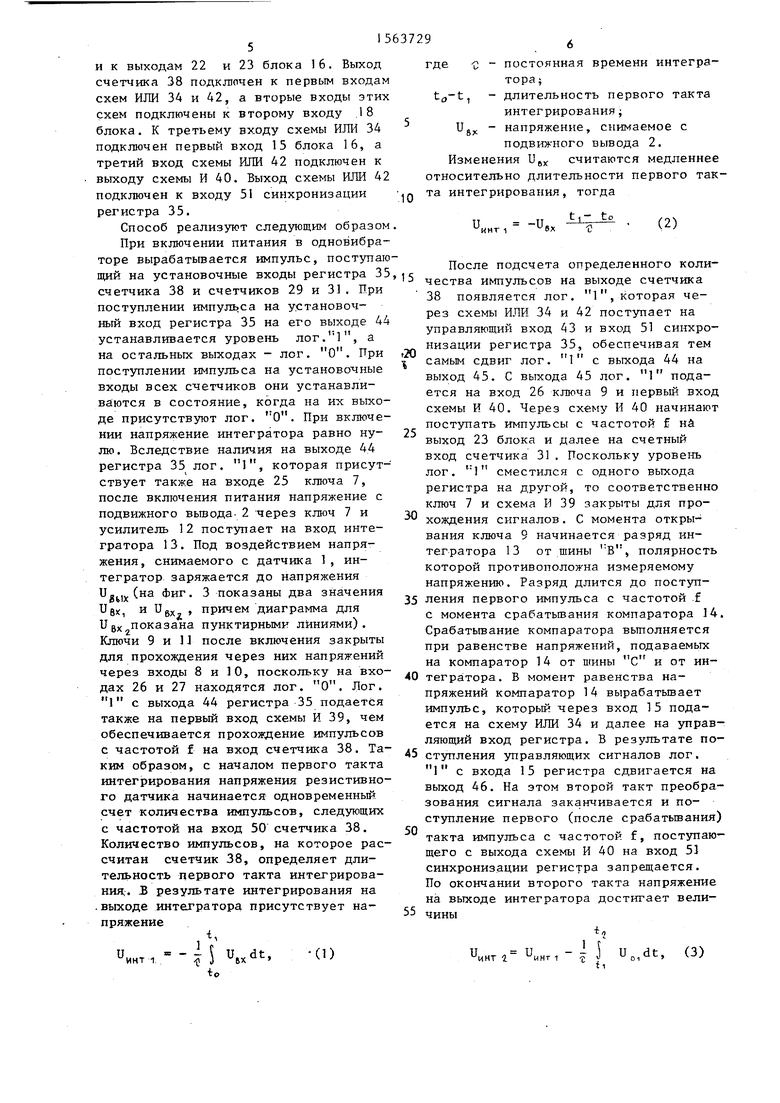

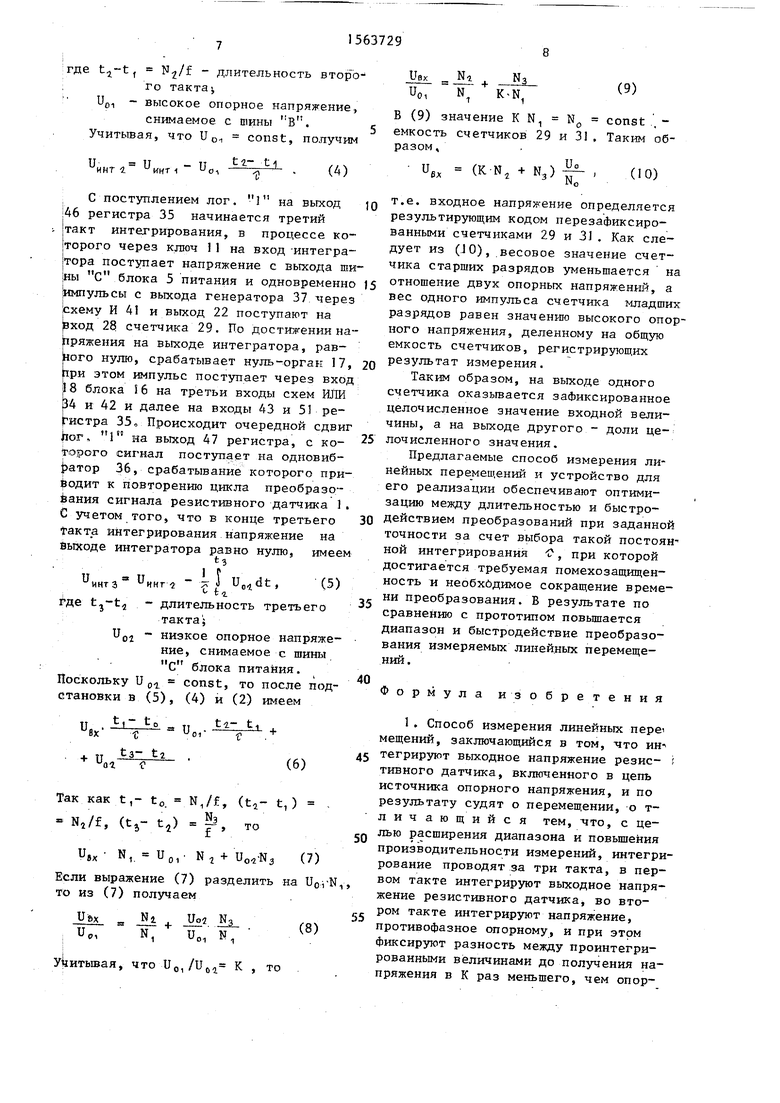

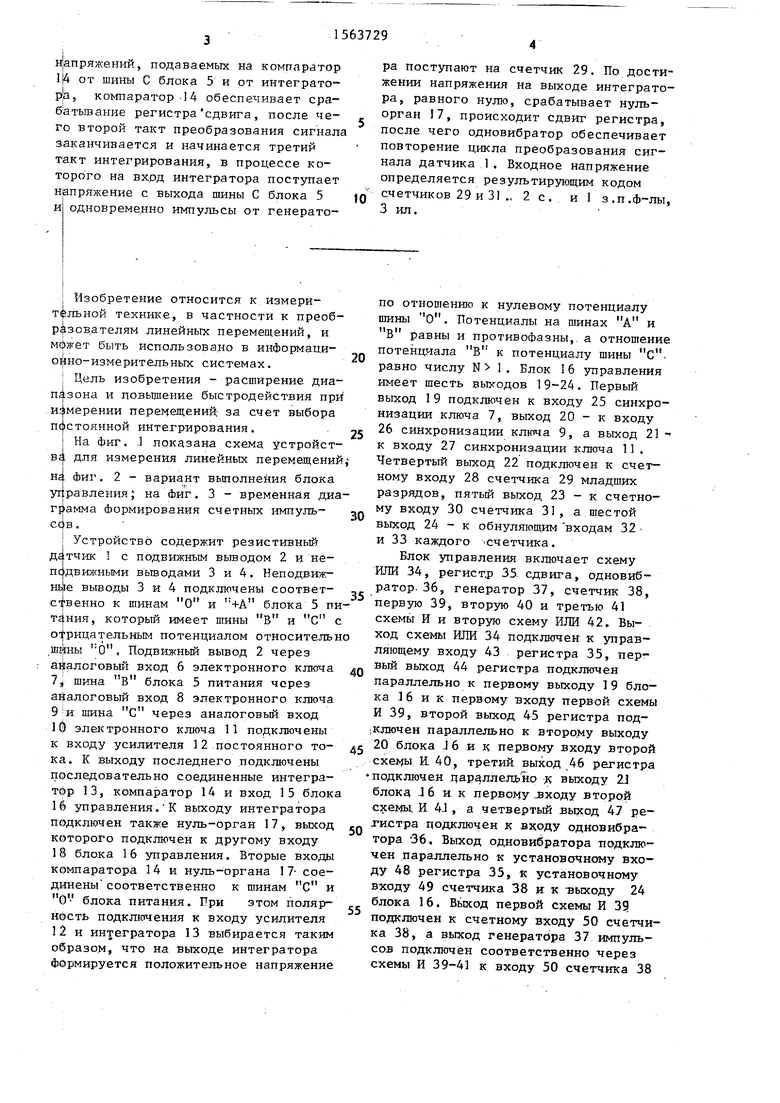

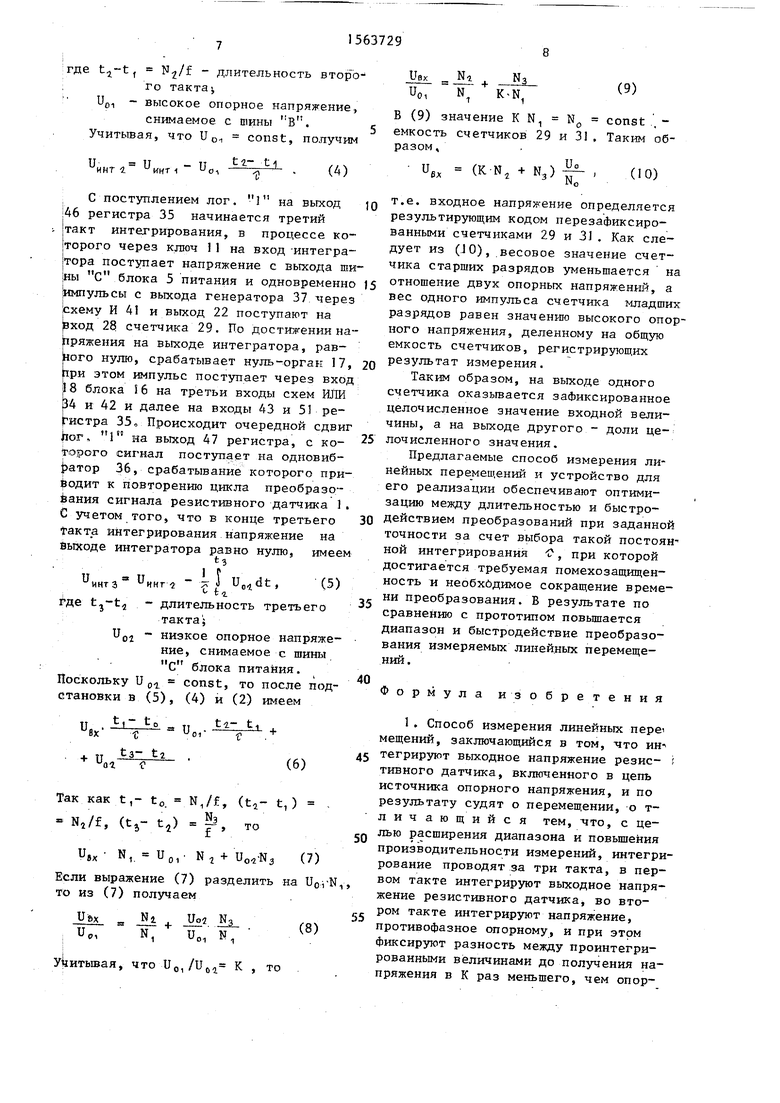

На фиг. 1 показана схема, устройства для измерения линейных перемещенийна Фиг. 2 - вариант выполнения блока управления; на Фиг. 3 - временная диаграмма формирования СЧеТНЫХ ИМПУЛЪ-

сов,

Устройство содержит резистивный датчик 3 с подвижным выводом 2 и неподвижными выводами 3 и 4. Неподвижные выводы 3 и 4 подключены соответ- ственно к шинам О и +А блока 5 питания, который имеет шины В и С с отрицательным потенциалом относительн шины |:0. Подвижный вывод 2 через аналоговый вход 6 электронного ключа 7, шина в блока 5 питания через аналоговый вход 8 электронного ключа

9и шина С через аналоговый вход

10электронного ключа 11 подключены

к входу усилителя 12 постоянного то- ка. К выходу последнего подключены последовательно соединенные интегратор 13, компаратор 14 и вход 15 блока 16 управления. К выходу интегратора подключен также нуль-орган 17, выход которого подключен к другому входу 18 блока 16 управления. Вторые входы компаратора 3 4 и нуль-органа 17- соединены соответственно к шинам С и О блока питания. При этом поляр- ность подключения к входу усилителя 12 и интегратора 13 выбирается таким образом, что на выходе интегратора формируется положительное напряжение

0

5

Q

,, 0

д5 en ,.-

по отношению к нулевому потенциалу шины О. Потенциалы на шинах А и В равны и противофазны, а отношение потенциала в к потенциалу шины С равно числу N 1. Блок 16 управления имеет шесть выходов 19-24. Первый выход 19 подключен к входу 25 синхронизации ключа 7, выход 20 - к входу 26 синхронизации ключа 9, а выход 21 к входу 27 синхронизации ключа 11. Четвертый выход 22 подключен к счетному входу 28 счетчика 29 младших разрядов, пятый выход 23 - к счетному входу 30 счетчика 31, а шестой выход 24 - к обнуляющим входам 32 и 33 каждого счетчика.

Блок управления включает схему ИЛИ 34, регистр 35 сдвига, одновибратор. 36, генератор 37, счетчик 38, первую 39, вторую 40 и третью 41 схемы И и вторую схему ИЛИ 42. Выход схемы ИЛИ 34 подключен к управляющему входу 43 регистра 35, первый выход 44 регистра подключен параллельно к первому выходу 1 9 блока 3 6 и к первому входу первой схемы И 39, второй выход 45 регистра под- .ключен параллельно к второму выходу 20 блока J 6 и к первому входу второй схемы И. 40, третий выход 46 регистра подключен параллель но к выходу 2J блока, J6 и к первому входу второй схемы И 4J, а четвертый выход 47 регистра подключен к входу одновибра- тора 36, Выход одновибратора подключен параллельно к установочному входу 48 регистра 35, к установочному входу 49 счетчика 38 и к выходу 24 блока 16. Выход первой схемы И 39 подключен к счетному входу 50 счетчика 38, а выход генератора 37 импульсов подключен соответственно через схемы И 39-41 к входу 50 счетчика 38

5

22 и 23 блока 16. Выход подключен к первым входам и 42, а вторьте входы этих

и к выходам счетчика 38 схем ИЛИ 34

схем подключены к второму входу 18 блока. К третьему входу схемы ИЛИ 34 подключен первый вход 15 блока 16, а третий вход схемы ИЛИ 42 подключен к выходу схемы И 40. Выход схемы ИЛИ 42 подключен к входу 51 синхронизации регистра 35.

Способ реализуют следующим образом

При включении питания в одновибра- торе вырабатывается импульс, поступающий на установочные входы регистра 35 счетчика 38 и счетчиков 29 и 31. При поступлении импульса на установочный вход регистра 35 на его выходе 44 устанавливается уровень лог. 1, а на остальных выходах - лог. О. При поступлении импульса на установочные входы всех счетчиков они устанавливаются в состояние, когда на их выходе присутствуют лог. О. При включении напряжение интегратора равно нулю. Вследствие наличия на выходе 44 регистра 35 лог. 1, которая присутствует также на входе 25 ключа 7, после включения питания напряжение с подвижного вывода 2 через ключ 7 и усилитель 12 поступает на вход интегратора 13. Под воздействием напряжения, снимаемого с датчика 1, интегратор заряжается до напряжения U-b|X (на Фиг. 3 показаны два значения Uex, и U,

15

причем диаграмма для

ивк. uftx-7 u.f i4его диси ciMmci ,цлп

UBX показана пунктирными линиями). Ключи 9 и 1J после включения закрыты для прохождения через них напряжений через входы 8 и 10, поскольку на входах 26 и 27 находятся лог. О. Лог. 1 с выхода 44 регистра 35 подается также на первый вход схемы И 39, чем обеспечивается прохождение импульсов с частотой f на вход счетчика 38. Таким образом, с началом первого такта интегрирования напряжения резистивно- го датчика начинается одновременный счет количества импульсов, следующих с частотой на вход 50 счетчика 38. Количество импульсов, на которое рассчитан счетчик 38, определяет длительность первого такта интегрирования;. Б результате интегрирования на выходе интегратора присутствует напряжение

i,

U

инт 1

« URX

dt,

41)

10

3729

где

; - постоянная времени интегратора;ta-t., - длительность первого такта

интегрирования; Uftx - напряжение, снимаемое с

подвижного вывода 2. Изменения Uex считаются медленнее относительно длительности первого такта интегрирования, тогда

-и

8Х

±1Г

(2)

После подсчета определенного количества импульсов на выходе счетчика 38 появляется лог. 1, которая через схемы ИЛИ 34 и 42 поступает на управляющий вход 43 и вход 51 синхронизации регистра 35, обеспечивая тем самым сдвиг лог. 1 с выхода 44 на выход 45. С выхода 45 лог. 1 подается на вход 26 ключа 9 и первый вход схемы И 40. Через схему И 40 начинают поступать импульсы с частотой f на выход 23 блока и далее на счетный вход счетчика 31. Поскольку уровень лог. 1:1 сместился с одного выхода регистра на другой, то соответственно ключ 7 и схема И 39 закрыты для прохождения сигналов. С момента открывания ключа 9 начинается разряд интегратора 13 от шины В, полярность которой противоположна измеряемому напряжению. Разряд длится до поступ- ления первого импульса с частотой f с момента срабатьюания компаратора 14. Срабатывание компаратора выполняется при равенстве напряжений, подаваемых на компаратор 14 от шины С и от интегратора. В момент равенства напряжений компаратор 14 вырабатывает импульс, который через вход 15 подается на схему ИЛИ 34 и далее на управляющий вход регистра. В результате поступления управляющих сигналов лог. 1 с входа 15 регистра сдвигается на выход 46. На этом второй такт преобразования сигнала заканчивается и поступление первого (после срабатывания) такта импульса с частотой f, поступающего с выхода схемы И 40 на вход 51 синхронизации регистра запрещается. По окончании второго такта напряжение на выходе интегратора достигает величины

л

инт 1 ин

T1-| J U0,dt, (3)

где tt-t, N2/f - длительность второ-1Uex

го такта;U0,

Jii + NI

N, K-Nl

(9)

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ измерения линейных перемещений и устройство для его осуществления | 1989 |

|

SU1670365A2 |

| Способ измерения линейных перемещений и устройство для его осуществления | 1989 |

|

SU1820198A1 |

| Электромагнитный расходомер | 1986 |

|

SU1509600A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Преобразователь выходных сигналов параметрических датчиков в код | 1986 |

|

SU1336232A1 |

| Преобразователь сигнала тензомоста в интервал времени | 1987 |

|

SU1580260A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1583757A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1991 |

|

SU1785075A1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

Изобретение относится к измерительной технике и может быть использовано в информационно-измерительных системах. Цель - расширение диапазона и повышение быстродействия при измерении перемещений за счет выбора постоянной интегрирования. После включения питания напряжение с подвижного вывода 2 через ключ 7 и усилитель 12 поступает на вход интегратора 13. Под воздействием напряжения, снимаемого с резистивного датчика 1 с подвижным выводом и неподвижными выводами, интегратор заряжается до максимального напряжения. Счетчик блока управления в период заряжения интегратора подсчитывает количество импульсов, поступающих от генератора. Количество импульсов счетчика блока управления определяет длительность первого такта интегрирования. После переполнения счетчика блока управления регистр сдвига обеспечивает прохождение импульсов в счетчик 31. С момента открывания электронного ключа 9 интегратор разряжается от шины B блока 5 питания. При равенстве напряжений, подаваемых на компаратор 14 от шины C блока 5 и от интегратора, компаратор 14 обеспечивает срабатывание регистра сдвига, после чего второй такт преобразования сигнала заканчивается и начинается третий такт интегрирования, в процессе которого на вход интегратора поступает напряжение с выхода шины C блока 5 и одновременно импульсы от генератора поступают на счетчик 29. По достижении напряжения на выходе интегратора, равного нулю, срабатывает нуль-орган 17, происходит сдвиг регистра, после чего одновибратор обеспечивает повторение цикла преобразования сигнала датчика 1. Входное напряжение определяется результирующим кодом счетчиков 29, 31. 2 с. и 1 з.п.ф-лы, 3 ил.

U01 - высокое опорное напряжение,B (g) значение к N N const

снимаемое с шины В .5 емкость счетч„ков 29 и 3J , Таким обУчитывая, что UD1 const, получим разом

U

инт

1- 01

ti- (и

(А)

С поступлением лог. I на выход 46 регистра 35 начинается третий такт интегрирования, в процессе которого через ключ 11 на вход -интегратора поступает напряжение с выхода шины С блока 5 питания и одновременно импульсы с выхода генератора 37 через схему И 41 и выход 22 поступают на вход 28 счетчика 29. По достижении напряжения на выходе интегратора, равного нулю, срабатывает нуль-орган 17, при этом импульс поступает через вход 8 блока 6 на третьи входы схем ИЛИ 34 и 42 и далее на входы 43 и 51 регистра 35 Происходит очередной сдвиг

лог, 1 на выход 47 регистра, с которого сигнал поступает на одновиб- ратор 36, срабатывание которого приводит к повторению цикла преобразования сигнала резистивного датчика 1 С учетом того, что в конце третьего такта интегрирования напряжение на

выходе интегратора равно нулю, имее

э

- U Un,dt,(5)

U.

инт з где t,-t,j

U

инт 1

I Lv u ta - длительность третьего

такта;

Uoi - низкое опорное напряжение, снимаемое с шины С блока питания.

Поскольку Uог const, то после подстановки в (5), (4) и (2) имеем

U0,ti- t1

(6)

Так как t,- t0 N,/f, (t2- t, )

N7/f, (tj- Ц)

N|

то

Uex N, - U01- N7 + (7)

Если выражение (7) разделить на Uoi N,, то из (7) получаем

NI + Uo N5

N.

Uoi N1

(8)

Учитывая, что U0,/Uca К , то

U,

(KN2 + N3) (10)

5

0

5

0

5

5

0

5

0

т.е. входное напряжение определяется результирующим кодом перезафиксированными счетчиками 29 и 31, Как следует из (JO), весовое значение счетчика старших разрядов уменьшается на отношение двух опорных напряжений, а вес одного импульса счетчика младших разрядов равен значению высокого опор- ного напряжения, деленному на общую емкость счетчиков, регистрирующих результат измерения.

Таким образом, на выходе одного счетчика оказывается зафиксированное целочисленное значение входной величины, а на выходе другого - доли це- лоч исленног о знач ения.

Предлагаемые способ измерения линейных перемещений и устройство для его реализации обеспечивают оптимизацию между длительностью и быстродействием преобразований при заданной точности за счет выбора такой постоянной интегрирования О , при которой достигается требуемая помехозащищенность и необхбдимое сокращение времени преобразования. В результате по сравнению с прототипом повышается диапазон и быстродействие преобразования измеряемых линейных перемещений.

Формула изобретения

5

0

5

0

5

0

5

0

чиков, шестой выход блока управления соединен с вторыми входами т-разряд- ных счетчиков, выходы которых являются выходами устройства, подвижный вывод резистивного датчика и отрицательные шины блока питания соединены соответственно с аналоговыми входами первого, второго и третьего электронных ключей, а нулевая и вторая отрицательная шины блока питания соединены соответственно с вторыми входами нуль-органа и компаратора.

# L.r

./

V

Pvff.3

0f/f.g

/rr&ffawuir /tffffrfe- pomopa

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-05-15—Публикация

1988-03-21—Подача