(54) УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ АСИНХРОННЫХ

КАНАЛС

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство временного уплотнения асинхронных каналов | 1976 |

|

SU610310A1 |

| Устройство для разделения асинхронных каналов | 1977 |

|

SU668098A2 |

| Многоканальное устройство синхронизации и выравнивания потоков информации | 1979 |

|

SU886018A1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1811020A1 |

| Устройство для многоканальной магнитной записи и воспроизведения сигналов с коррекцией временных искажений | 1990 |

|

SU1777178A1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1826135A1 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1126993A1 |

| Устройство для многоканальной магнитной записи и воспроизведения сигналов с коррекцией временных искажений | 1990 |

|

SU1783577A2 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ НАГРУЖЕНИЕМ ПРИ ПРОГРАММНЫХ ИСПЫТАНИЯХ МЕХАНИЧЕСКИХ КОНСТРУКЦИЙ НА УСТАЛОСТНУЮ ПРОЧНОСТЬ | 2007 |

|

RU2365963C2 |

., ,1 Изобретение относится к передаче данных. Известно устройство для разделения асинхронных каналов, содержащее последовательно соединенные первый триггер, первый элемент И и первый делитель частоты, выход которого подключен к первым входам фазового компаратора и буферного накопнтеля, второй вход которого соединен с вторым входом фазового компаратора, .а к управляющему входу первого, делнтеля частоты подключен выход генератора импульсов 1. Однако в известном .устройстве небольшой диапазон допустимых расстроек тактовых частот каналов. Цель изобретения - расширение диапазона допустимых расстроек тактовых частот каналов. Для этого в устройство для разделения асинхронных каналов, содержащее последовательно соединенные первый триггер, первый элемент И н первый делитель частоты, выход которого подключен к первым входам фазового компаратора и буферного накопителя, второй вход которого соединен с вторым входом фазового компаратора, а к управляющему входу первого делителя частоты подключен выход генератора импульсов, введены второй и третий делители частоты, второй и третий триггеры и второй, третий и четвертый элементы И. .Прн этом первый выход второго триггера подключен к первому входу второго элемента И, второй вход которого соединен с вторым входом первого элемента И н выходом второго делителя частоты, к входу которого подключён выход первого делнтеля частоты, второй и третнй входы которого соединены соответственно с выходами второго и третье)х) элементов И, а второй выход первого триггера подключен к первому входу третьего элемента И, второй вход которого соедннен с вторым выходом второго триггера первый вход которорого соединен с первым входом первого триггера и выходом четвертого элемента И, к первюму входу которого подключен выход третьего триггера, первый и второй входы которого соедннены соответственно с выходами третьего элемента И и фазового компаратора, второй выход которого подключен к второму входу четвертого элемента И, причем третнй вход третьего элемента И соединен с первым выходом третьего делителя частоты, второй выход которого подключен к второму входу буферного накопителя, третий вход которого сое- . динен с входом третьего делнтеля частоты, к управляющему входу которого подключен выход генератора импульсов, а на вторые входы первого и второго триггеров поданы импульсы синхронизации.

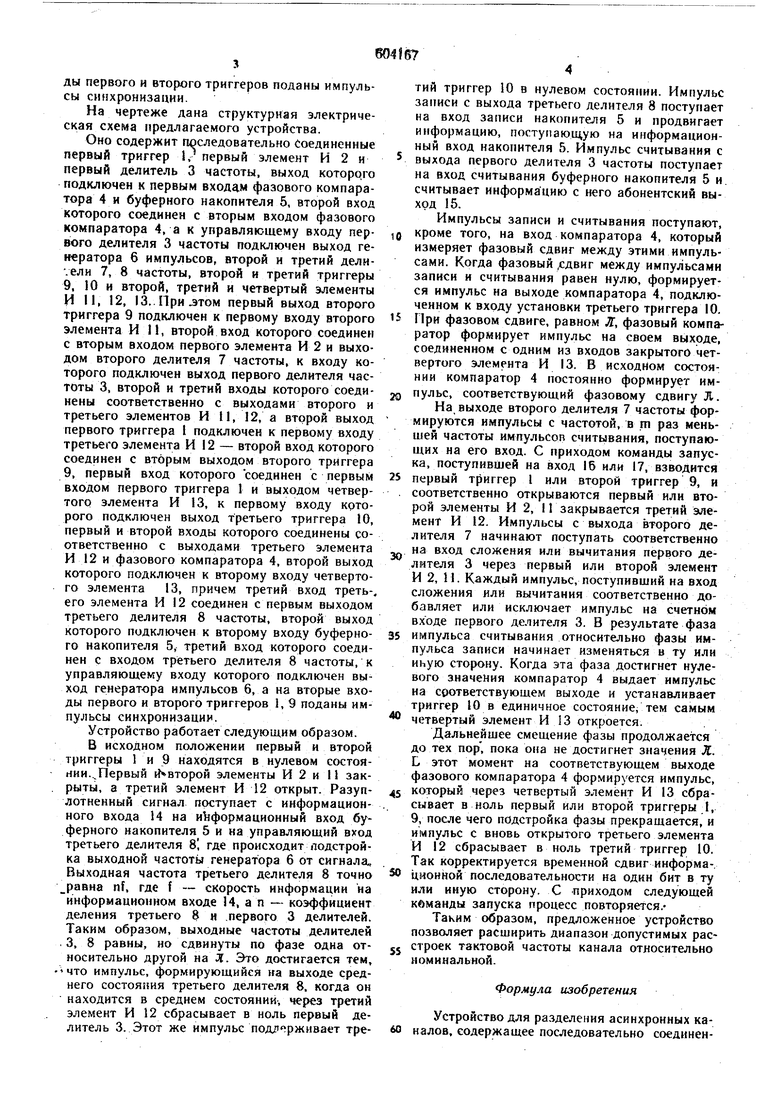

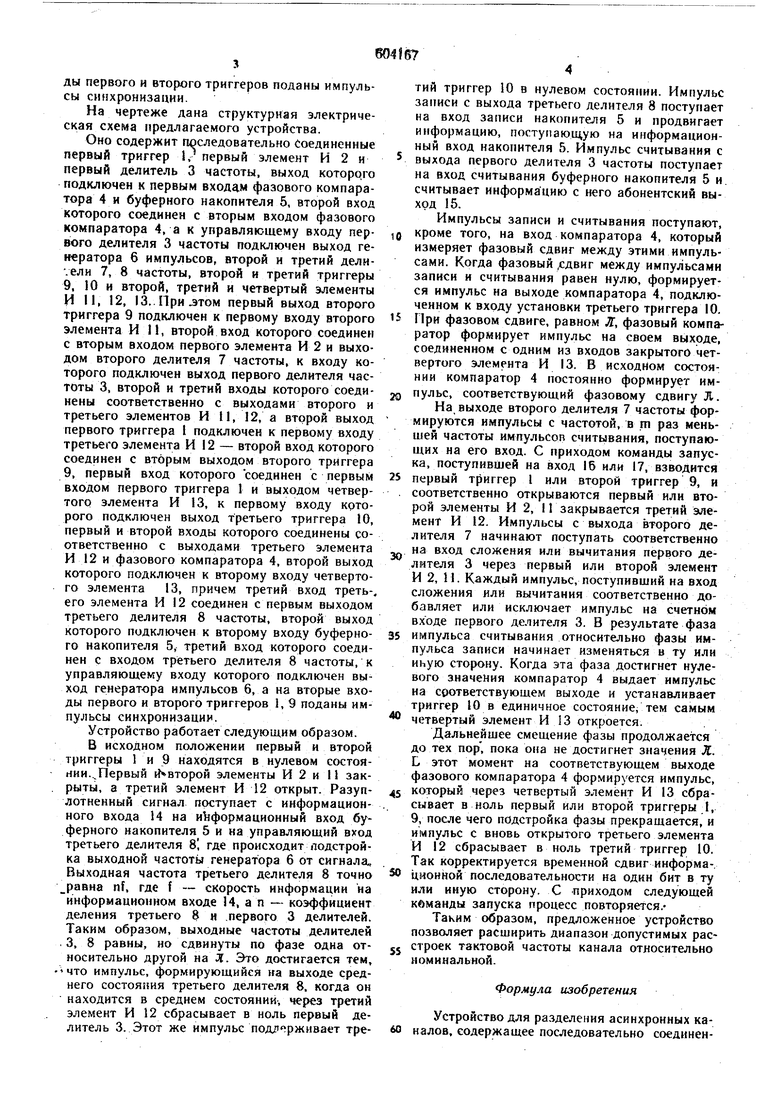

На чертеже дана структурная электрическая схема предлагаемого устройства.

Оно содержит последовательно Соединенные первый триггер К- первый элемент И 2 и первый делитель 3 частоты, выход которого подключен к первым входам фазового компаратора 4 и буферного накопителя 5, второй вход которого соединен с вторым входом фазового компаратора 4, а к управляющему входу первого делителя 3 частоты подключен выход генератора 6 импульсов, второй и третий дели.ели 7, 8 частоты, второй и третий триггеры 9, 10 и второй, третий и четвертый элементы И 11, 12, 13..При этом первый выход второго триггера 9 подключен к первому входу второго элемента И П, второй вход которого соединен с вторым входом первого элемента И 2 и выходом второго делителя 7 частоты, к входу которого подключен выход первого делителя частоты 3, второй и третий входы которого соединены соответственно с выходами второго и третьего элементов И И, 12, а второй выход первого триггера I подключен к первому входу третьего элемента И 12 - второй вход которого соединен с вторым выходом второго триггера 9, первый вход которого соединен с первым входом первого триггера 1 и выходом четвертого элемента И 13, к первому входу которого подключен выход третьего триггера 10, первый и второй входы которого соединены соответственно с выходами третьего элемента И 12 и фазового компаратора 4, второй выход которого подключен к второму входу четвертого элемента 13, причем третий вход треть-, его элемента И 12 соединен с первым выходом третьего делителя 8 частоты, второй выход которого подключен к второму входу буферного накопителя 5, третий вход которого соединен с входом третьего делителя 8 частоты, к управляющему входу которого подключен выход генератора импульсов 6, а на вторые входы первого и второго триггеров 1, 9 поданы импульсы синхронизаци 1.

Устройство работает следующим образом. В исходном положении первый и второй триггеры 1 и 9 находятся в нулевом состоянии...Первый 1| второй элементы И 2 и П зак. рыты, а третий элемент И 12 открыт. Разуплотненный сигнал поступает с информационного входа 14 на и1яформационный вход буферного накопителя 5 и на управляющий вход третьего делителя 8| где происходит подстройка выходной частоты генератора б от сигнала. Выходная частота третьего делителя 8 точно равна nf, где f - скорость информации на информационном входе 14, an - коэффициент деления третьего 8 и .первого 3 делителей. Таким образом, выходные частоты делителей .3, 8 равны, но сдвинуты по фазе одиа относительно другой на Л. Это достигается тем, что импульс, формирующийся на выходе среднего состояния третьего делителя 8. когда он находится в среднем состояний, через третий элемент И 12 сбрасывает в ноль первый делитель 3. Этот же импульс подл ржнаает третий триггер 10 в нулевом состоянии. Импульс записи с выхода третьего делителя 8 поступает на вход записи накопителя 5 и продвигает информацию, поступающую на информационный вход накопителя 5. Импульс считывания с

выхода первого делителя 3 частоты поступает на вход считывания буферного накопителя 5 и. считывает информацию с него абонентский выход 15.

Импульсы записи и считывания поступают,

j кроме того, на вход компаратора 4, который измеряет фазовый сдвиг между этими импульсами. Когда фазовый усдвиг между импульсами записи и считывания равен нулю, формируется импульс на выходе компаратора 4, подключенном к входу установки третьего триггера 10.

При фазовом сдвиге, равном Л, фазовый компаратор формирует импульс на своем выходе, соединенном с одним из входов закрытого четвертого элемента И 13. В исходном состоянии компаратор 4 постоянно формнрует импульс, соответствующий фазовому сдвигу Л. На выходе второго делителя 7 частоты формируются импульсы с частотой, в ш раз меньщей частоты импульсов считывания, поступающих на его вход. С приходом команды запуска, поступивщей на вход 16 или 17, взводится

5 первый триггер I или второй триггер 9, и . соответственно открываются первый или второй элементы И 2, II закрывается третий элемент И 12. Импульсы с выхода второго делителя 7 начинают поступать соответственно

на вход сложения или вычитания первого делителя 3 через первый или второй элемент И 2, 11. Каждый импульс, поступивший на вход сложения или вычитания соответственно добавляет или исключает импульс на счетном входе первого делителя 3. В результате фаза

5 импульса считывания относительно фазы импульса записи начинает изменяться в ту или иную сторону. Когда эта фаза достигнет нулевого значения компаратор 4 выдает импульс иа соответствующем выходе и устанавливает триггер 10 в единичное состояние, тем самым

четвертый элемент И 13 откроется.

Дальнейшее смещение фазы продолжается до тех пор , пока она не достигнет значения Л. L этот момент на соответствующем выходе фазового компаратора 4 формируется импульс,

5 который через четвертый элемент И 13 сбрасывает в ноль первый или второй триггеры 1, 9, после чего подстройка фазы прекращается, и импульс с вновь открытого третьего элемента И 12 сбрасывает в ноль третий триггер 10. Так корректируется временной сдвиг информа-. 50 ционной последовательности на один бит в ту или иную сторону. С -приходом следующей к манды запуска процесс повторяется.Таким образом, предложенное устройство позволяет расширить диапазои допустимых рас55 строек тактовой частоты канала относительно номинальной.

Формула изобретения

Устройство для разделения асинхронных ка60 налов, содержащее последовательно соединенные первый триггер, первый элемент И и первый делитель частоты, выход которого подключен к первым входам фазового компаратора и буферного накопителя, второй вход которого соединен с вторым входом фазового компаратора, а к управляющему входу первого делителя частоты подключен выход генератора импульсов, отличающееся тем. что, с целью расширения диапазона допустимых расстроек тактовых частот каналов, введены второй и третий делители частоты, второй и третий триггеры и второй, третий и четвертый элементы И, при этом первый выход Второго триггера подключен к первому входу второго элемента И, второй вход которого соединен с вторым входом первого элемента И и выходом второго делителя частоты, к входу которого подключен выход первого делителя частоты, второй и третий входы которого соединены соответственно с выходами второго и третьего элементов И, а второй выход первого триггера подключен к первому входу третьего элемента И, второй вход которого соединен с вторым выходом второго триггера, первый вход которого соединсн с первым входом первого .триггера н выходом четвертого элемента И, к первому входу которого подключен выход третьего триггера, первый и второй входы которого соединены соответственно с выходами третьего элемента И и фазового компаратора, второй выход которого подключен к второму входу четвертого элемента И, причем третий вход третьего элемента И соединен с первым выходом третьего делителя частоты, второй выход которого подключен к второму входу буферного накопителя, третий вход которого соединен с входом третьего делителя частоты, к упрйвляющему входу которого подключен выход генератора импульсов, а на вторые входы первого и второго триггеров поданы импульсы синхронизации.

Источники информации, принятые во внимание при экспертизе:

I. Авторское свидетельство № 415815, М.кл2 Н 04 J 1/16, 1974.

Авторы

Даты

1978-04-25—Публикация

1976-05-25—Подача