каналов введены четыре дополнительных элемента If, буферный накопитель, инвертор, второй элемент ИЛИ, два триггера и фазовый компаратор, выход которого подключен к первым входам первого и второго элементов И, вторые входы которых соединены с выходами коммутатора, третий вход которого соединен с выходом второго элемента ИЛИ и с первыми входами первого и второго триггеров, ко вторым входам которых подключены соответственно выходы первого и второго элементов И, при этом выходы первого триггера соединены с первыми входами первого и второго дополнительных элементов И, вторые-входы которых соединены со вторым выходом формирователя кадров и вторыми входами третьего и четвертого дополнительных элементов И, к первым входам которых подключен первый выход второго триггера, второй выход которого соединен с третьим входом первого дополнительного элемента И, а дополнительный выход регистра сдвига подключен к третьему входу третьего дополнигельного элемента И и ко входу инвертора, выход которого соединен с третьим входом четвертого дополнительного элемента Л, причем выхоВ5й второго, третьего и четвертого дополнительных элементов И подключены ко входам второго элемента ИЛИ и блока кодироваиня, соответствующий вход которого соеsiHHefl с выходом, первого дополнительного глемента И, а выход первого элемента ИЛИ через буферный накопитель подключен ко второму входу узла объединения, при этом первый выход формирователя кадров подключен к первому.входу фазового компаратора, второй вход которого соединен с выходом формирователя вн ульсов записи.

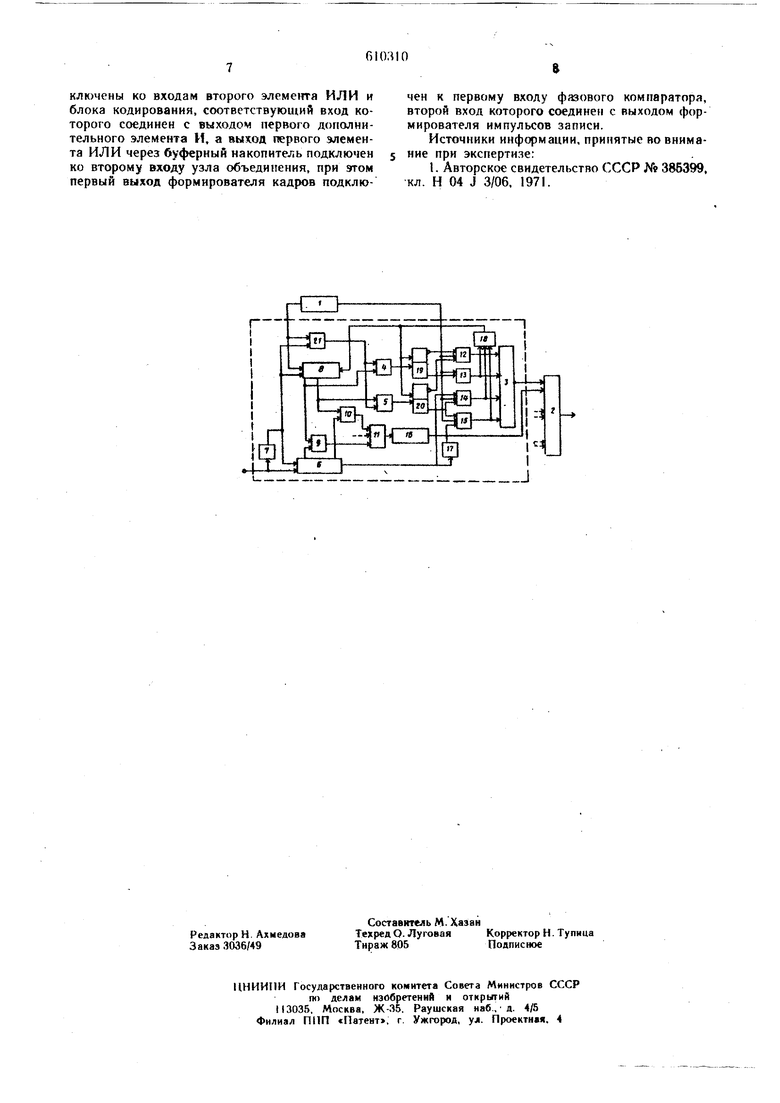

На чертеже представлена структурная электрическая схема устройства временного уплот«ения асинхронных каналов.

Устройство временного уплотнения асинхронных каналов содержит общие для всех каналов формирователь кадров и узел объединения 2, а также в каждом канале блок кодирования 3, выход которого подключен к первому входу узла объединения 2, два элемента И 4, 5, регистр сдвига б, первый вход которого соединен со входом формирователя импульсов записи 7, выход которого подключен к первому входу коммутатора 8 и ко второму входу регистт pa сдвига 6, выходы которого соединены с первыми -входами элементов коммутации 9, 10, ко вторым входам которых подключены выходы коммутатора 8, второй вход которого соединен с первым выходом формирователя кадров i, а выходы элемент-ов коммутации 9, 10 подключены ко входам первого элемента ИЛИ ИГ; четыре дополнительных элемента И 12, 13, 14, 15, буферный накопитель 16, инвертор 17, второй элемент ИЛИ 18, два триггера 19, 20 и фазовый компаратор 21, выход которого подклю 1ен к первым входам первого и второго элементов И 4, 5, вторые входы которых соединены с выходами коммутатора 8, третий вход которого соединен с выходом второго элемента ИЛИ 18 и с первыми входами первого и второго триггеров 19, 20, ко вторым входам которых

подключены соответственно выходы первого и второго элементов И 4, 5, при этом выходы первого триггера 19 соединены с первыми входами первого и второго дополнительных элементов И 12, 3, вторые входы которых соединены со вторым выходом формирователя кадров 1 . и вторыми входами третьего и четвертого дополнительных элементов И 14, 15, к первым входам которых подключен первый выход второго триггера 20, второй выход которого соединён с третьим входом первого дополнительного элемента И 12, а дополнительный выход регистра сдвига б подключен к третьему входу третьего дополнительного элемента И 14 и ко входу инвертора 17, выход которого соединен с третьим входом четвертого дополнительного элемента И 15, причем выходы второго, третьего и четвертого дополнительных элементов И 13, 14, 15 подключены ко входам второго элемента ИЛИ 18 и блока кодирования 3, соответствующий вход которого соединен с выходом первого дополнительного элемента И 12, а выход пер-вого элемента ИЛИ 11 через буферный накопитель 16 подключен ко второму входу узла объединения 2, при этом первый выход формирователя кадров 1 подключен к первому входу фазового компаратора 21, второй вход которого соединен с выходом формирователя импульсов записи 7.

Устройство временного уплотнения асинхронных каналов работает следующим образом.

Устройство формирует кадр передачи, в котором каждому асинхронному каналу отводится свой временной интервал. Границы кадров отмечены импульсом начала кадра. Этот импульс вырабатывается формирователем кадров I. Формирователь кадров состоит из задающего кварцевого генератора, делителей частоты и распределителей импульсов. Информация от каждого асинхронного канала поступает на информационный вход регистра .сдвига 6 и на вход формирователя импульсов записи 7, в котором из сигнала выделяется тактовая частота. Импульсы выделенной тактовой частоты поступают на вход регистра сдвига 6 и продвигают информацию по регистру, а также поступают на вход сложения коммутатора 8, где каждый импульс записи переводит коммутатор 8 в следующее по старшинству положение. Импульсы считывания от формирователя кадров 1 с частотой, равной номинальной скорости информации на входе устройства временного уплотнения асинхронных каналов, поступают на вход вычитания коммутатора 8 и переводят «го в предыдущее по старщинству положение. В исходном состоянии мэммутатор 8 находится в среднем положении и включает соответствующий элемент коммутации 9 или 10, через который происходит считывани значений информационных символов из среднего разряда регистра сдвига 6 и запись этих значений через первый элемент ИЛИ II в буферный накопитель 16. Если канальная частота записи на входе сложения равна частоте импульсов считывания на входе вычитания коммутатора 8, то коммутатор 8 находится в среднем состоянии, и считывание информации происходит со среднего разряда регистра сдвига 6. Если частота записи превысит частоту сч итывания, то коммутатор 8 начинает смещаться в сторону старшего положения, и считывание информации iipo исходит уже с другого соответствующего разряда регистра сдвига 6. Если частота импульсов записи меньше частоты импульсов считывания, то смещение считывания происходит в сторону младшего разряда регистра сдвига 6. Когда коммутатор 8 достигает младшего или старшего положений, то включается первый или второй элемент И 4, 5 соответственно, и импульс от фазового компаратора 21 взводит триггер 19 или 20. Импульс на выходе фазового компаратора 21 формируется только в случае сдвига фаз между импульсами записи и импульсами считывания на его входах на Я. Таким образом, взведение триггеров 19 и 20 происходит только в случае достижения сдвига фаз между импульсами записи и считывания, равного /СЯ, где К- 1,2,... Удобно принять УС I. Импульс начала кадра от формирователя кадров 1 опрашивает все четыре дополнительных элемента И 12, 13, 14, 15. Когда оба триггера 19 и 20 находятся в нулевом состоянии, включен первый дополнительный эле мент И 12. Если триггер 19 находится в единичном состоянии, включен второй дополнительный элемент И 13. Если триггер 20 находится в единичном состоянии, включен третий дополнительный элемент И 14 или четвертый, дополнительный элемент И 15 в зависимости от состояния среднего разряда регистра сдвига 6. Очевидно, что оба триггера в единичном состоянии одновременно находиться не могут. С приходом опрашивающего импульса начала кадра на выходе включенног;о дополнительного элемента И появляется сигнал, по которому в блоке кодирования 3 формируется соответствующий код. Импульс на выходе дополнительного элемента И 13 означает, что в информационную последовательное«ь вставлен лищний бит из-за отрицательного рассог: ласования частот записи и считывания. Импульс на выходе дополнительного элемента И 14 означает, что в информационной последовательности пропущен бит со значением «1, а импульс на выходе дополнительного элемента И .15 означает, что пропущен бит со значением «О из-за положительного рассогласоваНИН частот записи и считывания. Импульсы с выходов дополиительных элементов И 13, 14,. 15 через второй элемент ИЛИ 18 сбрасывают триггеры 19 и 20 в нулевое состояние, а коммутатор 8 устанавливают в среднее положение. В отсутствии импульсов на выходах дополнительных элементов И 13, 14, 15 формируются импульсы на выходе дополнительного элемен та И 12 по каждому импульсу начала кадра. В соответствующий временной шггервал, определяемый формирователем кадров 1, код стаффннга из блока кодирования 3 и содержимое буфериого накопителя 16 через узел объединеиня 2 выводятся в групповой канал. Коды, формируемые блоком кодирования 3, должны обладать хорршими взаимокорреляциониыми свойствами, кроме того, желательно, чтобы код, формируемый от импульса первого лопо.шительного элемента И, обладал хорошими автокорреляционными свойствами, что поз1кугясг использовать его в качестве кода кадровой синх-ро шзации. Таким образом, анализ отклонения положения коммутатора 8 от средноч) в сторону младшего или старшего положений позволяет использовать асинхронные источники с любым знаком отклонения их тактовых ча :тот от номинальных, т. е. расширяет диапазон допустимых расстроек тактовой частоты канала относительно номинальной. Использонлние в качестве кода кадровой синхронизации кода отсутствиястаффинга в одном из каналов позволяет исключить специальный BpeivfeHHorf интервал в кадре под код кадровой синхронизации, что повышает эффективность использования пропускной способности группового канала. Формула J зoбpeтeнuя Устройство временного уплотнения асинхронных каналов, содержащее общие для всех каналов формирователь кадров и узел объединения, а также в каждом канале блок кодирования, выход которого подключен к первому входу узла объединения, два элемента И, регистр сдвига, первый вход которого соединен со входом формирователя импульсов записи, выход которого подключен к первому входу коммутатора и ко второму входу регистра сдвига, выходы которого соединены с первыми входами элементов коммутации, ко вторым входам которых подключены выходы коммутатора, второй вход которого соединен с первым выходом формирователя кадров, а выходы элементов коммутации подключеиы ко входам первого элемента ИЛИ, отличающееся тем, что, с целью расширения диапазона допустимых расстроек тактовых частот уплотняемых каналов. в каждый из каналов введены четыре дополнительных элемента И, буферный накопитель, инвертор, второй элемент ИЛИ, два триггера и фазовый компаратор, выход которого подключен к первым входам первого и второго элементов И, вторые входы которых соединеиы с выходами коммутатора, третий вход которого соединен с выходом второго элемента ИЛИ- и с первыми входами первого и второго триггеров, ко вторым входам которых подключены соответственно выходы первого и второго элементов И, при этом выходы первого триггера соединены с первыми входами первого и второго дополнительных .дшементов И, вторые входы которых соединены со вторым выходом формирователя кадров и вторыми входами третьего и четвертого дополиительных элементов И, к первым входам которых подключен первый выход второго триггера, второй.выход которого соединен с третьим входом первого дополнительного элемента И, а дополнительный выход регистра сдвига подключен к третьему вхо-, ду третьего дополнительного элемента И и ко входу инвертора, выход которого соединен с третьим входом четвертого дополнительного элемента И, причем выходы второго, третьего и четвертого дополнительиых элементов И подключены ко входам второго элрме1тта ИЛИ и блока кодирования, соответствующий вход которого соединен с выходом первого дополнительного элемента И, а выход первого элемента ИЛИ через буферный накопитель подключен ко второму входу узла объединения, при этом первый выход формирователя кадров подключен к первому входу фазового компаратора, второй вход которого соединен с выходом формирователя импульсов записн.

Источники информации, принятые во внимание при экспертизе:

I. Авторское свидетельство СССР Я 386399, кл. Н 04 J 3/06, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разделения асинхронных каналов | 1977 |

|

SU668098A2 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| Устройство для разделения асинхронных каналов | 1976 |

|

SU604167A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для асинхронного сопряжения цифровых потоков | 1986 |

|

SU1312556A1 |

| Многоканальное устройство синхронизации и выравнивания потоков информации | 1979 |

|

SU886018A1 |

| УСТРОЙСТВО ПРИЕМА И ПЕРЕДАЧИ ФАЗОМАНИПУЛИРОВАННЫХ КОДОВЫХ СИГНАЛОВ | 2002 |

|

RU2236086C2 |

| Устройство для распознавания контуров изображений | 1983 |

|

SU1156103A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| УСТРОЙСТВО ВРЕМЕННОГО УПЛОТНЕНИЯ АСИНХРОННЫХ | 1973 |

|

SU385399A1 |

Авторы

Даты

1978-06-05—Публикация

1976-05-25—Подача