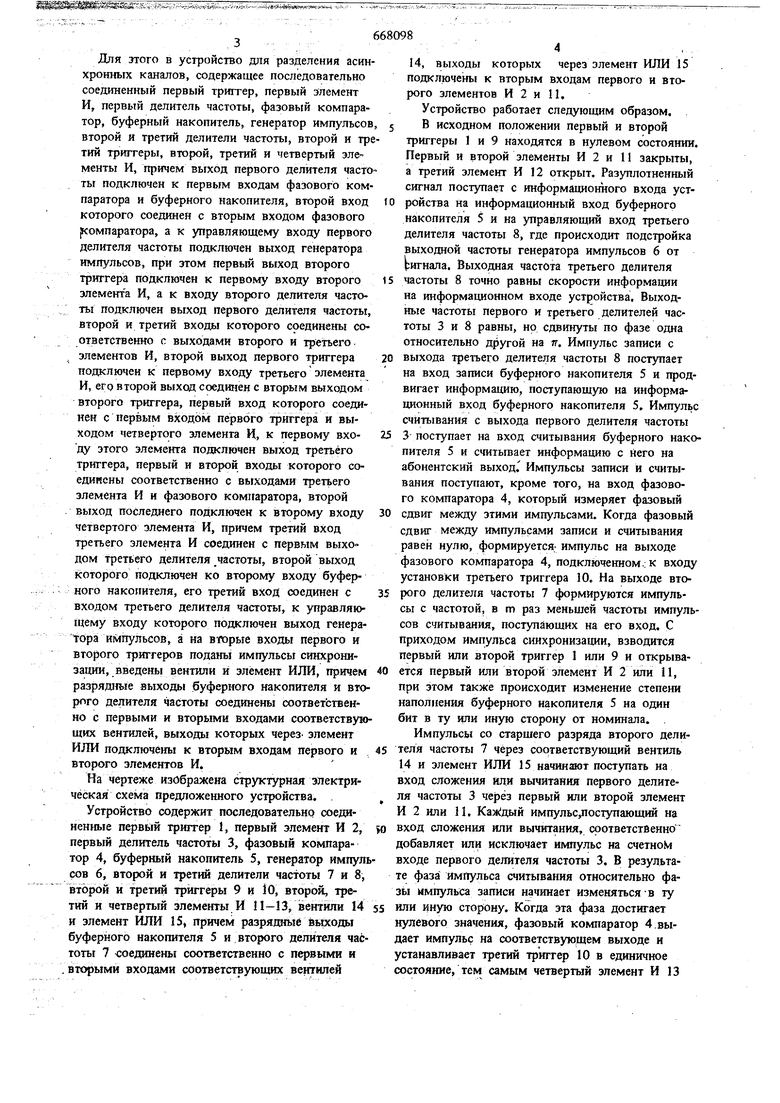

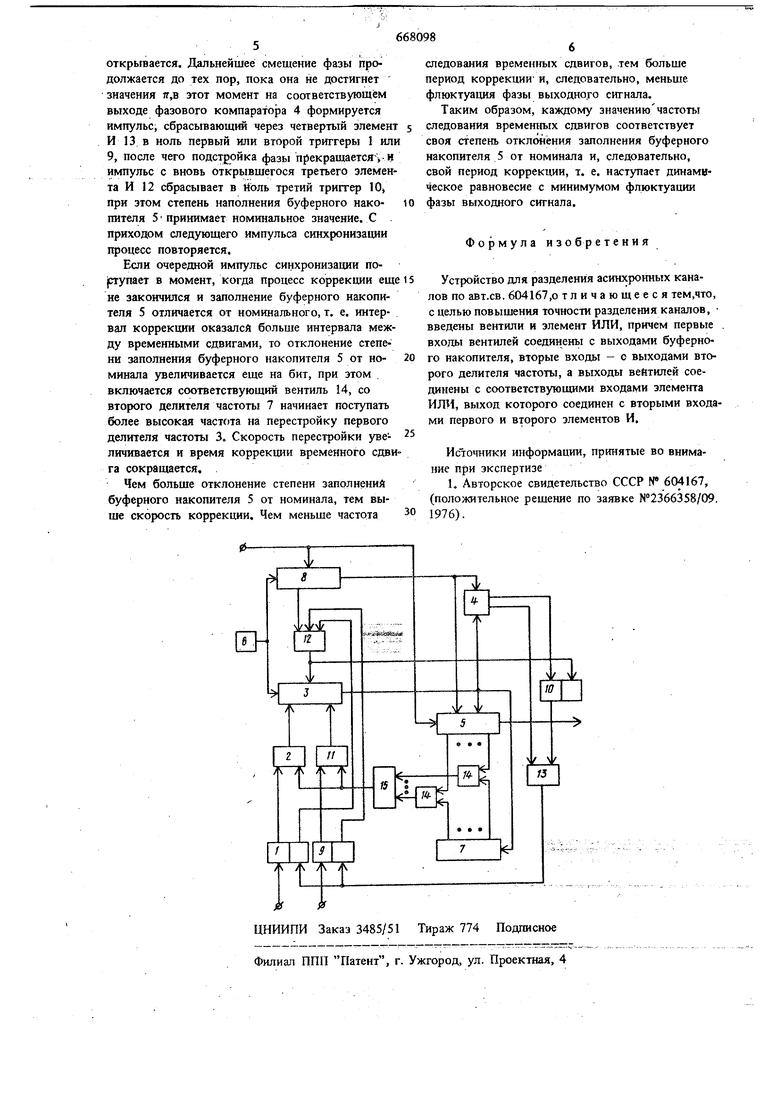

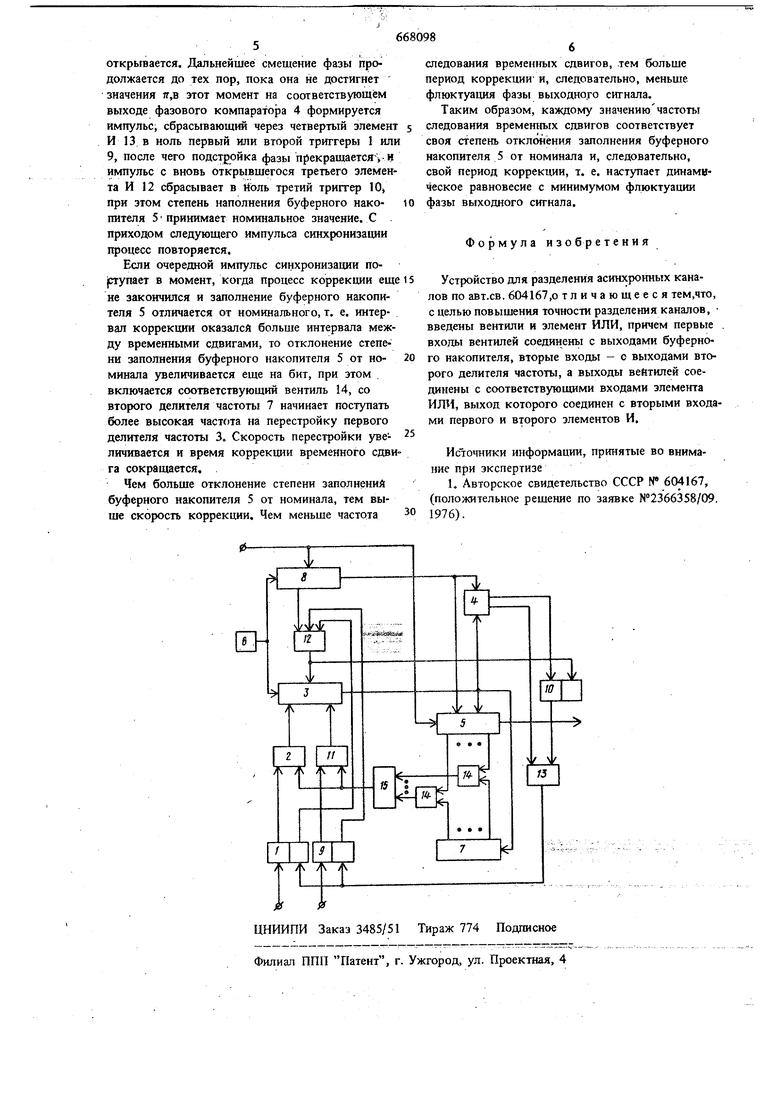

Для этого в устройство для разделения асинхронных каналов, содержащее последовательно соединенный первый триггер, первый элемент И, первый делитель частоты, фазовый компаратор, буферный накопитель, генератор импульсов второй и третий делители частоты, второй и тре тий триггеры, второй, третий и четвертый элементы И, причем выход первого делителя частО ты подключен к первым входам фазового компаратора и буферного накопителя, второй вход которого соединен с вторым входом фазового компаратора, а к управляющему входу первого делителя частоты подключен выход генератора импульсов, при зтом первый выход второго триггера подключен к первому входу второго элемента И, а к входу второго делителя частоты подключен выход первого делителя частоты, второй и третий входы которого соединены соответственно с выходами второго и третьего, элементов И, второй выход первого триггера подключен к первому входу третьего элемента И, его второй выход соединен с вторым выходом второго триггера, первый вход которого соединен с первым входблс первого триггера и выходом четвертого элемента И, к первому входу этого элемента подключен выход третьего триггера, первый и второй входы которого соединены соответственно с выходами третьего элемента И и фазового компаратора, второй выход последнего подключен к второму входу четвертого элемента И, причем третий вход третьего элемента И соединен с первым выходом третьего делителя частоты, второй выход которого подключен ко второму входу буферного накопителя, его третий вход соединен с входом третьего делителя частоты, к управляющему входу которого подключен выход генераtOpa импульсов, а на вгорые входы первого и второго триггеров поданы импульсы синхронизации, введены вентили и элемент ИЛИ, причем разрядные выходы буферного накопителя и второго делителя частоты соединены соответственно с первыми и вторыми входами соответствующих вентилей, выходы которых через- элемент ИЛИ подключит. к вторым входам первого и второго элементов И. На чертеже изображена структурная электрическая схема предложенного устройства. Устройство содержит последовательно соединенные первый триггер 1, первый элемент И 2, первый делитель частоты 3, фазовый компаратор 4, буферный накопитель 5, генератор импуль сов 6, второй и третий делители частоты 7 и 8, второй и третий триггеры 9 и Ю, второй, третий и четвертый элементы И II-13, 1вентили 14 и элемент ИЛИ 15 причем разрядап ё вьрсоды буферного накопителя 5 и второго делителя частоты 7 :оединены соответственно с первыми и .вторыми входами соответствующих вентилей 14, выходы которых через элемент ИЛИ 15 подключены к вторым входам первого и второго элементов И 2 и П. Устройство работает следующим образом. В исходном положении первый и второй триггеры 1 и 9 находятся в нулевом с:остоянин. Первый и второй элементы И 2 и 11 закрыты, а третий элемент И 12 открыт. Разуплотненный сигнал поступает с информадионного входа устройства на информационный вход буферного накопителя 5 и на управляющий вход третьего делителя частоты 8, где происходит подстройка выходной частоты генератора импульсов 6 от ригнала. Выходная частота третьего делителя частоты 8 точно равны скорости информации на информационном входе устройства. Выходные частоты первого и третьего делителей частоты 3 и 8 равны, но сдвинуты по фазе одна относительно другой на гг. Импульс записи с выхода третьего делителя частоты 8 поступает на вход записи буферного накопителя 5 и продвигает информацию, поступающую на информационный вход буферного накопителя 5. Импульс считывания с выхода первого делителя частоты 3- поступает на вход считывания буферного накопителя 5 и считывает информацию с него на абонентский выход. Импульсы записи и считывания поступают, кроме того, на вход фазового компаратора 4, который измеряет фазовый сдвиг между этими импульсами. Когда фазовый сдвга между импульсами записи и считывания равен нулю, формируется; импульс на выходе фазового компаратора 4, подключенном.: к входу установки третьего триггера 10. На выходе второго делителя частоты 7 формируются импульсы с частотой, в m раз меньшей частоты импульсов считывания, поступающих на его вход. С приходом импульса синхронизации, взводится первый или второй триггер 1 или 9 и открывается первый или второй элемент И 2 или И, при этом также происходит изменение степени наполнения буферного накопителя 5 на один бит в ту или иную сторону от номинала. Импульсы со старщего разряда второго делителя частоты 7 через соответствующий вентиль 14 и элемент ИЛИ 15 начинают поступать на вход сложения или вычитания первого делителя частоты 3 через первый или второй злемент И 2 или 11. Каж;дый импульс,поступающий на вход сложения или вычитания, соответственно добавляет или исключает импульс на счетном входе первого делителя частоты 3. В результате фаза Импульса считывания относительно фазы импульса записи начинает изменяться-в ту или иную сторону. Когда эта фаза достигает нулевого значения, фазовый компаратор 4.выдает импульс на соответствующем выходе и устанавливает третий триггер 10 в единичное состояние, тем самым четвертый элемент И 13

открывается. Дальнейшее смещение фазы продолжается до тех пор, пока она не достигнет значения тт,ъ этот момент на соответствующем выходе фазового компаратора 4 формируется импульс, сбрасывающий через четвертый элемент И 13 в ноль первый или второй триггеры 1 или 9, после чего подстройка фазы прекращается -и импульс с вновь открывщегося третьего элемента И 12 сбрасывает в йоль третий триггер 10, при этом степень наполнения буферного накопителя 5 принимает номинальное значение. С приходом следующего импульса синхронизации процесс повторяется.

Если очередной импульс синхронизации портупает в момент, когда процесс коррекции еще не закончился и заполнение буферного накопителя 5 отличается от номинального, т. е. интервал коррекции оказалсй больше интервала между временными сдвигами, то отклонение степени заполнения буферного накопителя 5 от номинала увеличивается еще на бит, при этом включается соответствующий вентиль 14, со второго делителя частоты 7 начинает поступать более высокая частота на перестройку первого делителя частоты 3, Скорость перестройки увеличивается и время коррекции временного сдвига сокращается.

Чем больще отклонение степени заполнений буферного накопителя 5 от номинала, тем выше скорость коррекции. Чем меньще частота

следования временных сдвигов, тем больще период коррекции и, следовательно, меньще флюктуация фазы выходного сигнала.

Таким образом, каждому значениючастоты следования времешп.1х сдвигов соответствует своя степень отклонения заполнения буферного накопителя 5 от номинала и, следовательно, свой период коррекции, т. е. наступает динамическое равновесие с минимумом флюктуации фазы выходного сигнала.

Формула изобретения

Устройство для разделения асинхронных каналов по авт.св. 604167,0 тличающееся тем,что, с целью повышения точности разделения каналов, введены вентили и элемент ИЛИ, причем первые входы вентилей соединеньг с выходами буферного накопителя, вторые входы - с выходами второго делителя частоты, а выходы вентилей соединены с соответствующими входами элемента ИЛИ, выход которого соединен с вторыми входами первого и второго элементов И,

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР N 604167, (положительное решение по заявке №2366358/09 1976).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разделения асинхронных каналов | 1976 |

|

SU604167A1 |

| Устройство временного уплотнения асинхронных каналов | 1976 |

|

SU610310A1 |

| Устройство для многоканальной магнитной записи и воспроизведения сигналов с коррекцией временных искажений | 1990 |

|

SU1777178A1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1826135A1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1811020A1 |

| Многоканальное устройство синхронизации и выравнивания потоков информации | 1979 |

|

SU886018A1 |

| Устройство для многоканальной магнитной записи и воспроизведения сигналов с коррекцией временных искажений | 1990 |

|

SU1783577A2 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Ультразвуковой измеритель перемещений | 1989 |

|

SU1619027A1 |

| Устройство для многоканальной магнитной записи и воспроизведения сигналов с коррекцией временных искажений | 1990 |

|

SU1818636A1 |

Авторы

Даты

1979-06-15—Публикация

1977-10-26—Подача