Устройство относитсяк передаче информации и может использоваться в адаптивных системах телеметрии, связи, фототелеграфии и телевидения для передачи многоканальных сообщений с дельта-модуляцией повышенной помехоустойчивости. Известно многоканальное устройство для передачи информации с дельта-модуляцией, содержащее в каждом из N каналов первый элемент И и второй элемент И, выходы которых подключены к входам элемента ИЛИ и вычитающий элемент, выход которого подключен к одному из входов троичного модулятора, выход которого через интегратор подключен к одному из входов вычитающего элемента, а также общие для всех каналов блок памяти, синхронизатор, блок формирования адресов, сумматор и двоичный модулятор, выход которого подключен к первому входу сумматора, к второму входу которого подключен первый выход блока формирования адресов, второй и третий выходы которого подключены к соответствующим входам двоичного модулятора, причем второй выход блока формирования адресов подключен к первому входу первого элемента И каждого из N каналов, второй вход которого и первый вход второго элемента И соединены с соответствующим выходом блока памяти, к входам которого подключены выходы троичных модуляторов соответствующих каналов, первый, выход синхронизатора подключен к другому входу вычитающего элемента каждого из X каналов и к дополнительному вхо ду блока памяти, второй выход синхронизатора подключен к другому входу троичного модулятора каждого из К каналов и к первому дополнительному входу блока формирования адресов, второй дополнительный вход которого соединен с третьим выходом синхронизатора, соединенным с другим входом второго элемента И каждого из N каналов 1J. Однако в известном устройстве имеет место малая степень уплотнения информации при ак-. тивизации ее источников. Цель изобретения увеличение скорости передачи информации. Для этого в многоканальное устройство для передачи информации с дельта-модуляцией, содержащее в каждом из N каналов первый элемент И и второй элемент И, выходы которых подключены к входам элемента ИЛИ, и вычитающий элемент, выход которого подключен к одному из входов троичного модулятора, выход которого через интегратор подключен к одному из входов вычитающего элемента, а также общие для всех каналов блок памяти.

синхронизатор, блок формирования адресов, сумматор и двоичный модулятор, выход которого подключен к первому входу сумматора, ко второму входу которого подключен первый выход блока формирования адресов, второй и третий выходы которого подключены к соответствующим входам двоичного модулятора, причем второй выход блока формирования адресов подключен к первому входу первого элемента И каждого из N каналов, второй вход которого и первый вход BTOpuO элемента И соединены с соответствующим выходом блока памяти, к входам которого подключены выходы троичных модуляторов соответствующих каналов, первый выход синхронизатора подключен к другому входу вычитающего элемента каждого из N каналов и к дополнительному входу блока памяти, второй выход синхронизатора подключен к другому входу троичного модулятора каждого из N каналов и к первому дополнительному входу блока формирования адресов, второй дополнительный вход которого соединен с третьим выходом синхронизатора, соединенным с другим входом второго элемента И каждого из -N каналов, в каждый из N каналов, кроме первого, введены последовательно соединеннью элемент НЕТ, элемент НЕ и третий элемент И, а также введены общие для всех каналов последовательно соединенные регистр сдвига, счетчик и блок формирования кода числа каналов, элемент задержки, дополнительный элемент НЕ и блок формирования маркера кадра, при этом в каждом из N. каналов, кроме первого, один из входов элемента НЕТ и другой вход третьего элемента И подключены к выходу элемента ИЛИ, выход каждого из элементов НЕТ и выход элемента ИЛИ первого канала подключены к соответствующим входам блока формирования адресов, другой вход элемента НЕТ каждого из N-1 каналов подключен к выходу элемента ИЛИ предыдущего канала, выходы третьих элементов И каждого из N-1 каналов- подключены к соответствующим входам регистра сдвига, к дополнительному входу которого подключен четвертый выход синхронизатора, выход блока формирования кода числа каналов подключен к третьему входу сумматора, к четвертому входу которого подключен первый выход синхронизатора через блок формирования маркера кадра, выход регистра сдвига через последовательно соединенные дополнительный элемент НЕ и элемент задержки подключен к второму входу счетчика, к третьему входу которого и к входу синхронизатора подключен выход дополнительного элемента НЕ.

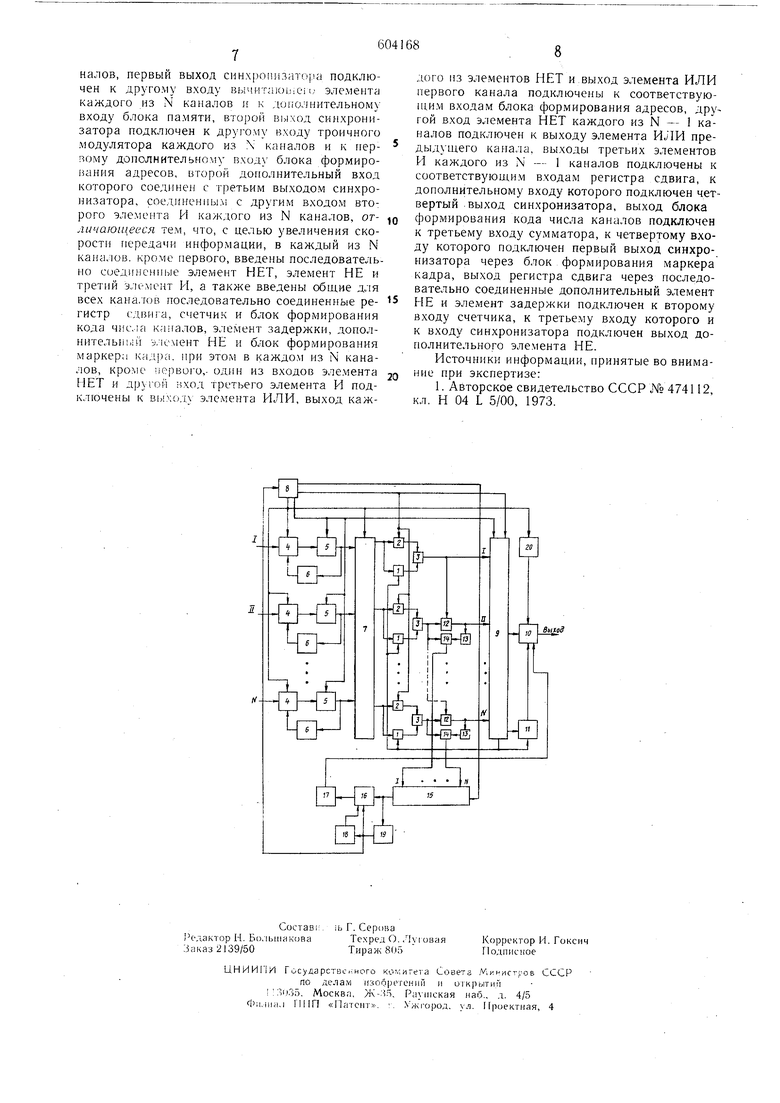

На чертеже дана структурная электрическая схема предлагаемого устройства.

Многоканальное устройство для передачи информации с дельта-модуляцией, содержит в каждом из N каналов первый элемент И 1 и второй элемент И 2, выходы которых подключены к входам элемента ИЛИ 3, и вычитающий элемент 4, выход которого подключен к одному из входов троичного модулятора 5, выход которого через интегратор 6 подключен к одному из входов вычитающего элемента 4, а также общие для всех каналов блок 7 памяти, синхронизатор 8, блок 9 формирования адресов, сумматор 10 и двоичный модулятор 11, выход которого подключен к первому входу сумматора 10, ко второму входу которого Подключен первый выход блока 9, второй и третий выходы которого подключены к соответствующим входам двоичного модулятора 11, причем второй выход блока 9 подключен к первому входу первого элемента И 1 каждого rt3N каналов, второй вход которого и первый вход второго элемен-та И 2 соединены с соответствующим выходом блока 7, к входам которого подключены ВЫХОД троичных модуляторов 5 соответствующих каналов, первый выход синхронизатора 8 подключен к другому входу вычитающего элемента 4 каждого из N каналов и к дополнительному входу блока 7, второй выход

синхронизатора 8 подключен к другому входу троичного модулятора 5 каждого из N каналов и к первому дополнительному входу блока 9 формирования адресов, второй дополнительный вход которого соединен с третьим выходом синхронизатора 8, соединенным с другим входом второго элемента И 2 каждого из N каналов, последовательно соединенные элемент НЕТ 12, элемент НЕ 13 и третий элемент И 14, а также введены общие для всех каналов последовательно соединенные регистр 15 сдвига, счетчик 16 и блок 17 формирования кода числа каналов, элемент 18 задержки, дополнительный элемент НЕ 19 и блок 20 формирования маркера кадра, при этом в каждом из N каналов, кроме первого, один из входов элемента НЕТ 12 и другой вход третьего элемента И 14 подключены к выходу элемента ИЛИ 3, выход каж дого из элементов НЕТ 12 и выход элемента ИЛИ 3 первого канала подключены к соответствующим входам блока 9, другой вход элемента- НЕТ 12 каждого из N - 1 каналов подключён к выходу элемента ИЛИ 3 предыдущего

канала, выходы третьих элементов И 14 каждого из N - 1 каналов подключены к соответствующим входам регистра 15 сдвига, к дополнительному входу которого подключен четвертый выход синхронизатора 8, выход блока

17 формирования кода числа каналов подключен к третьему входу сумматора 10, к четвертому входу которого подключен первый выход синхронизатора 8 через блок 20, выход регистра 15 через последовательно соединенные до.полнительный элемент НЕ 19 и элемент задержки 18 подключен к второму входу счетчика 16, к третьему входу которого и к входу синхронизатора 8 подключен выход дополнительного элемента НЕ 19.

Устройство работает следующим образом. Исходный аналоговый сигнал в каждом из N каналов поступает на вход вычитающего элемента 4, соединенного с троичным модулятором 5, в котором формируется сигнал разности между исходным сигналом и сигналом аппроксимации, вырабатываемым интегратором 6, Указанный разностный сигнал в троичной форме поступает на соответствующий вход блока памяти 7. Синхронизм одновременного формирования разностного сигнала в троичной форме по всем N каналам достигается подачей соответствующих импульсов на входы вычитающих элементов 4 и троичных модуляторов 5 с первых двух выходов Синхронизатора 8. В каждый период опроса (дискретизации) одновременно с запуском вычитающих элементов 4 также происходит сброс блока 7 памяти в исходное состояние. В зависимости от амплитуды исходного сигнала на. каждом из N выходов блока 7 может присутствовать один из трех типов сигналов: высокий, низкий и нулевой. Так как нулевой сигнал соответствует избыточной выборке, то он в канал связи не передается. Это достигается подключением к каж дому выходу блока 7 второго элемента И 2 и первого элемента И 1. По окончании записи информации в блок 7 с третьего выхода синхронизатора 8 подается импульс считывания на все N вторых элементов И 2, при этом одновременно импульсный сигнал появляется на выходах элементов ИЛИ 3 только тех каналов, в которых исходный сигнал имеет положительный знак приращения. Импульсный сигнал с выхода элемента ИЛИ 3 первого канала поступает на вход блока 9 формирования адресов, с первого выхода которого код адреса первого канала через сумматор 10 поступает на выход устройства. Одновременно с этим процессом импульсный сигнал с выхода элемента ИЛИ 3 первого канала поступает на запрещающий вход элемента НЕТ 12 второго канала, тем самым запрещая прохождение, импульсного сигнала с выхода элемента ИЛИ 3 второго канала на вход блока 9 формирования адресов. Но, благодаря наличию элемента НЕ 13, импульсный сигнал через третий элемент И 14 записывается в первый разряд регистра 15 сдвига. Этот же импульсный сигнал с выхода элемента ИЛИ 3 второго канала поступает на запрещающий вход элемента НЕТ 12 третьего канала. Однако даже и при открытом этом элементе в блоке 9 формирования адреса треть,его канала не произойдет, так как всоответствии с указанным примером на выходе элемента ИЛИ третьего канала импульсный сигнал отсутствует. Кроме того, не будет записан сигнал и во второй разряд регистра 15 сдвига. Отсутствие импульсного сигнала на выходе элемента ИЛИ 3 третьего канала не препятствует прохождению сигнала от анало.гичного элемента четвертого канала в блок 9 формирования адресов. Процесс одновременной записи сигналов от остальных каналов в регистр 15 сдвига и блок 9 происходит описанным выще образом. После окончания пер§й:одиых процессов в схеме устройства синхронизатор 8 с четвертого выхода начинает выдавать сдвигак/щие импульсы в регистр 15 сдвига, счетчик 16 при этом фиксирует количество идущих подряд «единиц (для нащего примера одну). При появлении сигнала «О на выходе регистра 15 с выхода дополнительного элемента НЕ 19 подается импульс считывания в счетчик 16. Сформированный код числа подряд идущих каналов с выхода блока 17 формирования кода через сумматор 10 выдается в линию связи. Одновременно с этим сигнал с выхода дополнительного элемента НЕ 19 временно прекращает подачу управляющих сигналов с выхода синхронизатора 8 в блок 9. Этот же сигнал, пройдя через элемент 18 задержки, устанавливает счетчик 16 в нулевое состояние. После окончания формирования кода адреса последнего (старщего по номеру) канала или кода числа подряд идущих каналов с указанным знаком приращения со второго выхода блока 9 формирования адресов на первый вход двоичного модулятора 11 поступает сигнал формирования информационного символа «1, который также через сумматор 10 вслед за кодами адресов поступает в канал связи. Кроме того, управляющий сигнал с того же выхода блока 9 поступает в качестве импульса считывания одновременно на все N первые элементы И 1, и процесс формирования кодов адресов и. числа подряд идущих каналов, в которых исходная функция имеет отрицательный знак приращения, происходит изложенным выще образом. По окончании формирования этих кодов и выдачи их в канал связи с третьего выхода блока 9 в двоичный модулятор 11 поступает сигнал на формирование символа «О. Под воздействием сигнала с первого выхода синхронизатора 8 в блоке 20 формируется код маркера кадра, который следует в начале кадоа и служит на приемной стороне сигналом синхронизации. Предложенное устройство по сравнению с известным позволяет увеличить скорость передачи информации. Формула изобретения Многоканальное устройство для передачи информации с дельта-модуляцией, содержащее в каждом из N каналов первый элемент И и второй э 1-емент И, выходы которых подключены к входам элемента ИЛИ, и вычитающий элемент, выход которого подключен к одному из входов.троичного модулятора, выход которого через интегратор подключен к одному из входов вычитающего элемента, а также общие для всех каналов 6vTOK памяти, синхронизатор, блок формирования адресов, сумматор и двоичный модулятор, выход которого подключен к первому входу сумматора, ко второму входу которого подключен первый выход блока формирования адресов, второй и третий выходы которого подключены к соответствующим входам двоичного модулятора, причем второй выход блока формирования адресов подключен к первому входу первого элемента И каждого из N каналов, второй вход которого и первый вход второго элемента И соединены с соответствующим выходом блока памяти, к входам которого подключены выходы троичных модуляторов соответствующих каналов, первый выход синх)011изато| а подключен к другому входу Bbi4HT;i)oi:iCi i; эле.мента каждого из N каналов it к лополнительному входу блока памяти, второй В111ход синхронизатора подключен к другому входу троичного модулятора каждого из Х каналов и к первому дополнительному входу блока формирования адресов, второй дополнительный вход которого соединен с третьим выходом синхронизатора, соединен 1Пз1.м с другим входом второго элемента И каждого из N каналов, отличаюп(ееся тем, что, с целью увеличения скорости передачи информации, в каждый из N каналов, кроме первого, введены последовательно соединенные элемент НЕТ, элемент НЕ и третий элемент И, а также введены общие для всех кана.юв последовательно соединенные регистр сдвига, счетчик и блок формирования кода .ia каналов, э;1емент задержки, дополнителыилн у/юмент НЕ и блок формирования маркера )а. при этом в каждом нз N каналов, кроме iiepBoio,- один из входов эле.мента НЕТ и другой нход третьего элемента И подключены к элемента ИЛИ, выход каждого нз элементов НЕТ и,выход элемента ИЛИ первого канала подключены к соответствуюН1ИМ входам блока формирования адресов, другой вход элемента НЕТ каждого из N - 1 каналов подключен к выходу элемента ИЛИ предыдуц его канала, выходы третьих элементов И каждого из N - 1 каналов подключены к соответствующим входам регистра сдвига, к дополнительному входу которого подключен четвертый выход синхронизатора, выход блока

формирования кода числа каналов подключен к третьему входу сумматора, к четвертому входу которого подключен первый выход синхронизатора через блок формирования маркера кадра, выход регистра сдвига через последовательно соединенные дополнительный элемент НЕ и элемент задержки подключен к второму входу счетчика, к третьему входу которого и к входу синхронизатора подключен выход дополнительного элемента НЕ.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР №474112, кл. Н 04 L 5/00, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство дляпЕРЕдАчи иНфОРМАции C дЕльТА- МОдуляциЕй | 1979 |

|

SU849271A1 |

| Многоканальное устройство для передачи информации с дельта-модуляцией | 1982 |

|

SU1166330A1 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1145357A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2039365C1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2344544C2 |

| Устройство синхронизации источников сейсмических сигналов | 1991 |

|

SU1787278A3 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1996 |

|

RU2099739C1 |

| Ранговый обнаружитель сигналов | 1981 |

|

SU970291A1 |

Авторы

Даты

1978-04-25—Публикация

1975-12-12—Подача