Изобретение относится к радиотехнике и может использоваться в аппаратуре передачи дискретной информации.

Из основного авт. св. № 526898 известно устройство дпя исправления ошибок в кодовой комбинации, содержащее однопороговуюи двухпороговую схемы, соединенные с входом устройства, сумматор по модулю два, один вход.которогО соединен с выходом бпока формирования полиномов ошибок, другой

вход через последовательно соединенные буферный и основной блоки памяти - с выходом однопороговой схемы, а выход подключен к первому входу элемента И, блок обнаружения ошибок, первый выход

которого соединен с выходом устройства, второй - со вторым выходом элемента И, выход элемента И соединен со вторым выходом устройства, а выход двухпороговоЙ схемы соединен с первым входом блока

формирования полиномов ошибок, второй вход которого соединен со вторым выходом блока обнаружения ошибок, выход сумматор по модулю два соединен со входом блока обнаружения ошибок.

Цель изобретения - увеличение быстродействия устройства.

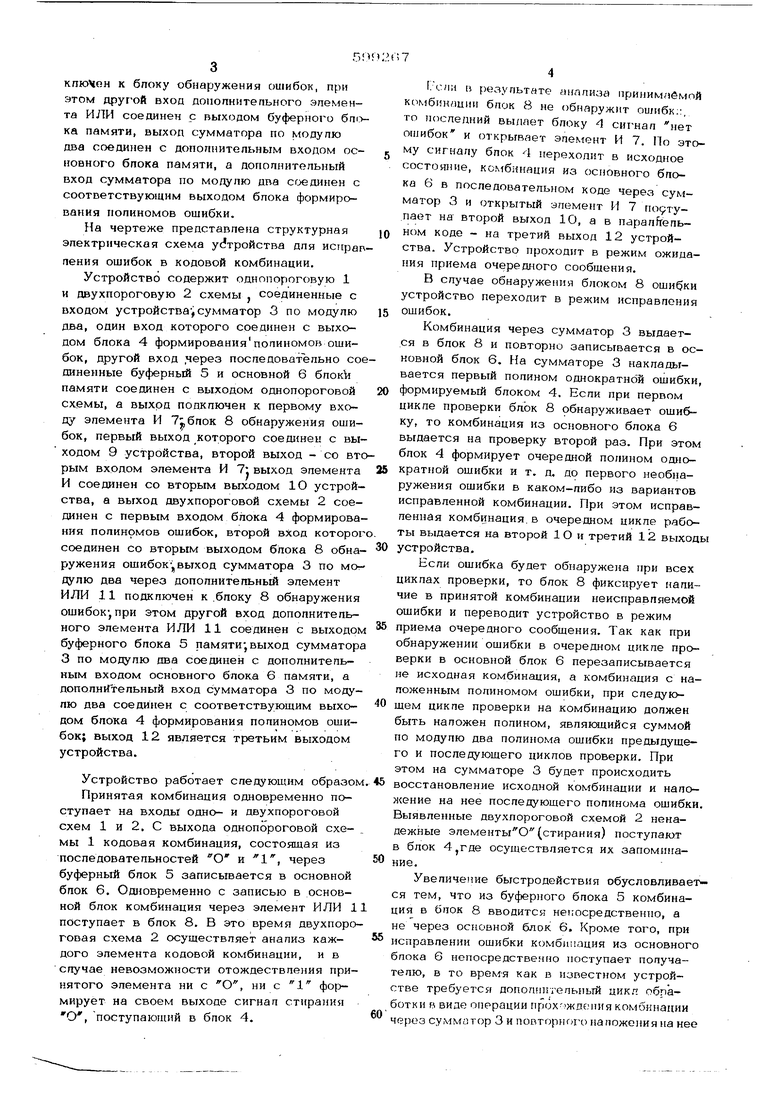

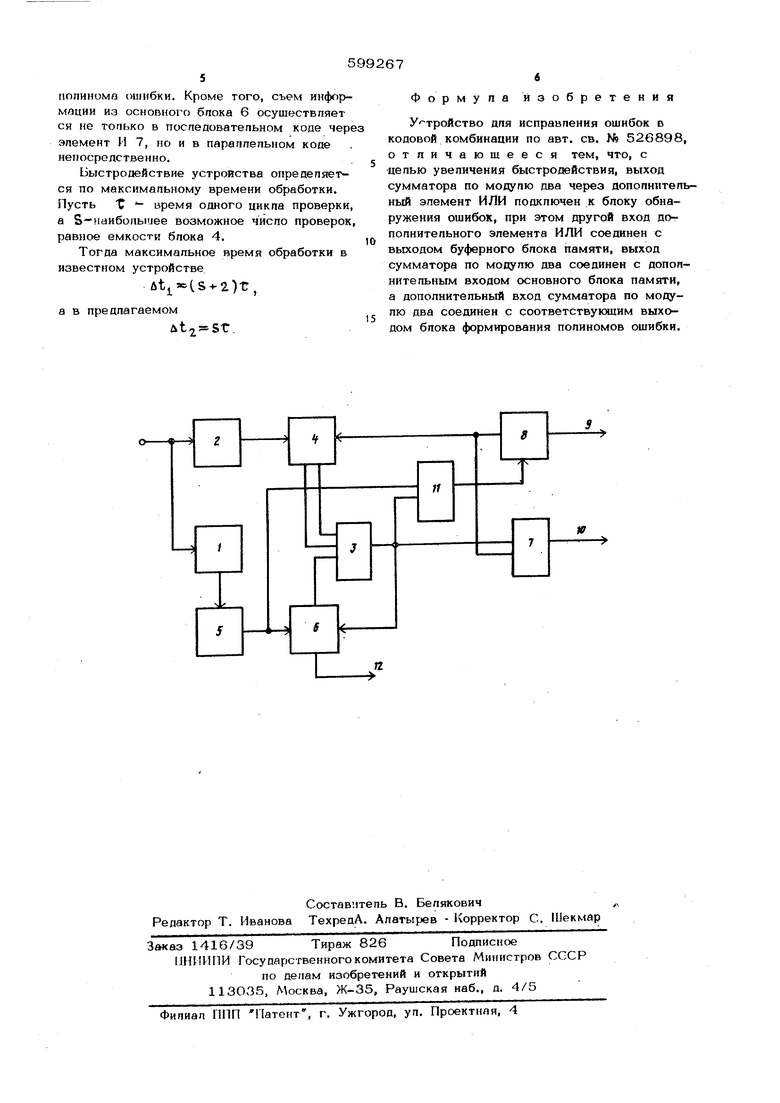

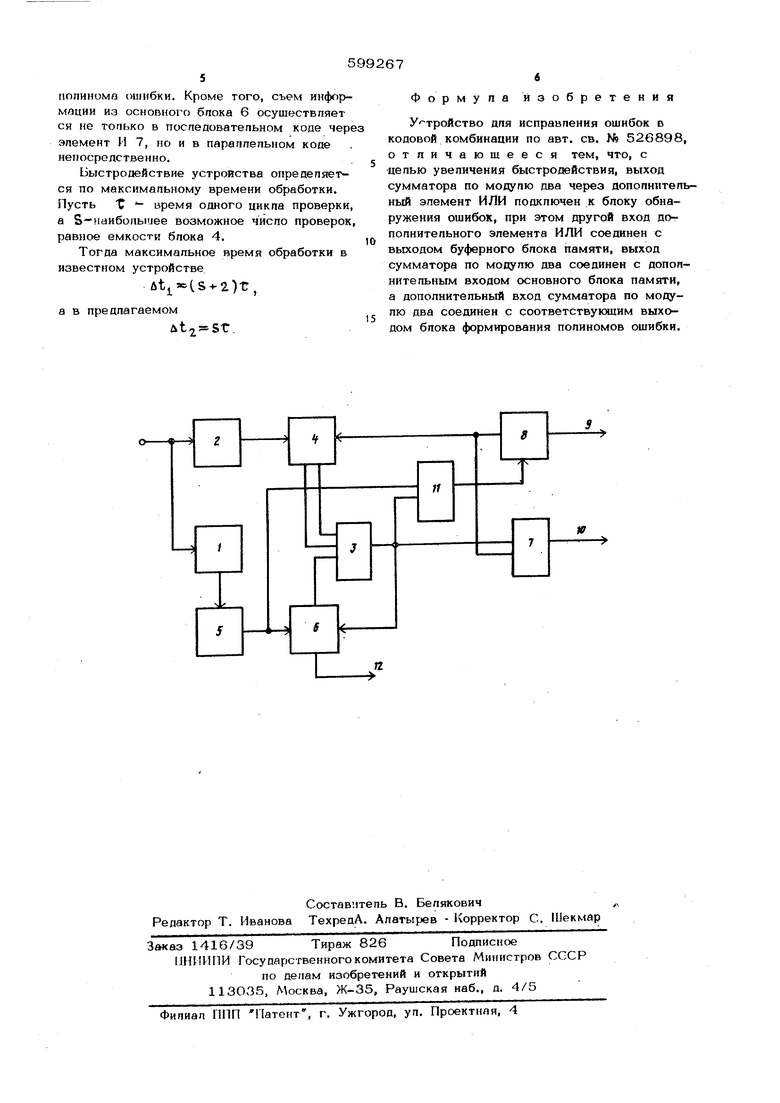

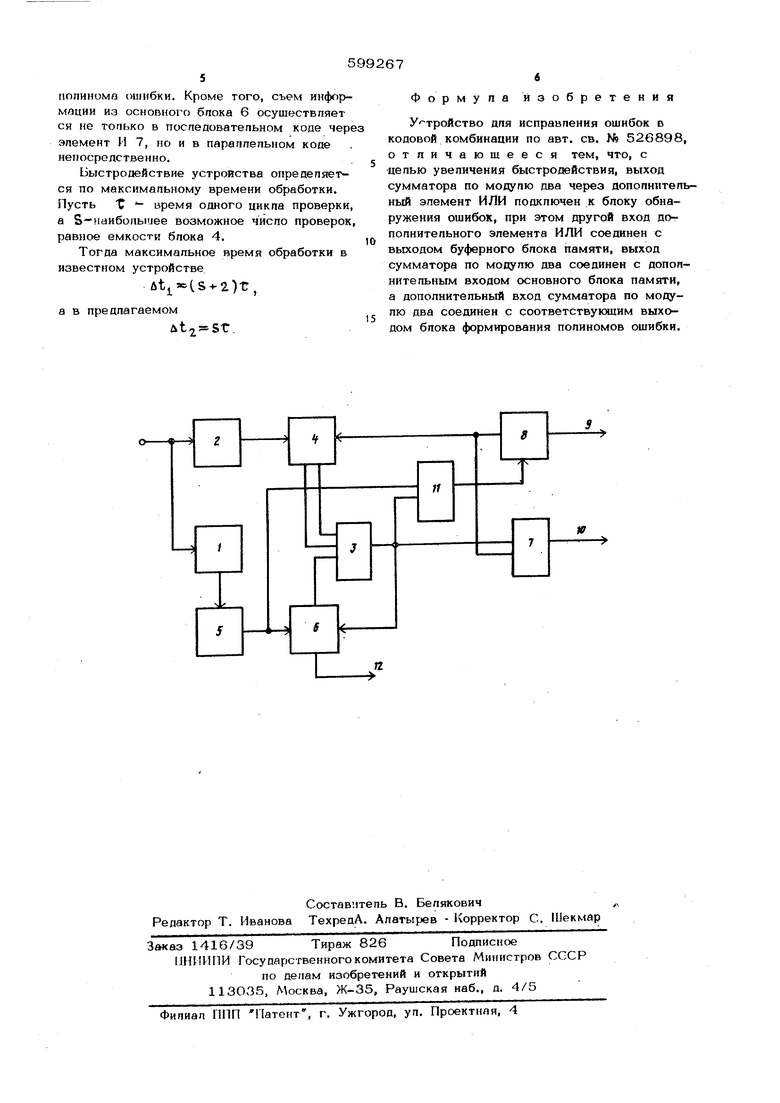

Дпя этого в предлагаемом устройстве содержашем однопороговую и двухпороговую схемы, соединенные с входом устройства, сумматор по модулю два, одни вход которого соединен с выходом блока формирования полиномов ошибок, другой вход через последовательно соединенные буферный и основной блоки памяти соединен е выходом однопороговой схемы, а быход подключен к первому входу элемента И, блок обнаружения ошибок, первый выхрд которого соединен с выходом устройства, второй выход - со вторым входом элемента И, выход элемента И соединен со вторым выходом устройства,, а выход двухпороговоЙ схемы соединен с первым входом блока формирования полиномов ошибок, второй вход которого соединен со вторым выходом бпока обнаружения ошибок, выход сумматора по модулю два соединен с входом блока обнаружения ошибок, выход сумматора по модулю два через дополнительный эпемент ИЛИ подкпюЧен к блоку обнаружения ошибок, при этом другой вход донопнитепьного эпемента ИЛИ соединен с выходом буферного 6ni ка памяти, выход сумматора по модупю два соединен с дополнительным входом основного блока памяти, а дополнительный вход сумматора по модулю два соединен с соответствующим выходом блока формирования полиномов ошибки. На чертеже представлена структурная электрическая схема устройства для исправ ления ошибок в кодовой комбинации. Устройство содержит однопороговую 1 и двухпороговую 2 схемы j соединенные с входом устройства ,сумматор 3 по модулю два, один вход которого соединен с выходом блока 4 формированияполиномов ошибок, другой вход .через последовательно со диненные буферный 5 и основной 6 блок памяти соединен с выходом однопороговой схемы, а выход подключен к первому входу элемента И 75;,блок 8 обнаружения ошибок, первый выход которого соединен с вы ходом 9 устройства, второй выход - со вт рым входом элемента И 7: выход элемента И соединен со вторым выххздом 10 устройства, а выход двухпороговой схемы 2 соединен с первым входом блока 4 формирова ния полиномов ошибок, второй вход которог соединен со вторым выходом блока 8 обна ружения ошибок , выход сумматора 3 по модулю два через дополнительный элемент ИЛИ 11 подключен к .блоку 8 обнаружения ошибок-, при этом другой вход дополнительного элемента ИЛИ 11 соединен с выходом буферного блока 5 памяти; выход сумматор 3 по модулю два соединен с дополнительным входом основного блока 6 памяти, а дополнительный вход Ьумматора 3 по модулю два соединен с соответствующим выходом блока 4 формирования полиномов ошибок; выход 12 является третьим выходом устройства. Устройство работает следующим образом Принятая комбинация одновременно поступает на входы одно- и двухпороговой схем 1 и 2. С выхода однопороговой схемы 1 кодовая комбинация, состоящая из последовательностей О и I, через буферный блок 5 записывается в основной блок 6. Одновременно с записью в основной блок комбинация через элемент ИЛИ 1 поступает в блок 8. В это время двухпоро говая схема 2 осуществляет анализ каждого элемента кодовой комбинации, и в случае невозможности отождествления принятого элемента ни с О, ни с 1 фо(мирует на своем выходе сигнал стирания О, поступающий в блок 4. 1.С/1И в результате анализа принимаемой комбнинции блок 8 не обнаружит ошибк::, то последний выдает блоку 4 сигнал нет ошибок и открывает элемент И 7. По этому сигналу блок 4 переходит в исходное состояние, комбинация из основного блока 6 в последовательном коде через сумматор 3 и открытый элемент И 7 по9тупает на второй выход 1О, а в паралРгельном коде - на третий выход 12 устройства. Устройство проходит в режим ожидания приема очередного сообщения. В случае обнаружения блоком 8 ошибки устройство переходит в режим исправления ошибок. Комбинация через сумматор 3 выдается в блок 8 и повторно записывается в основной блок 6. На сумматоре 3 накладывается первый полином однократной ошибки, формируемый блоком 4. Если при первом цикле проверки блок 8 обнаруживает ошибку, то комбинация из основного блока 6 выдается на проверку второй раз. При этом блок 4 формирует очередной полином однократной ошибки и т. д. до первого необнаружения ошибки в каком-либо из вариантов исправленной комбинации. При этом исправленная комбинация.в очередном цикле работы выдается на второй 1О и третий 12 выходы устройства. Если ошибка будет обнаружена при всех циклах проверки, то блок 8 фиксирует наличие в принятой комбинации неисправляемой ошибки и переводит устройство в режим приема очередного сообщения. Так как при обнаружении ощибки в очередном цикле проверки в основной блок 6 перезаписывается не исходная комбинация, а комбинация с наложенным полиномом ошибки, при следующем цикле проверки на комбинацию должен быть наложен полином, являющийся суммой по модулю два полинома ошибки предыдущего и последующего циклов проверки. При этом на сумматоре 3 будет происходить восстановление исходной комбинации и наложение на нее последующего полинома ошибки. Выявленные двухпороговой схемой 2 ненадежные элементы О (стирания) поступают в блок 4,где осуществляется их запоминание, Увеличение быстродействия обусловливается тем, что из буферного блока 5 комбинация в блок 8 вводится неиосредствентю, а не через основной блок 6. Кроме того, при исправлении ошибки комбинация из основного блока 6 непосредственно поступает получателю, в то времЯ как в известном устройстве требуется допогнпггепьный цикп обработки в виде операции прохожпония комбинации через сумматор 3 и повторнг)гч) наложения на нее полинома ошибки. Кроме того, съем информации из основного блока 6 осушествпяет СИ не топько в поспедоватепьном коде чер элемент И 7, но и в параппепьном копе непосредственно. Выстрошйствие устройства опрепепяется по максимапьному времени обработки. Пусть Т - время одного цикпа проверки а 5-иаибо11ыиее возможное чиспо проверок равное емкости блока 4. Тогда максимальное время обработки в известном устройстве ut.,tS-K2)tr, а в предлагаемом Ф о р м у п а зобретения У- тройство дпя исправления ошибок в кодовой комбинации по авт. св. № 526898, отличающееся тем, что, с целью увеличения быстродействия, выход сумматора по модулю два через дополнительный элемент ИЛИ подключен к блоку обнаружения ошибок, при этом другой вход дополнительного элемента ИЛИ соединен с вькодом буферного блока памяти, выход сумматора по модулю два соединен с дополнительным входом основного блока памяти, а дополнительный вход сумматора по модулю два соединен с соответствующим выходом блока формирования полиномов ошибки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок в кодовой комбинации | 1976 |

|

SU604170A2 |

| Устройство для исправления ошибок в кодовой комбинации | 1974 |

|

SU526898A1 |

| Устройство для обнаружения ииСпРАВлЕНия ОшибОК B КОдОВОйКОМбиНАции | 1979 |

|

SU801283A2 |

| Устройство для обнаружения и исправления ошибок в кодовой комбинации | 1974 |

|

SU540389A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙ КОМБИНАЦИИ | 1972 |

|

SU335689A1 |

| Устройство для обнаружения ошибок | 1983 |

|

SU1100746A1 |

| Устройство для исправления и обнаружения ошибок | 1984 |

|

SU1205312A2 |

| Устройство защиты от ошибок внешней памяти | 1981 |

|

SU1018119A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙКОМБИНАЦИИ | 1971 |

|

SU293243A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

Авторы

Даты

1978-03-25—Публикация

1976-12-13—Подача