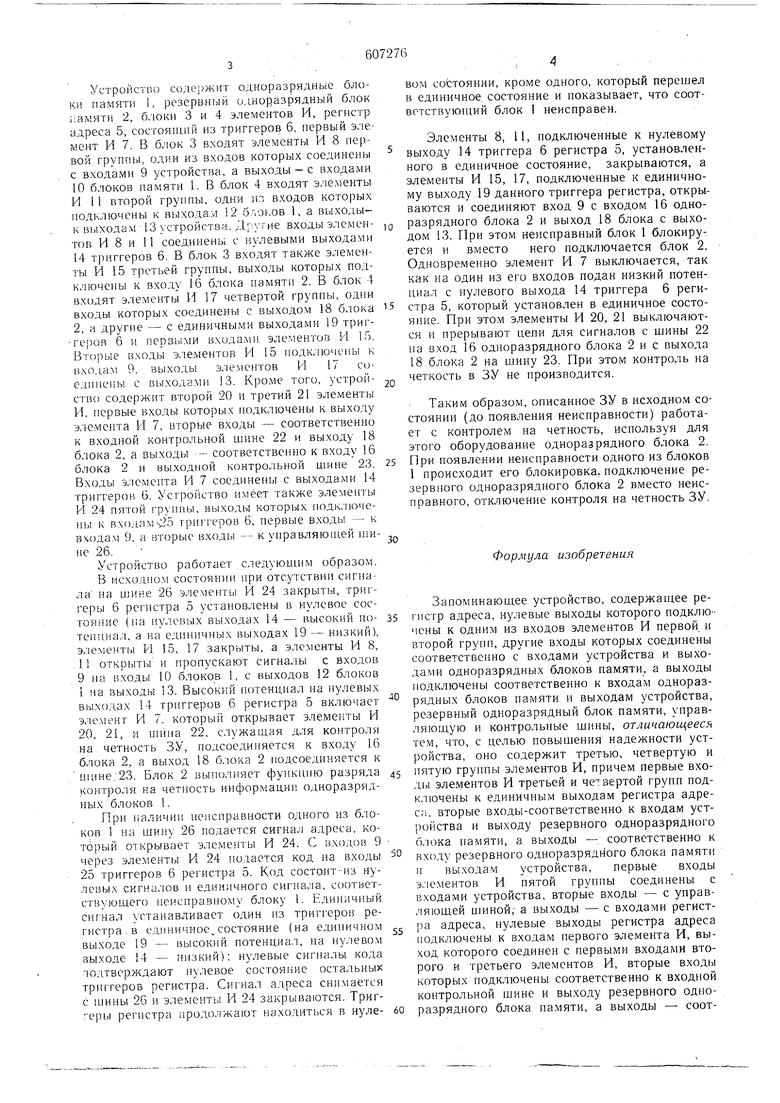

(54) ЗАПОМИНАЮШЕЕ УСТРОЙСТВО Устройство содсржит одноразрядные блоки памяти 1, резервный одноразрядный блок ;:амяти 2, блоки 3 и 4 элементов И, регистр адреса 5, состоящий из триггеров 6, первый элемент И 7. В блок 3 входят элементы И 8 первой группы, один из входов которых соединены с входами 9 устройства, а выходы - с входами 10 блоков памяти 1. В блок 4 входят элементы И 11 второй группы, одни из входов которых подключены к выходам 12 бг.о.ов 1, а выходык выходам 13 устройства. Другие входы элементов И 8 и 11 соединены с нулевыми выходами 14 триггеров 6. В блок 3 входят также элементы И i5 третьей группы, выходы которых подключены к входу 16 блока памяти 2. В блок 4 входят элементы И 17 четвертой группы, одпи входы которых соединены с выходом 18 блока 2, а другие - с единичными выходами 19 триггеров б и первы.ми входам элементов И 15. Вторые входы элементов И 15 подключены к входам 9, выходы элемептов И 17 С(;единены с выходами 13. Кроме того, устройство содержит второй 20 и третий 21 элементы И, первые входы которых подключены к выходу элемента И 7, вторые входы - соответственно к входной контрольной шине 22 и выходу 18 блока 2, а выходы - соответетвепно к входу 16 блока 2 и выходной контро;1ьной шипе 23. Входы э;1Смепта И 7 соединены е выходами 14 триггеров 6. Усгройство имеет также эле.мепты И 24 пятой группы, выходы которых подк.лючепы к входаMv. триггеров 6, первые входы -- к входа.м 9, а вторые входы - - к управляюп1,ей тине 26. Устройство работает следующим образом. В исходпо.м еостояпии при отеу1ствии сигнала на шин.е 26 эле.мепты И 24 закрыты, триггеры 6 регистра 5 уетапогзлены в нулевое состояние (па пулевых выходах 14 - высокий потепциал, а на едппичных выходах 19 - низкий),, элементы И 15, 17 закрыты, а элементы И 8, ,11 открыты и пропускают сигналы с входов 9 на входы 10 блоков I, с выходов 12 блоков 1 на выходы 13, Высокий потенциал на нулевых выходах 14 триггеров 6 регистра 5 включает эле.менг И 7. который открывает элеме1 ты И 20, 21, и uiHHa 22, служащая для контроля ,на четность ЗУ, подсоединяется к входу 16 блока 2, а выхОлТ. 18 б.юка 2 подсоединяется к П1ине.23. Блок 2 вьиюлпяет фупкпню разряда контроля на четность информации одноразрядных блоков 1. При наличии неисправности одного из блоков 1 на шину 26 подается сигнал адреса, который открывает элементы И 24. С входов 9 через элементы И 24 подается код на входы 25 триггеров 6 регистра 5. Кс)Д состонт-из нулевых скгна,:1ов и единичного сигнала, соответствующего неисп)авному блоку 1. Единичный сигнал устанавливает один из триггеров регистра, в единичное состояние (на единичном выходе 19 - высокий потенциал, на нулевом выходе 14 - низкий); нулевые сигналы кода 10;чтвер,ждают нулевое состояние остальных триггеров регистра. Си1-нал адреса снн.мается с тины 26 и элементы И 24 закрываются. Триггеры регистра про;1олжают находиться в нулевом СОСТОЯНИИ, кроме одного, который перешел в единичное, состояние и показывает, что соответствующий блок 1 неисправен. Элементы 8, И, подключенные к нулевому выходу 14 триггера 6 регистра 5, установленного в единичное состояние, закрываются, а элементы И 15, 17, подключенные к единичному выходу 19 данного триггера регистра, открываются и соединяют вход 9 с входом 16 одноразрядного блока 2 и выход 18 блока с выходом 13. При этом неисправный блок 1 блокируется и вместо него подключается блок 2. Одновременно элемент И 7 выключается, так как на один из его входов подан низкий потенциал с нулевого выхода 14 триггера 6 регистра 5, который установлен в единичное состояние. При этом элементы И 20, 21 выключаются и прерывают цепи для сигналов с шины 22 на вход 16 одноразрядного блока 2 и с выхода 18 блока 2 на шину 23. При этом контроль на четкость в ЗУ не производится. Таким образом, описанное ЗУ в исходном состоянии (д,о появления неисправности) работает с контролем на четность, используя для этого оборудование одноразрядного блока 2. При появлении неисправности одного из блоков 1 происходит его блокировка, подключение резервного одноразрядного блока 2 вместо неисправного, отключение контроля на четность ЗУ. Формула изобретения Запоминающее устройство, содержаплее регистр адреса, нулевые выходы которого подключены к одним из входов элементов И первой, и второй групп, другие входы которых соединены соответственно с входами устройства и выходами одноразрядных блоков памяти, а ВЫХОДЬЕ подключены соответственно к входам одноразрядных блоков памяти и выходам устройства, резервный одноразрядный блок памяти, управляющую и контрольные шины, отличающееся тем, что, с целью повышения надежности устройства, оно содержит третью, четвертую и пятую группы элементов И, причем первые входь1 элементов И третьей и че1вертой грунп подключены к едипичным выходам регистра адреc;i, вторые входы-соответственно к входам устройства и выходу резервного одноразрядного блока памяти, а выходы - соответственно к входу резервного одноразрядного блока памятп и выходам устройства, первые входы э.лементов П пятой группы соединены с входами устройства, вторые входы - с управляющей щиной,- а выходы - с входами регистра адреса, нулевые выходы регистра адреса подключены к входам первого элемента И, выход которого соединен с первыми входами второго и третьего элементов И, вторые входы которых подключены соответственно к входной контрольной шине и выходу резервного одноразрядного блока памяти, а выходы - соответственно к входу резервного одноразрядного блока памяти и выходной контрольной шине. Источники информации, принятые во внимание при экспертизе:

1.Патент США Xs 3568153, кл. 340-146.1. 1971.

2.Авторское свидетельсгво СССР № 263682, кл. G 11 С 7/00, 1966.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1978 |

|

SU781973A1 |

| Запоминающее устройство | 1979 |

|

SU842955A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970476A1 |

| Запоминающее устройство с резервированием | 1980 |

|

SU963088A1 |

| Запоминающее устройство | 1980 |

|

SU903973A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1981 |

|

SU972599A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Запоминающее устройство с защитой информации при отключении питания | 1980 |

|

SU888205A1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Запоминающее устройство | 1980 |

|

SU858095A1 |

Авторы

Даты

1978-05-15—Публикация

1975-04-14—Подача