Изобретение относится к запоми аюцим устройствам и может быть применено в вычислительных машинах параляельного действия, к которым предъявляется требование сохранения работоспособности при наличии одной неисправности.

Известно запоминшощее устройство с самоконтролем, содержащее матрицу функциональных ячеек, избыточные функциональные {пейки, средства выбора ячеек, память для хранения адресов неисправных ячеек, логику управления замещением tl3.

Недостатком этого устройства является то, что в нем не предусмотрено использование избыточных функциональных ячеек для контроля основных функциональных ячеек.

Наиболее близким техническим решением к изобретению является зешоминающее устройство с самоконтролем, содержащее регистр адреса, нулевые выходы которого подключены к одним из входов элементов И первой и второй групп, другие входы которых соединены соответственно с выходами устройства и выходами одноразрядных блоков памяти, а выходы подключены соответ(ственно к входам одноразрядных блоков памяти и исходам устройства, реэервный одноразрядный блок памяти, управляювдю и контрольную шины,третью, четвертую и пятую группы элементов И, первые входы элементов И третьей и четвертой групп подключены к единичным выходам регистра адреса, вторые входа - соответственно к входам устройства и вы10ходу резервного одноразрядного блока памяти, а выходы - соответственно к входу резервного одноразрядного блока памяти и выходам устройства, первые входы элементов и пятой груп15пы соединены с входами устройства, вторые входа - с управляющей шиной,, ;а выходы - с входами регистра адреса, нулевые входы регистра адреса подключены к входам первого элемента И,

20 выход которого соединен с первыми входами второго и третьего элементов И, вторые входы которых подключегел соответственно к входной контрольной шине и выходу резервного одноразряд25ного блока памяти, а выходы - к saходу резервного одноразрядного блока памяти и выходной контрольной шине |.2

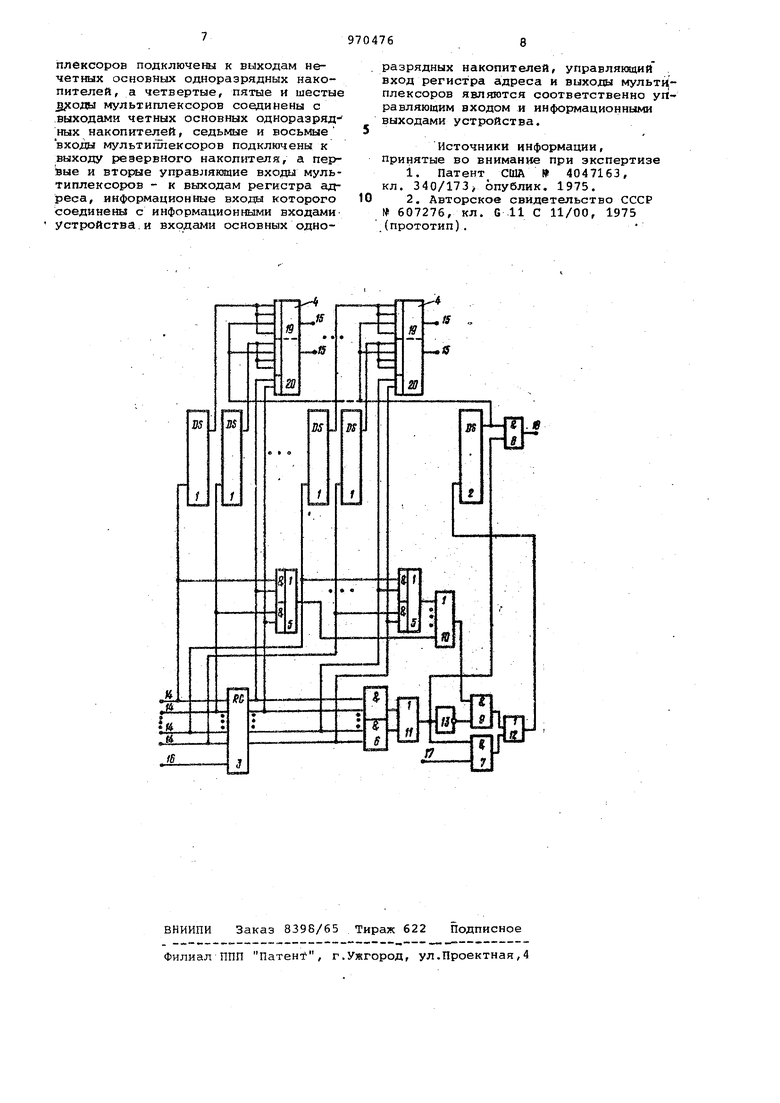

Недостатками этого устройства яв.ляются отсутствие блокировки обору30дования контроля по четности при его отказе, пониженная помехозащищенност обусловленная наличием избыточных це пей нулевых выходов триггеров регист ра адреса и использование .цля управления замещением сложного оборудования, в частности элементов И первой группы, что снижает надежность устройства. Цель изобретения - упрощение и по вышение надежности запоминающего устройства, Поставленная цель достигается тем что в запоминающее устройство с само контролем, содержащее одноразрядные накопители, резервнйй Одноразрядный накопитель, регистр адреса, элементы И, элементыИЛИ и элементы И-ИЛИ, первые и вторые входы которых явля1ются информационными входами устрой|ства, третьи и четвертые входы соеди нены с выходами регистра адреса и входами первого элемента И, выходы эле ентов И-ИЛИ подключены; к входам первого элемента ИЛИ, выходы первого элемента И соединены с входами второго элемента ИЛИ, выход которого подключенк первым входам второго и третьего элементов И, второй вход третьего элемента И соединен с выходом резервного одноразрядного накопителя , второй вход второго элемеН та И и выход третьего элемента И являются соответственоо контрольным входом и выходом устройства, введены мультиплексоры, третий элемент ИЛИ, четвертый элемент И и элемент НЕ, вход которого соединен с выходом второго элемента ИЛИ, а выход - с и первым входом четвертого элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, а выходк первому входу третьего элемента ИЛИ, второй вход Которого соединен с выходом второго элемента И, а.выход с входом резервного одноразряд ного накопителя, первые, вторые и третьи входы мультиплексоров подключены к выходам нечетных основных одноразрядных накопителей, а четвертые пятые и шестые входы мультиплексоров Соединены с выходами четных основных одноразрядных накопителей, седьмые и восьмые входы мультиплексоров подключены к выходу резервного накопителя, а первые и вторые управляющие входы мультиплексоров - к выходс1М регистра адреса, информационные входы которого соединены с информационными входами устройства и входами основных одноразрядных накопителей, управлякнций вход регистра адреса и выходы мультиплексоров являются соответственно управляющим входом и информационными выходами устройства. На чертеже приведена функциональная схема запоминающего устройства. Устройство содержит основные одноразрядные накопители 1, резервный одноразрядный накопитель 2. регистр 3 адреса, мультиплексоры 4, элементы И-ИЛИ 5, первый 6, второй 1. третий 8 и четвертый 9 элементы И, первый 10, второй 11 и третий 12 элементы ИЛИ и элемент НЕ 13. На чертеже обозначены информационные входы 14 и выходы 15, уйравляющие входы 16 и контрольные вход 17 и выход 18 устг ройства. В качестве мультиплексоров могут быть использованы, например, интегральные микросхемы, состоящие из. двух логических переключателей 19 и 20 из четьфех в один. Устройство работает следующим-образом. На входы двух логических элементов 19 и 20 поступает двухразрядный управляющий код (с попарных выходов регистра 3 адреса), На первом и вто(Ром выходах мультиплексора 4 появляется соответственно сигнал с первс го и четвертого его входов., если по упрсшляющим входам поступает разрешающий код 00, со второго и восьмого, еслц, разрешающий код - 01, с пятого и седьмого, если разрешанлдий код 10, с третьего и шестого, если разрешающий код - 11, В исходном состоянии регистр 3 адреса установлен в нулевое состояние подачей кода 00 ... О по входгии 14 устройства и сигнала разрешения по управляющей шине 16, На выходах регистра 3 устанавливаются нулевые потенциалы, и элементы И-ИЛИ 5, элемент И б закрыты. Нулевые потенциалы выходов регистра 3 подключают выходы одноразрядных накопителей 1 через первые и четвертые входы мультиплексоров 4-к выходам 15 устройства. Поступление информации на вход резервного накопителя 2 блокируется нулевыми потенциалами на выходе элемента ИЛИ 10, а выход информации с резервного накопителя 2 на выходы 15 устройства блокируется на мультиплексорах 4 подачей кода 00 по управляющим входам. Сигнал с выхода элемента ИЛИ 11 через элемент И 7 и элемент ИЛИ 12 запрещает прохождение информации со входа .17 на вход накопителя 2 и на выход 18 с выхода накопителя 2. В данном состоянии устройство работает в режиме запоминания и выдачи информации одноразрядными накопителями 1, и контроль на четность не проводится. Для задания режима контроля четности на входы, 14 устройства подается код 11 ... 1. При наличии разрешагацего сигнала на входе 16 этот код записывается в регистр 3 годреса. Элементы И 6 и ИЛИ 11 срабатьгааюту сигнал с выхода элемента ИЛИ 11 разрешает запись кода контроля четности, поступающего на вход 17, в резервный накопитель 2 через элементы И 7, ИЛИ 12. Информация; записанная в накопитель 2, воспроизводится на выход 18, так как на элемент И 8 также пос тупает разрешающий сигнал с выхода элe /leнтa ИЛИ 11. Сигнал с выхода элемента ИЛИ 11 через элемент НЕ 13 запрещает запись информации с выхода элемента ИЛИ 10 в накопитель 2. Код 11 ... 1 с выходов регистра 3 подает gj также на управляющие входы мульти jinexcopOB 4 и подключает через тоеть ч шестые входы мультиплексоров 4 выходы одноразрядных накопителей 1 на входы 15 устройства. После занесения кода 11 ... 1 в регистр 3 сигнал разрешения со входа 16 снимается, и устоойство работает в режиме запоминания и выдачи информации с контролем на четность. В случае наличия неисправности одного из накопителей 1 осуществляется замещение его резервным накопителем 2. Для этого на входы 14 устройства подается код с единицей в разряде, соответс-увующем неисправному из накопителей 1, и нулями в остальных разрядах. При наличии сигнала разрешения на входе 16 этот код записывается в регистр 3. На выходах регистра 3 устанавливаются нулевые потенциалы, соответствующие нулевым кодам входной информации, и положительный потенцигш, соответствующий коду единицы входной информации. При этом запрещается срабатывание элементов И б 7 и 8 и элемента ИЛИ 11. Сигнал с выхода элемента НЕ 13 разрешает запись информации в резервный накопитель 2 через элементы И-ИЛИ 5, ИЛИ 10 .9 И, ИЛИ 12 с того входа 14 устройст |ва, разряд которого замещается. Если неисправен нечетный блок (ус тановлен в единицу нечетный разряд регистра 3), то на управляющие входы соответствующего мультиплексора 4 по дается код 10. При этом производится подключение выхода резервного накопи теля 2 через первый выход мультиплек сора 4 на один из выходов 15 устройства, а на другой выход 15 устройств поступает информация с выхода четного накопителя 1. Если неисправен четный накопитель 1 (установлен в единицу четный разря регистра 3), то на управляющие входы мультиплексора 4 подается код 01. Пр этом на первый выход соответствукяцего мультиплексора 4 поступает информация с выхода нечетного накопителя 1, а на второй выход - информация с выхода резервного накопителя 2. При этом контроль на четность не производится. Предлагаемое устройство обеспечивает блокировку оборудования контроля по четности при работе в режиме запоминания и выдачи информации, что Расширяет функциональные возможности устройства. Этот режим вводится без дополнительных затрат оборудования за счет задействования не используемого в остальных режимах состояния мультиплексора 4 и необходим при неисправности контрольного оборудования и (или) оборудования управления замещением, например, при неисправности одного или нескольких элементов И-ИЛИ 5, элементов И 6-9, элементов ИЛИ 10-12, элемента НЕ 13 и (или) накопителя 2, повышение помехозащищенности за счет уменьшения в два раза количества выходных цепей регистра 3, и сокращение оборудования за счет того, что регистр 3 адреса мажет быть выполнен на интегральных микросхемах, за счет чего повышается на|дежность устройства. Технико-экономическое преимущество предлагаемого устройства заключается, таким образом, в упрощении устройства за счет сокращения оборудования и в его более высокой надежности по сравнению с известным. Формула изобретения Запоминак14ее устройство с самоконтролем, содержащее одноразрядные накопители, резервный одноразрядный накопитель, регистр адреса, элементы И, элементы ИЛИ и элементы И-ИЛИ, перовые и вторые входы которых являются Информационными входами устройства, третьи и четвертые входы соединены с выходами регистра адреса и входами первого элемента И, выходы элемен- тов И-ИЛИ подключены к входам первого элемента ИЛИ, выходы первого элемента И соединены с входами второго элемента ИЛИ, выход которого подключен к первым входам второго и третьего элементов И, второй вход третьего Элемента И соединен с выходом резервного одноразрядного накопителя, втоЕЮй вход второго элемента И и выход третьего .элемента И являются соответственно контрольными входом и выходом устройства, отличающеес я тем, что, с целью упрощения и повышения надежности устройства, в , него введены мультиплексоры, третий элемент ИЛИ, четвертый элемент и и Ьлёмент НЕ, вход которого соединен с выходом второго элемента ИЛИ, а выход - с первым входом четвертого элемента И, второй ЕХОД которого подключен к выходу первого элемента ИЛИ, а выход - к первому входу третьего элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, а выход - с входом резерв«ного одноразрядного накопителя, первые, вторые и третьи входы мульти-

плексоров подключены к выходам нечетных основных одноразрядных накопителей, а четвертые, пятые и шестые оды мультиплексоров соединены с выходами четных основных одноразрядных накопителей, седьмые и восьмые входы мультигшексоров подклнмены к выходу резервного накопителя, а перйые и второе управляквдие входы мультиплексоров - к выходам регистра адреса, информационные входа которого соединены с информационными входами устройства:и входами основных одноразрядных накопителей, управляивдий вход регистра адреса и выхода мультиплексоров являются соответственно yriравляющим входом и информационными выходами устройства.

Источники информации. Принятые во внимание при экспертизе

1. Патент США 4047163, кл. 340/173 опублик. 1975. 2. Авторское свидетельство СССР № 607276, кл. G 11 С 11/00, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1979 |

|

SU842955A1 |

| Запоминающее устройство | 1975 |

|

SU607276A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1185400A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1065855A1 |

| Запоминающее устройство | 1978 |

|

SU781973A1 |

Авторы

Даты

1982-10-30—Публикация

1981-04-10—Подача