(54) УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ КОДА

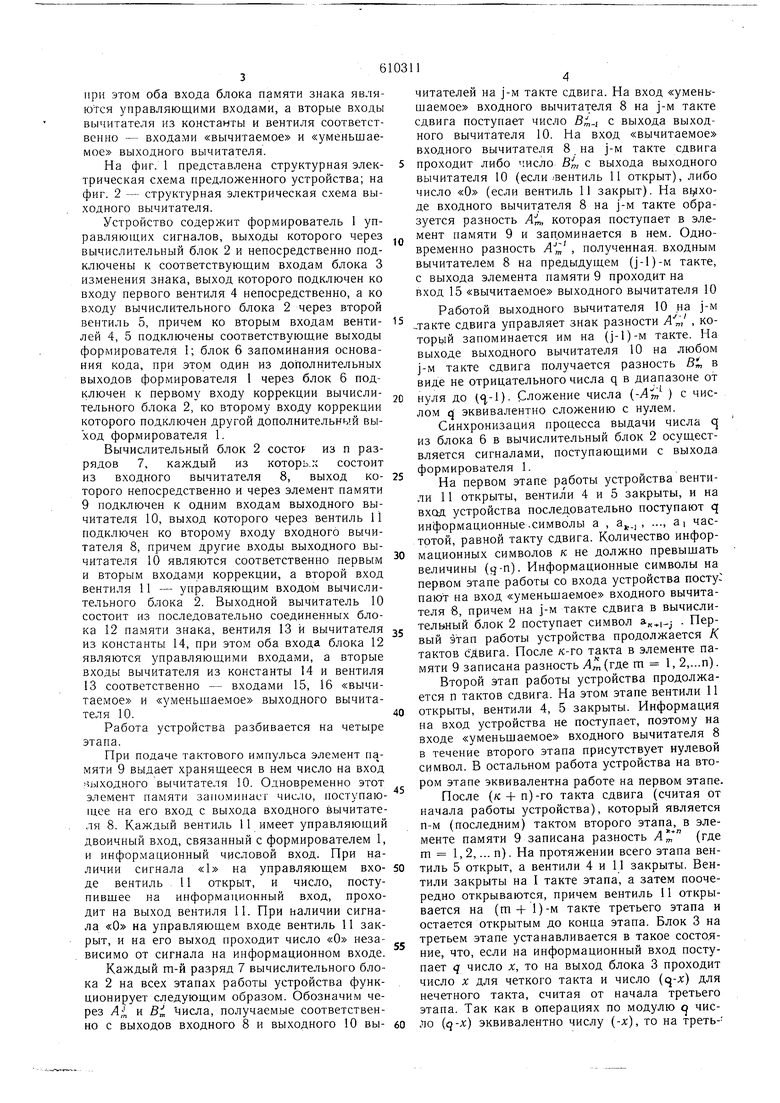

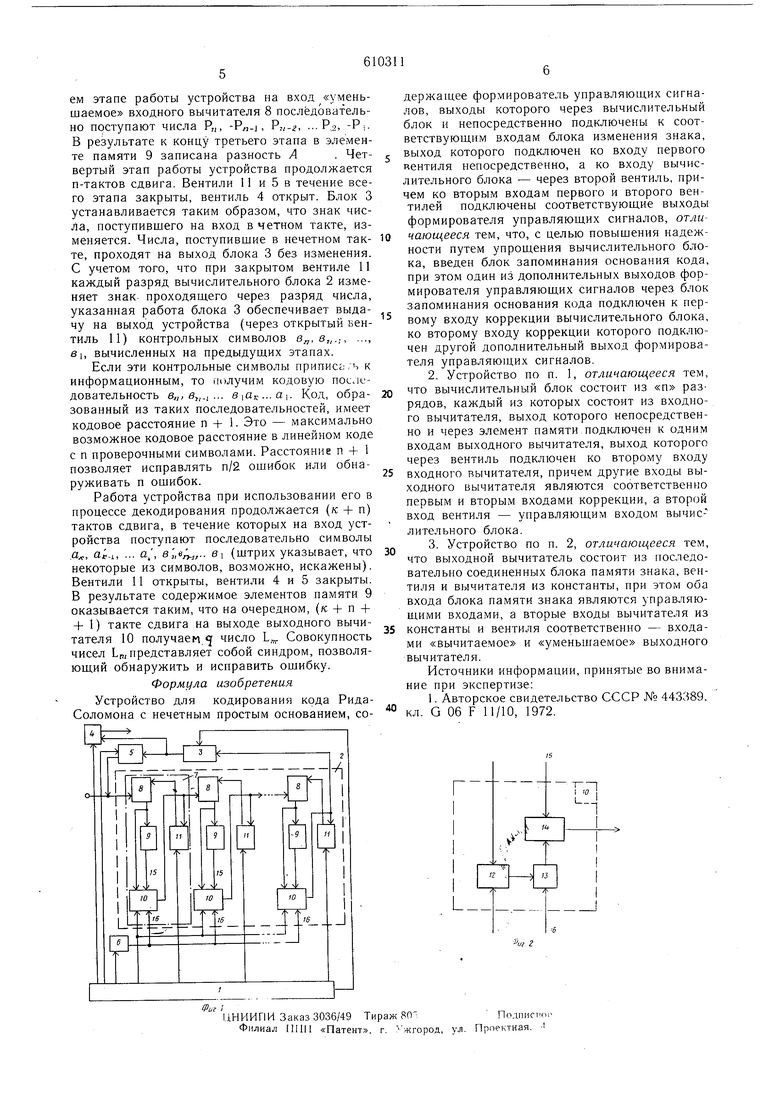

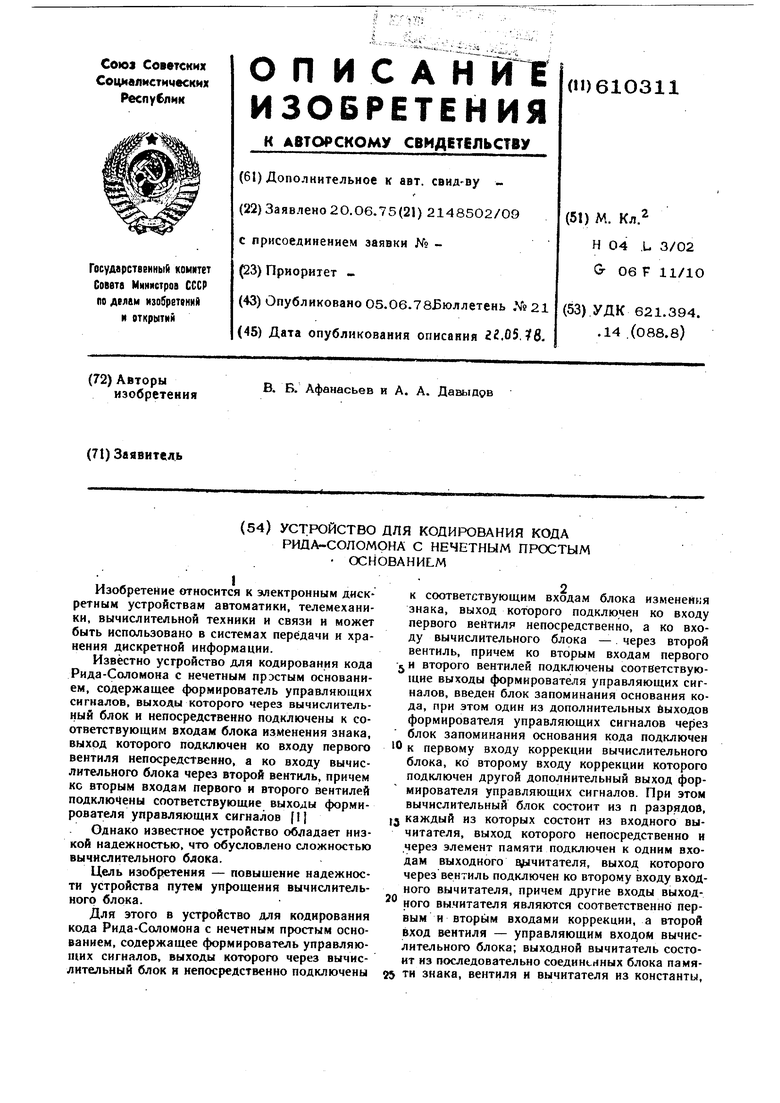

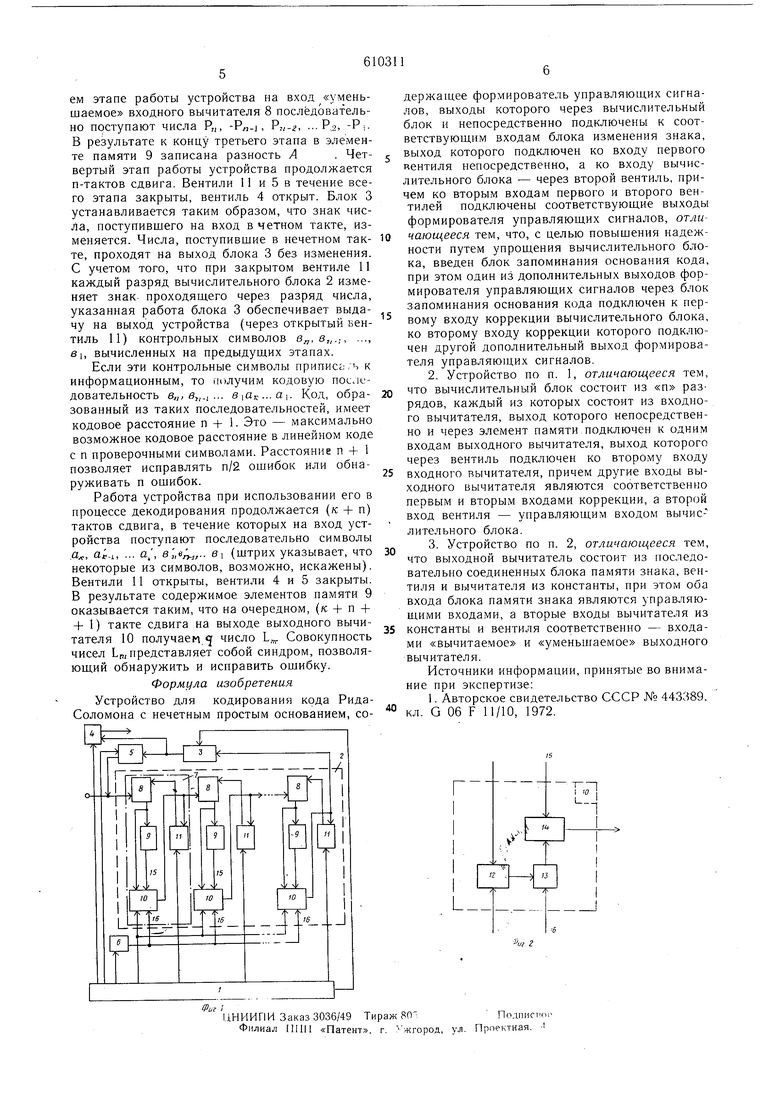

РИДА-СОЛОМОНА С НЕЧЕТНЫМ ПРОСТЫМ ОСНОВАНИЕМ при этом оба входа блока памяти знака являются управляющими входами, а вторые входы вычитателя из константы и вентиля соответственно - входами «вычитаемое и «уменьшаемое выходного вычитателя. На фиг. 1 представлена структурная электрическая схема предложенного устройства; на фиг. 2 - структурная электрическая схема выходного вычитателя. Устройство содержит формирователь 1 управляющих сигналов, выходы которого через вычислительный блок 2 и непосредственно подключены к соответствующим входам блока 3 изменения знака, выход которого подключен ко входу первого вентиля 4 непосредственно, а ко входу вычислительного блока 2 через второй вентиль 5, причем ко вторым входам вентилей 4, 5 подключены соответствующие выходы формирователя 1; блок 6 запоминания основания кода, при этом один из дополнительных выходов формирователя 1 через блок 6 подключен к первому входу коррекции вычислительного блока 2, ко второму входу коррекции которого подключен другой дополнительный выход формирователя 1. Вычислительный блок 2 cocтo из п разрядов 7, каждый из которь.. состоит из входного вычитателя 8, выход которого непосредственно и через элемент памяти 9 подключен к одним входам выходного вычитателя 10, выход которого через вентиль И подключен ко второму входу входного вычитателя 8, причем другие входы выходного вычитателя 10 являются соответственно первым и вторым входами коррекции, а второй вход вентиля 11 - управляющим входом вычислительного блока 2. Выходной вычитатель 10 состоит из последовательно соединенных блока 12 памяти знака, вентиля 13 и вычитателя из константы 14, при этом оба входа блока 12 являются управляющими входами, а вторые входы вычитателя из константы 14 и вентиля 13 соответственно - входами 15, 16 «вычитаемое и «уменьшаемое выходного вычитателя 10. Работа устройства разбивается на четыре этапа. При подаче тактового импульса элемент па мяти 9 выдает хранящееся в нем число на вход выходного вычитателя 10. Одновременно этот элемент памяти запоминает число, ноступаюnj.ee на его вход с выхода входного вычитателя 8. Каждый вентиль 11 имеет управляющий двоичный вход, связанный с формирователем 1, и информационный числовой вход. При наличии сигнала «1 на управляющем входе вентиль . 11 открыт, и число, поступившее на информационный вход, проходит на выход вентиля И. При наличии сигнала «О на управляющем входе вентиль 11 закрыт, и на его выход проходит число «О независимо от сигнала на информационном входе. Каждый гп-й разряд 7 вычислительного блока 2 на всех этапах работы устройства функционирует следующим образом. Обозначим через А; и В числа, получаемые соответственно с выходов входного 8 и выходного 10 вычитателей на j-м такте сдвига. На вход «уменьшаемое входного вычитателя 8 на j-м такте сдвига поступает число S.j с выхода выходного вычитателя 10. На вход «вычитаемое входного вычитателя 8 на j-м такте сдвига проходит либо число Вт с выхода выходного вычитателя 10 (если вентиль 11 открыт), либо число «О (если вентиль 11 закрыт). На BI XOде входного вычитателя 8 на j-м такте образуется разность Лто которая поступает в элемент памяти 9 и запоминается в нем. Одновременно разность , полученная, входным вычитателем 8 на предыдущем (j-l)-M такте, с выхода элемента памяти 9 проходит на вход 15 «вычитаемое выходного вычитателя 10 Работой выходного вычитателя 10 на j-м сдвига управляет знак разности AJ , которуй запоминается им на (j-l)-M такте. На выходе выходного вычитателя 10 на любом j-м такте сдвига получается разность Вт в виде не отрицательного числа q в диапазоне от нуля до (-1). Сложение числа ( ) с числом q эквивалентно сложению с нулем. Синхронизация процесса выдачи числа q из блока 6 в вычислительный блок 2 осуществляется сигналами, поступающими с выхода формирователя 1. На первом этапе работы устройства вентили 11 открыты, вентили 4 и 5 закрыты, и на вход устройства последовательно поступают q информационные .символы а , a.j , ..., ai частотой, равной такту сдвига. Количество информационных символов к не должно превышать величины (у-п). Информационные символы на первом этапе работы со входа устройства поступают на вход «уменьшаемое входного вычитателя 8, причем на j-м такте сдвига в вычислительный блок 2 поступает символ . Первый этап работы устройства продолжается К тактов сдвига. После к-го такта в элементе памяти 9 записана разность А,п (где m 1, 2,...п). Второй этап работы устройства продолжается п тактов сдвига. На этом этапе вентили 11 открыты, вентили 4, 5 закрыты. Информация на вход устройства не поступает, поэтому на входе «уменьшаемое входного вычитателя 8 в течение второго этапа присутствует нулевой символ. В остальном работа устройства на втором этапе эквивалентна работе на первом этапе. После («: + п)-го такта сдвига (считая от начала работы устройства), который является п-м (последним) тактом второго этапа, в элементе памяти 9 записана разность Л (где m 1, 2,... п). На протяжении всего этапа вентиль 5 открыт, а вентили 4 и 11 закрыты. Вентили закрыты на I такте этапа, а затем поочередно открываются, причем вентиль 11 открывается на (m-f 1)-м такте третьего этапа и остается открытым до конца этапа. Блок 3 на третьем этапе устанавливается в такое состояние, что, если на информационный вход поступает q число X, то на выход блока 3 проходит число X для четкого такта и число () для нечетного такта, считая от начала третьего этапа. Так как в операциях по модулю о число (q-x) эквивалентно числу (-х), то на треть

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования | 1985 |

|

SU1275782A1 |

| Декодер мажоритарных блоковых кодов | 1986 |

|

SU1349011A1 |

| Преобразователь импульсно-кодомодулированных сигналов в дельта-модулированные сигналы | 1985 |

|

SU1264347A1 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| Устройство для разложения цифровых сигналов по Уолшо-подобным базисам | 1983 |

|

SU1108461A1 |

| Преобразователь сигналов с импульсно-кодовой модуляцией в сигналы с адаптивной дельта-модуляцией со слоговым компандированием | 1990 |

|

SU1709537A1 |

| Устройство для декодирования с исправлением ошибок | 1990 |

|

SU1797165A1 |

| Процессор быстрого преобразования уолша-адамара | 1989 |

|

SU1795471A1 |

| Устройство для быстрого преобразования Уолша-Адамара | 1987 |

|

SU1443002A1 |

| Вычислительное устройство | 1980 |

|

SU1001090A1 |

Авторы

Даты

1978-06-05—Публикация

1975-06-20—Подача