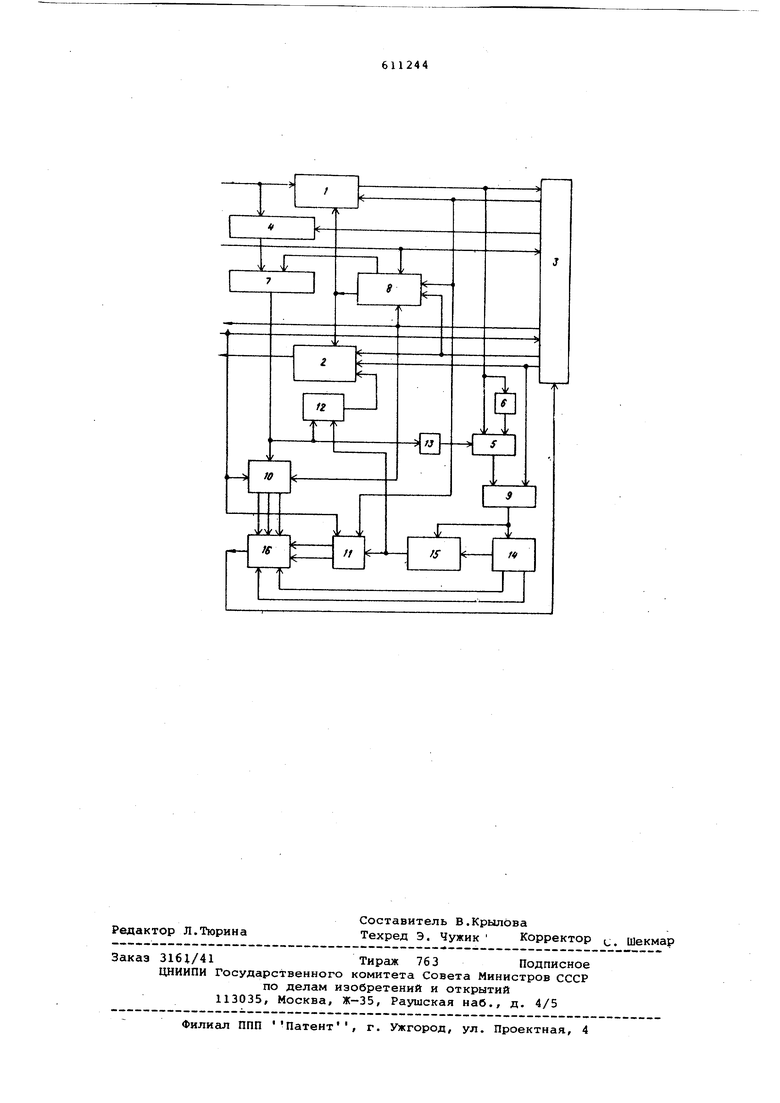

(54) УСТРОЙСТВО ДЛЯ ПРИЕМА И ВЫДАЧИ ИНФОЕадДЦИИ С КОНТРОЛЕМ ОШИБОК тов и выдачи данных, выходы которых являются информационными выходами уст ройства, третий выход блока управлени соединен с управляющим входом группы элементов И выдачи данных и с четвер тым входом блока синхронизации, стробирутащий выход которого соединен со стробирующими входами групп элементов И приема и выдачи данных . Это известное устройство имеет низкую эффек тивность, контроля информации, вызванную ограниченностью средств контроля обмена двоичной информацией. Вследствие этого в известном устройстве снижается вероятность обнаружения ошибок при обмене и достоверности информации возможен беспрепятственный прием и передача искаженной сбоями и неисправ ностями информации. Кроме того, из-за низкой эффективности контроля информа ции в известном устройствесущественно усложняются поиск и локализация неисправностей в тракте передачи информации между каналом и внешними уст ройствами. Целью изобретения является повыше ние достоверности приема и выдачи инф мадии. В предлагаемом устройстве это достигается тем, что в него введены блок оценки формата данных, блок фор мирования сигнала ошибки, селектор, блок вычисления контрольной суммы, блок свертки, две группы элементов И группа элементов ИЛИ, группа элементов НЕ и элемент задержки, причем вы ходы группы элементов И приема данны соединены непосредственно и через группу элементов НЕ сО входами селек тора, выход которого соединен с первыми входами группы элементов ИЛИ, информационные выходил блока управления соединены со вторыми входами гру пы элементов ИЛИ, выходы которых соединены со входами блока свертки и блока вычисления контрольной суммы, информационные выходы блока свертки соединены с первой группой входов бл ка формирования сигнала ошибки, выход разрешения суммирования блока свертки соединен с управляющим входом блока вычисления контрольной cyMNuJ, выходы которого соединены с информационными входами первой и второй групп элементов И,, вход прерывания устройства соединен с первым входом блока оценки формата данных и с первым управляющим входом первой группы элементов И, второй управляющий вход которой соединен со вторым выходом блока управления, а выходы - со второй группой выходов блока формирования сигнгша ошибки, выход признака и формации -абонента блока управления соединен со вторым входом блока оцен ки формата данных, выход схеки сравнения соединен с управляющим входом второй группы элементов И, с третьим входом блока оценки формата данных и через элемент , задержки - с управляющим входом селектора, выходы блока оценки формата данных соединены с третьей группой входов блока формирования сигнала йшибки, выход которого соединен с третьим входом блока управления, выходы второй группы элементов И соединены с информационными входами группы элементов И выдачи данных. На чертеже показана блок-схема предлагаемого устройства. Оно содержит группу элементов И 1 риема данных и группу элементов И 2 ыдачи данных, и блок 3 управления. Информационные входы устройства подключены ко входам группы элементов И 1 приема данных и ко входам блока 4 задания формата обмена данными, соединенным с первым выходом блока 3 управления, второй и третий выходы которого соединены соответственно с управляющими входами групп элементов И приема и выдачи данных. Выходы группы элементов И приема данных соединены с информационными входами блока 3 управления, с первыми входами селектора 5 и через группу элементов НЕ 6 - со вторыми входами селектора 5. Выходы блока 4 задания формата обмена данными подключены к первой группе входов схемы 7 сравнения, вторая группа входов которой соединена с информационными входами блока 8 синхронизации, который соединен со вторым и третьим выходами блока 3, со входом признака информации канала и с выходом признака информации абонента блока 3. Стробирующий выход блока 8 подключен к одноименным вхрдам групп элементов И приема и выдачи данных. Входы группы элементов И 2 выдачи данных соединены с информационными выходами блока 3 и GO вторыми входами группы элементов ИЛИ 9, первые входы которой подключены к выходам селектора 5. Вход признака информации канала устройства соединен с первым входом блока управления. Вход прерывания устройства соединен с первым входом блока 10 оценки формата данных и с первым управляющим входом первой группы эле ментов И 11, второй управляющий вход которой соединен со вторым выходом блока 3 управления. Выход признака информации абонента блока 3 управления .соединен со. вторым входом блока 10 оценки формата данных. Выход схема 7.сравнения подключён к управляющему входу второй группы элементов И 12, к третьему входу блока 10 оценки формата данных и через элемент 13 задержки - к управляющему входу селектора 5. Выходы группы элементов ИЛИ 9 подключены ко входам блока 14 свер: ки и ко входам блока 15 вычисления контрольной суимы, причем выход разрешения суммирования блока 14 соединен с управляющим входом блока 15. Выходы блока 15 подключены к информационным входам первой группы элементоз И 11 и второй группы элементов И 12, выходы которых соединены с информационными входами группы элементов И 2 выдачи данных. Выходы Норма, Больше и Меньше блока 10 оцен ки формата данных, выходы первой груп пы элементов И 11 и выходы блока 14 свертки подключены к соответствующим входам блока 16 формирования сигнала ошибки, выходы которого соединены с третьим входом блока 3 управления. Выходы группы элементов И 2 являются информационными выходами устройства. В процессе выполнения последовательности выборки внешнего устройства блок 3 управления выдает напервом выходе сигнал разрешения приема из канала по информационным входам разря дов модификации команды. Разряды команды поступают из кангша в блок 4 задания формата обмена данными, где определяется режим обмена массивом в N байтов, без учета байта контрольной суммы канала, которую канал выставляет после передачи массива данны для обнаружения кратных ошибок. В бло ке 4 формируется соответствующий за,данному формату данных код, поступающий на вторые входы схемы 7 сравнения В режиме приема данных блок 3 выдает на второй выход сигнал разрешения при ема, который поступает на группу элементов И 1 приема данных, подготавливая их к открыванию, и в блок 8 синхронизации. Одновременно блок 3 транслирует в канал сигнал Информация абонента (ИНФ-А), сообщая о готовности к приему данных. По получении сигнала ИНФ-А канал выдает байт данных на информационные входы устройств и сигнал Информация канала (ИНФ-К на вход признака информации канала, устройства. Сигнал ИНФ-К поступает в блок 3 и блок 8. Последний при совпадении сигналов ИНФ-А и ИНФ-К фиксирует принятие одного байта информации и вьадает стробирующий сигнал на группу элементов И 1, которые открываются и пропускают байт информации в бло 3. Одновременно принятьгй байт информа ции поступает на первые входы и через группу элементов НЕ б на вторые вхо ды селектора 5. При этом выход селектора 5 подключен к своему первого вхо ду управляющим сигналом с выхода схемы 7 через элемент 13 задержки. Таким образом, принятый байт инфор мации через первые входы селектора 5 и группу элементов ИЛИ 9 поступает на входа блока 14 свертки и на входам блока 15 вычисления контрольной сумма В блоке 14 принятый байт информации проверяется по четности, и 1пи правильной четности блок 14 выдает сигнал разрешения суммирования в блок 15 и сигнал Четность правильная - в блок 16 формирования сигнала ошибки. Посл /1;ний при этом вырабатывает сигнал разрешения продолжения обмена и вЕлдает его в блок 3. Блок управления сбрасывает сигнал ИНФ-А, указывая тем самым каналу на прием первого байта информации. Канал реагирует на сброс сигнала ИНФ-А сбросом информации на информационных входах устройства и сбросом сигнала ИНФ-К. При этом блок 3 управления снова транслирует в канал сигнал ИНФ-А, сообщая о готовности к приему второго байта данных. Процесс приема второго байта данных происходит аналогично. При неправильной четности принятого байта информации блок 14 выдает сигнал Четность неправильная в блок 16, который анализирует состояние выходов блока 14, фиксирует неправильную четность поступившего байта информации и выдает соответствующий сигнал в блок 3. Последний выставляет в канал сигнал прерывания обмена. В дальнейшем при поступлении от канала байтов ннфоркации с правильной четностью блок 15 производит последовательное суммирование всех поступающих байтов информации, а блок 8 синхронизации фиксирует число поступающих единиц информации, т.е. текущий формат данных, значение которого поступает из блока 8 на первые входы схемы 7. После приема последнего байта в массиве данных (предпоследнего с учетом байта контрольной cyNSMu) в блоке 8 устанавливается текущий формат данных, равный заданному формату. При этом схема 7 фиксирует равенство форматов и выдает сигнал совпадения в блок 10 оценки формата данных, на управляющий вход второй группы элементов И 12 и через элемент 13 задержки - на управляющий вход селектора 5. В селекторе 5 происходит переключение его выхода с первого входа на второй вход. Элемент 13 обеспечивает прохождение последнего байта Данных через первый вход селектора 5 до переключения его выхода на второй вход. После передачи всего массива данных канал выставляет, байт контрольной суммы, который через группу элементов И 1 приема данных подается на группу элементов НЕ 6. Инверсное значение контрольной суммы через второй вход селектора 5 и группу элементов ИЛИ 9 подается на входы блока 15. При правильной четности инверсного байта контрольной суммы в блоке 15 происходит суммирование контрольной , вычисленной в прцессе приема массива данных, с инверсным значенйвм контрольной сумг«л, переданной каналом. В случае равенства обеих сумм сумма байтов прямого и инверсно го значения контрольной: суммы представляет собой двоичное число с единичными значениями во всех его разрядах. После приема от канала байта контрольной суммы, блок 3 транслирует в канал сигнал ИНФ-А, сообщая каналу о готовности к принятию следующего байта. Но так как вся информация/ включая массив данных и его контрольную сумму, каналом передана, он выставляет на вход прерывания сигнал, свидетельсвующий об окончании передачи данных и поступающий в блок 3, в блок 10 и на первую группу элементов И 11.

Блок 10 учитывает последовательность поступления в него сигнала со впадения от схемы 7, соответствующего принятию от канала заданного массива данных, сигнала ИНФ-А, поступающего после сигнала совпадения и соответствующего принятию от канала байта контрольной массива данных и сигнала прерывания передачи данных, поступающего непосредственно после приема байта контрольной суммы. При наличии указанных сигналов и выполнения последовательности их поступления, блок iO оценки формата данных вырабатывает сигнал оценки Норма, поступающий в блок 16 формирования сигнала оишбкн. В случае невыполнения указанной последовательности поступления перечисленных сигналов в блок 10 (например, сигнал прерывания поступает раньше сигнала совпадения от схемы 7 или между последовательным поступлением сигнала совпадения исигнала прерывания фиксируется наличие .не одного сигнала ИНФ-А, соответствующего байту контрольной суммы, а нескольких) блок 10 вырабатывает сигнал Меньше или Больше, который выдается в блок 16.

Одновременно с описываемЕЛм процессом блок 15 выдает на первую группу элементов И 11 двоичное число, имеющее, как бьшр указано выше, во всех своих разрядах единичные значения в случае равенства контрольной сумг« ы, принятой от канала, и контрольной сумгФ, вычисленной при приемемассива данных. В этом случае, а также при наличии сигналов, поступающих на первые и вторые управляющие входы первой группы элементов И 11, последняя выдает сигнал Контрольная сумма верна в блок 16 форми зования сигнала сяиибки. В случае неравенства указанных контрольных сумм сумма байтов их прялюго и инверсного значений представляет собой-двоичное число, не содрежамее во всех разрядах единичные значения, что фиксируется первой группой элементов И 11, и в блок формирования сигнала поступает сигнал Контрольная сумма неверна .

Таким образом,, в устройстве осуществляется контроль достоверности принимаемой информации.

В режиме выдачи данных блок 3 управления зьвдает сигнал разрешения выдачи, который поступает на группу

JQ элементов И 2 выдачи данных, подготавливая их к открыванию, и в блок 8 синхронизации. Одновременно блок 3 подает на информационные входы группы элементов и 2 первый байт данных и транслирует в канал сигнал ИНФ-А,

15 сообщая о готовности .передачи первого байта данных. По сигналу ИНФ-А блок 8 формирует стробирующий импульс который открывает группу элементов И 2, и первый байт данных поступает

20 в канал. Приняв первый байт данных, канал выставляет сигнап ИНФ-К, поступающий в блоки 3 и 8. В блоке 8 по сигналам ИНФ-А и ИНФ-К фиксируется передача первого байта данных. По

25 сигналу ИНФ-К блок 3 сбрасывает .сигнал ИНФ-А. Канал реагирует на это сбросом сигнала ИНФ-К, после чего блок 3 выставляет на информационные входы группы элементов И 2 следующий

30 байт информации, процесс передачи которого происходит аналогично.

В процессе выдачи .данных, так же как и при приеме данньес, блок 8 фиксирует количество выданных единиц информации, которое подается на первые входы схемы 7. Схема 7 непрерывно сравнивает текущий формат данных с заданньий форматом, введенным из

блока 4 задания формата обмена данными в процессе выполнения последовательности выборки внешнего устройства каналом. В процессе выдачи данных каждий байт информации с выходом бло.J. ка 3 через вторые входы группы элементов ИЛИ 9 подается на блоки 15 и 14. Блок 14 проверяет каждый выдаваемый байт по четности, и в случае неправильной четности воздействует через блок 16 формирования сигнала ошиб50ки на блок 3 управления, который выставляет в канал сигнал прерывания Ъбмена. В случае правильной четности выдаваемых байтов информации последние .суммируются в блоке 15. Вычис TieHKOe значение контрольной суммы поступает из блока 15 на информационные входы второй группы элементов И 12, на управляющий вход которого подается сигнал с выхода схемы 7. После вы

60 дачи последнего байта массива данных схема сравнения фиксирует равенство ЗЕщанного и текущего формата данных и выдает сигнал совпадения который открывает вторую группу элементов И

„5 12. При этом байт контрольной суммл

через группу элементов И 2 выдачи данных поступает в канал.

Таким образом, в режиме передачи данных устройство обеспечивает контроль, достоверности выдаваемой информации .

Предлагаемое устройство для приема и выдачи информации выгодно отличается от аналогичных, известных ранее, тем, что существенно повышает достоверность передаваемой и принимаемой информации, повышает эффективность контроля обмена информацией, позволяет сократить время для локализации отказов в тракте передачи информации и упрост 1ть задачи диагностики; кроме того, эксплуатация и ремонт предлагаемого устройства - проще.

Формула изобретения

Устройство для приема и выдачи информации с контролем ошибок, содержащее блок управления, блок синхронизации, блок задания формата обмена данными, схему сравнения, группу элементов И приема данных, группу элементов И выдачи данных, причем информационные входы устройства соединены с первыми входами группы элементов И приема данных и блока задания формата обмен данными, управляющий вход которого соединен с первым выходом блока управления, а выходы - соединены с первой группой входов схемы сравнения, выходы группы элементов И приема данных соединены с информационными входами блока управления, второй выход которого соединен с управляющим входом группы элементов И приема данных и с первым входом блока синхронизации, вход признака информации канала устройства соединен с первым входом блока управления и со вторым входом блока синхронизации, информационные выходы которого соединены со второй группой входов схемы сравнения, вход прерывания устройства соединен со вторым входом блока управления, выход признака информации абонента блока управления соединен с третьим входом блока, синхронизации и является выходом устройства, информационные выходы блока управления- соединены с первыми входами группы элементов И выдачи данных, выходы которых являются информационными выходами устройства, третий выход блока управления соединен с управляющим входом .группы элементов И выдачи данных и с

четвертым входом блока синхронизации, стробирующий выход которого соединен со стробирующими входами групп элементов И приема и выдачи данных, о тличающееся тем, что, с целью повышения достоверности приема и выдачи информации, в устройство введены блок оценки формата данных, блок формирования сигнала ошибки, селектор, блок вычисления контрольной суммы, блок свертки, две группы элементов И, группа элементов ИЛИ, группа элементов НЕ и элемент задержки, причем выходы группы элементов И приема данных соединены непосредственно и через группу элементов НЕ со входами селектора, выход которого-соединен с первыми входами группы элементов ИЛИ, информационные выходы блока управления соединены со вторыми входами группы элементов ИЛИ, выходы которых соединены со входами блока свертки и блока вычисления контрольной суммы, информационные выходы блока свертки соединены с первой группой входов блока формирования сигнала ошибки, выход разрешения суммирования блока свертки соединен с управляющим входом блока вычисления контрольной суммы, выходы которого соединены с информационными входами первой и рторой групп элементов И, вход прерывания устройства соединен с первым входом блока оценки формата данных и с первым управляющим входом первой группы элементов И, второй управляющий вход которой соединен со вторым входом блока управления, а выходы - со второй группой выходов блока формирования сигнала ошибки, выход признака информации абонента блока управления, соединен со вторым входом блока оценки формата данных, выход cxeNttJ сравнения соединен с управляющим входом второй группы элементов И, с третьим входом блока оценки форЦата данных и через элемент задержкиt управляющим входом селектора,выходы блока оценки формата данных соединены с третьей группой входов бло.ка формирования сигнала ошибки, выход которого соединен с третьим входом блока управления, выходы второй группы элгментов И соединены с информационными входами группы элементов И выдачи данных .

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР 359645, кл. Q 06 Р 3/04, 1971.

2.Авторское свидетельство СССР 309357, кл. q 06 Р 3/04, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор канала | 1991 |

|

SU1839250A2 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1256036A1 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

| Многоканальный адаптер | 1987 |

|

SU1495806A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1986 |

|

SU1363226A1 |

| Устройство для приемопередачи информации с контролем ошибок | 1987 |

|

SU1425757A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Имитатор канала | 1985 |

|

SU1287160A1 |

| Имитатор канала | 1983 |

|

SU1174927A1 |

Авторы

Даты

1978-06-15—Публикация

1976-03-02—Подача