4 Ю

СП

ел

ч|

1} 42575

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре передачи, приема и обработки информации.

Цель изобретения-- повышение инфор - мативности И функциональной надежности устройства.

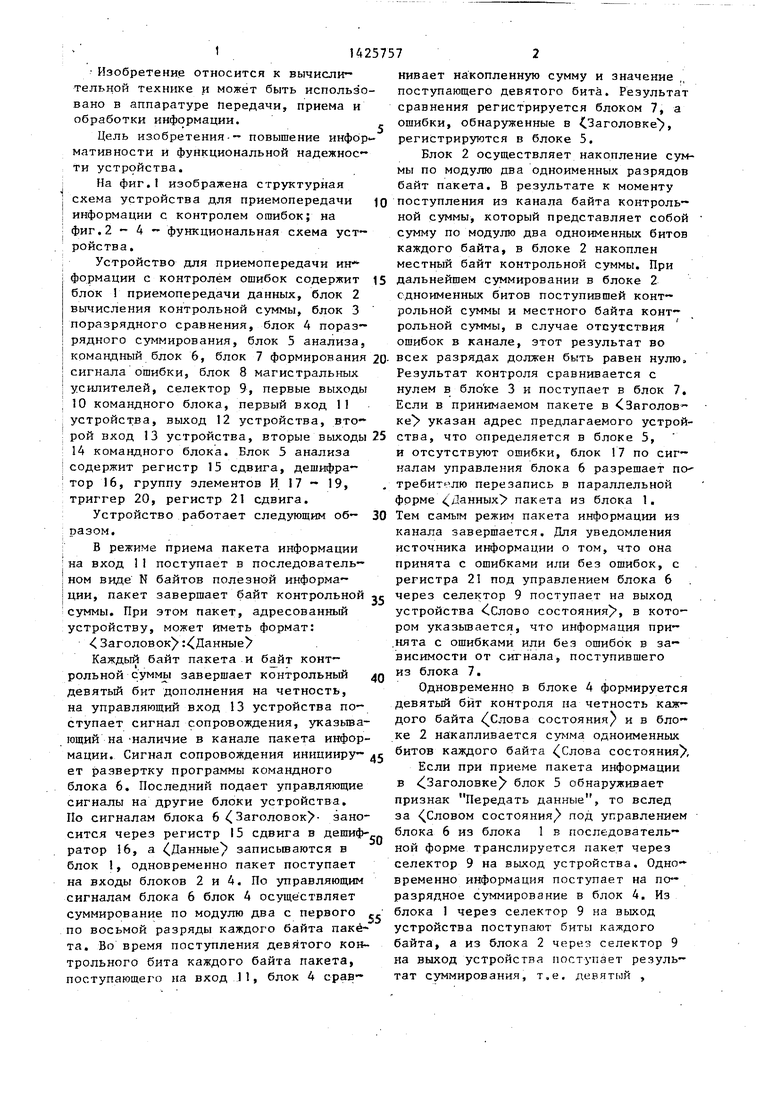

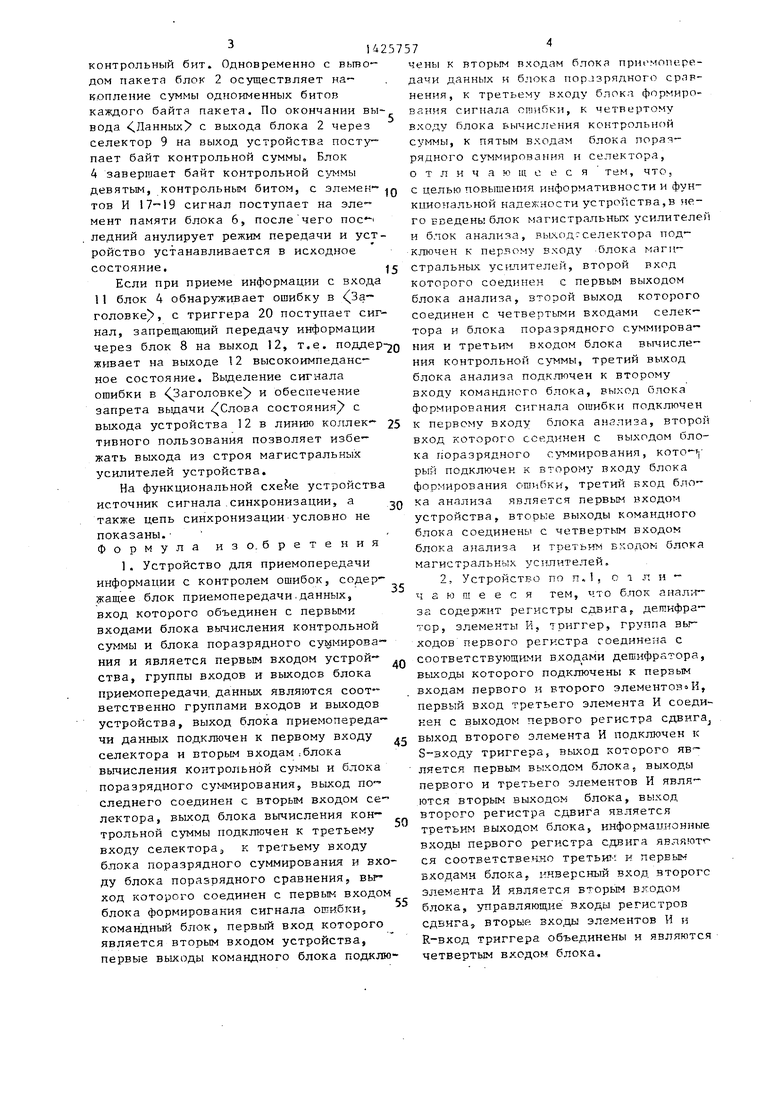

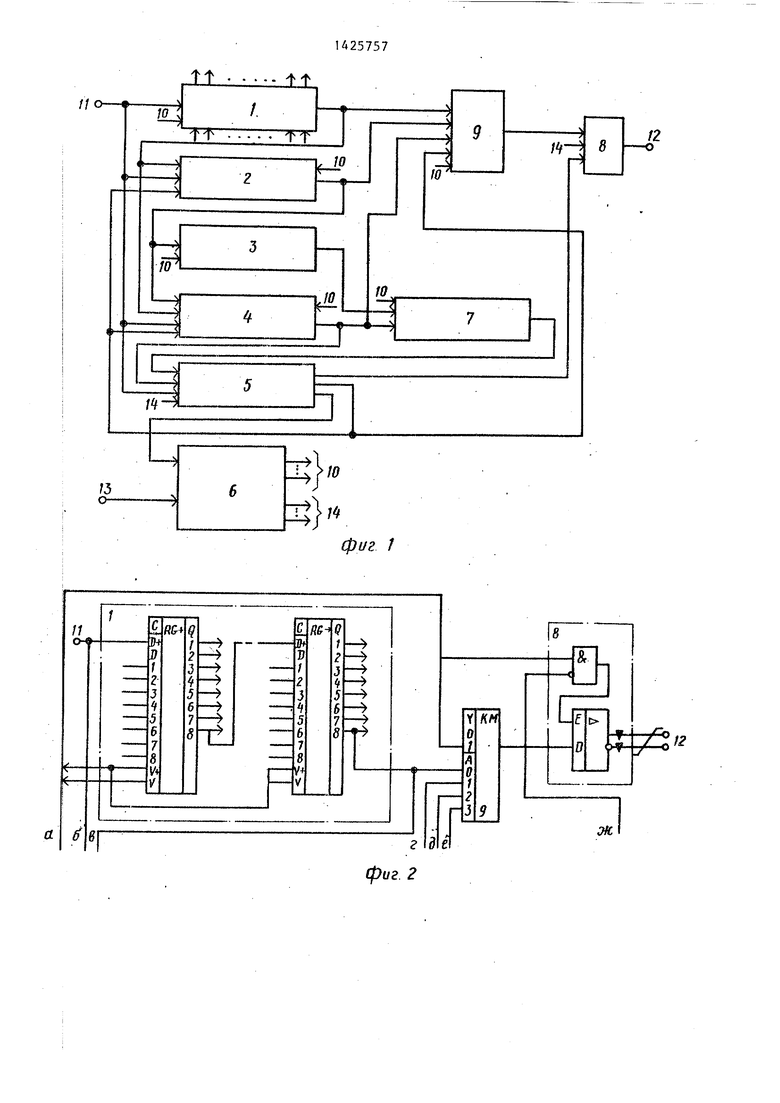

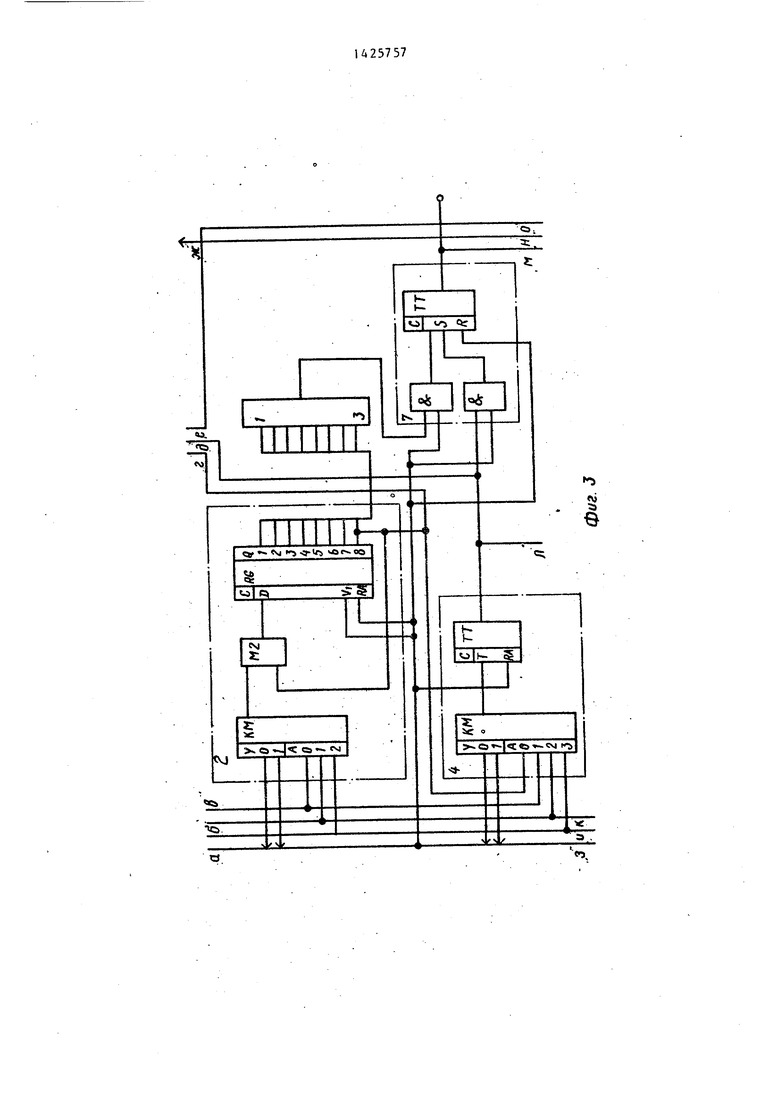

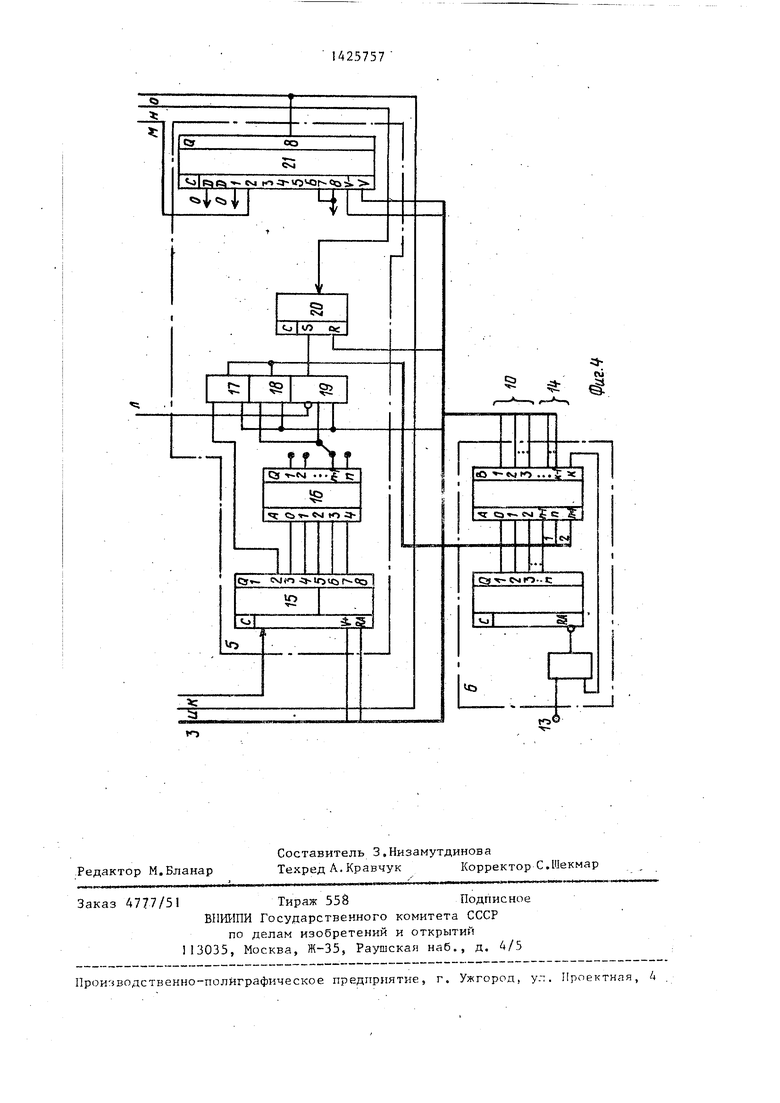

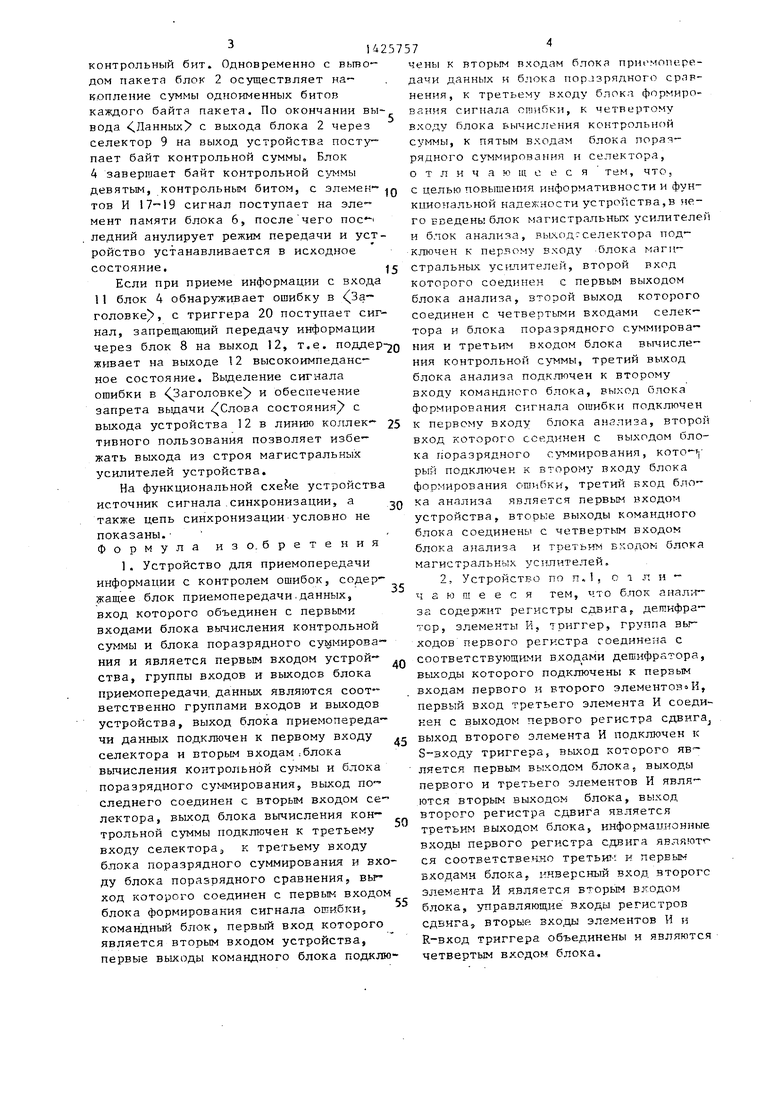

На фиг.1 изображена структурная схема устройства для приемопередачи Q информации с контролем ошибок; на фиг,2 - 4 - функциональная схема устройства.

Устройство для приемопередачи ин- формации с контролем ошибок содержит 15 блок приемопередачи данных, блок 2 вычисления контрольной суммы, блок 3 поразрядного сравнения, блок 4 поразнивает накопленную сумму и значение поступающего девятого бита. Результат сравнения регистрируется блоком 7, а ошибки, обнаруженные в Заголовке), регистрируются в блоке 5.

Блок 2 осуществляет накопление суммы по модулю два одноименных разрядов байт пакета. В результате к моменту поступления из канала байта контрольной суммы, который представляет собой сумму по модулю два одноименных битов каждого байта, в блоке 2 накоплен местный байт контрольной суммы. При дальнейшем суммировании в блоке 2 одноименных битов поступившей контрольной суммы и местного байта контрольной суммы, в случае отсутствия

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приемопередачи информации с контролем ошибок | 1985 |

|

SU1277166A1 |

| Устройство для сопряжения магистрали с ЦВМ | 1988 |

|

SU1569837A1 |

| Устройство ввода-вывода с контролем ошибок и индикацией | 1989 |

|

SU1728866A1 |

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| Устройство для коррекции ошибокС САМОКОНТРОлЕМ | 1977 |

|

SU796847A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| МИКРО-ЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 2000 |

|

RU2209462C2 |

| Устройство для контроля переписи информации перезагружаемой управляющей памяти процессора | 1981 |

|

SU1008746A1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

Изобретение относится к вычисли- тельной технике и может быть исполь зовано в .устройствах приема, передачи и обработки информации. Цель изобретения - повышение информативности и функциональной надежности. Устройство позволяет подключать несколько устройств к одной линии коллективного : пользования, при этом устройства различаются адресом, заложенным в -СЗа- головок за счет того, что реализует ся решающая обратная связь, по результатам контроля принятого сообщения формируется признак, указанный в Слове состояния, -при обнаружении ошибок в - Заголовке устройство не формирует на выход Слово состояния, поэтому исключается возможность выхода из строя магистральных усилителей. 2 з,п, ф-лы, 4 ил. S

рядного суммирования, блок 5 анализа,ошибок в канале, этот результат во командный блок 6, блок 7 формирования 20-всех разрядах должен быть равен нулю, сигнала ошибки, блок 8 магистральныхРезультат контроля сравнивается с усилителей, селектор 9, первые выходынулем в бло ке 3 и поступает в блок 7, 10 командного блока, первый вход 11Если в принимаемом пакете в СЗнголов устройства, выход 12 устройства, вто-кеУ указан адрес предлагаемого устрой- рой вход 13 устройства, вторые выходы 25ства, что определяется в блоке 5,

14 командного блока. Блок 5 анализа содержит регистр 15 сдвига, дешифратор 16, группу элементов И 17 - 19, триггер 20, регистр 21 сдвига.

Устройство работает следующим образом.

В режиме приема пакета информации на вход 1 поступает в последовательном виде N байтов полезной информа-

Iции, пакет завершает байт контрольной « через селектор 9 поступает на выход

суммы. При этом пакет, адресованный устройству, может иметь формат: Заголовок) :( Данные Каждый байт пакета и байт контрольной суммы завершает контрольный 40 девятый бит дополнения на четность, на управляющий вход 13 устройства поступает сигнал сопровождения, указывающий на Наличие в канале пакета инфорустройства 1Слово состояния, в котором указьшается, что информация принята с ошибками или без ошибок в зависимости от сигнала, поступившего из блока 7.

Одновременно в блоке 4 формируется девятый бит контроля на четность каждого байта Слова состояния) и в блоке 2 накапливается сумма одноименных

Сигнал сопровождения иницииру- 45 битов каждого байта Слова состояния).

50

мации.

ВТ развертку программы командного блока 6. Последний подает управляющие сигналы на другие блоки устройства. По сигналам блока 6 Оаголовок - заносится через регистр 15 сдвига в дешифратор 16, а Данные записьшаются в блок 1, одновременно пакет поступает на входы блоков 2 и 4. По управляющим сигналам блока 6 блок 4 осуществляет суммирование по модулю два с первого ,, по восьмой разряды каждого байта пакета. Во время поступления девятого контрольного бита каждого байта пакета, поступающего на вход 11, блок 4 сравЕсли при приеме пакета информации в 3аголовке блок 5 обнаруживает признак Передать данные, то вслед за Словом состояния под управлением блока 6 из блока 1 в последовательной форме транслируется пакет через селектор 9 на выход устройства. Одновременно информация поступает на поразрядное суммирование в блок 4. Из блока 1 через селектор 9 на выход устройства поступают биты каждого байта, а из блока 2 через селектор 9 на выход устройства поступает результат суммирования, т.е. девятый ,

и отсутствуют ошибки, блок 7 по сигналам управления блока 6 разрешает по . требителю перезапись в параллельной

форме Данных пакета из блока 1. 30 Тем самым режим пакета информации из канала завершается. Для уведомления источника информации о том, что она принята с ошибками или без ошибок, с регистра 21 под управлением блока 6

устройства 1Слово состояния, в котором указьшается, что информация принята с ошибками или без ошибок в зависимости от сигнала, поступившего из блока 7.

Одновременно в блоке 4 формируется девятый бит контроля на четность каждого байта Слова состояния) и в блоке 2 накапливается сумма одноименных

битов каждого байта Слова состояния).

Если при приеме пакета информации в 3аголовке блок 5 обнаруживает признак Передать данные, то вслед за Словом состояния под управлением блока 6 из блока 1 в последовательной форме транслируется пакет через селектор 9 на выход устройства. Одновременно информация поступает на поразрядное суммирование в блок 4. Из блока 1 через селектор 9 на выход устройства поступают биты каждого байта, а из блока 2 через селектор 9 на выход устройства поступает результат суммирования, т.е. девятый ,

контрольный бит. Одновременно с вьто- дом пакета блок 2 осуществляет накопление суммы одноименных битов каткдого байта пакета. По окончании вывода Данных с выхода блока 2 через селектор 9 на выход устройства поступает байт контрольной суммы. Блок 4 завершает байт контрольной суммы девятым, контрольным битом, с элемен- тов И 17-19 сигнал поступает на элемент памяти блока 6, после чего ледний анулирует режим передачи и устройство устанавливается в исходное состояние.

Если при приеме информации с входа 11 блок 4 обнаруживает ошибку в 3а головке, с триггера 20 поступает сигнал, запрещающий передачу информации

чены к вторым входам блока npHt Monepe- дачи данных и блока поразрядного српр- нения, к третьему входу блока формиро- вания сигнала ошибки, к четвертому входу блока вычисления контрольной суммы, к пятьсм входам блока поразрядного суммирования и селектора, отличающееся тем, что, с целью повыше1да:я информативности и фун- кпиональной надежности устройства,в него введены блок магистральных усилителе и блок анализа, выход:селектора подключен к первому входу блока магистральных усилителей, второй вход которого соединен с первым выходом блока анализа, второй выход которого соединен с четвертыми входами селектора и блока поразрядного суммирова-

через блок 8 на выход 12, т.е. поддер-20 ия и третьим входом блока вычисле- живает на выходе 12 высокоимпеданс- „ия контрольной суммы, третий выход

ное состояние. Выделение сигнала ошибки в 3аголовке и обеспечение запрета вьздачи Слова состояния) с выхода устройства 12 в линию коллек- тивного пользования позволяет избежать выхода из строя магистральных усилителей устройства.

На функциональной cxefie устройства источник сигнала.синхронизации, а также цепь синхронизации условно не

показаны.

Формула изо. бретения

25

30

блока анализа подключен к второму входу командного блока, выход блока формирования сигнала ошибки подключен к первому входу блока анзотиза, второй вход которого соединен с выходом блока поразрядного суммирования, кото-у подключен к второму входу блока формирования ошибки, третий вход блока анализа является первым входом устройства, вторые выходы командного блока соединены с четвертым входом блока анализа и третьим вкодом блока магистральных усилителей,

2, Устройство по п.1, о 1 л и - ч а ю ш е е с я тем, что блок анал;-г за содержит регистры сдвига,, дешифратор, элементы И, триггер, группа выходов первого регистра соединена с соответствующими входами дешифратора, выходы которого подключены к первым входам первого и второго элементоваК, первый вход третьего элемента И соеди- иен с выходом первого регистра сдвига j5 выход второго элемента И подключен к 8 зходу триггера, выход которого яв ляется первым выходом блока, выходы первого и третьего элементов И являются вторым выходом блока, вы.ход второго регистра сдвига является третьим выходом блока информационные входы первого регистра сдвига являют Г ся соответстве.н.ко третьи -: и первым входами блока, инверсный вход второго элемента И является вторым входом блока, управляющие входы регистров сдвига5 вторые вхо,цы элементов И и R-вход триггера объединены и являются четвертым входом блока.

35

40

50

55

чены к вторым входам блока npHt Monepe- дачи данных и блока поразрядного српр- нения, к третьему входу блока формиро- вания сигнала ошибки, к четвертому входу блока вычисления контрольной суммы, к пятьсм входам блока поразрядного суммирования и селектора, отличающееся тем, что, с целью повыше1да:я информативности и фун- кпиональной надежности устройства,в него введены блок магистральных усилителе и блок анализа, выход:селектора подключен к первому входу блока магистральных усилителей, второй вход которого соединен с первым выходом блока анализа, второй выход которого соединен с четвертыми входами селектора и блока поразрядного суммирова-

ия и третьим входом блока вычисле- „ия контрольной суммы, третий выход

5

0

блока анализа подключен к второму входу командного блока, выход блока формирования сигнала ошибки подключен к первому входу блока анзотиза, второй вход которого соединен с выходом блока поразрядного суммирования, кото-у подключен к второму входу блока формирования ошибки, третий вход блока анализа является первым входом устройства, вторые выходы командного блока соединены с четвертым входом блока анализа и третьим вкодом блока магистральных усилителей,

2, Устройство по п.1, о 1 л и - ч а ю ш е е с я тем, что блок анал;-г за содержит регистры сдвига,, дешифратор, элементы И, триггер, группа выходов первого регистра соединена с соответствующими входами дешифратора, выходы которого подключены к первым входам первого и второго элементоваК, первый вход третьего элемента И соеди- иен с выходом первого регистра сдвига j5 выход второго элемента И подключен к 8 зходу триггера, выход которого яв ляется первым выходом блока, выходы первого и третьего элементов И являются вторым выходом блока, вы.ход второго регистра сдвига является третьим выходом блока информационные входы первого регистра сдвига являют Г ся соответстве.н.ко третьи -: и первым входами блока, инверсный вход второго элемента И является вторым входом блока, управляющие входы регистров сдвига5 вторые вхо,цы элементов И и R-вход триггера объединены и являются четвертым входом блока.

5

0

0

5

t ttt

фиг /

(рог.

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для приемопередачи информации с контролем ошибок | 1985 |

|

SU1277166A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-26—Подача