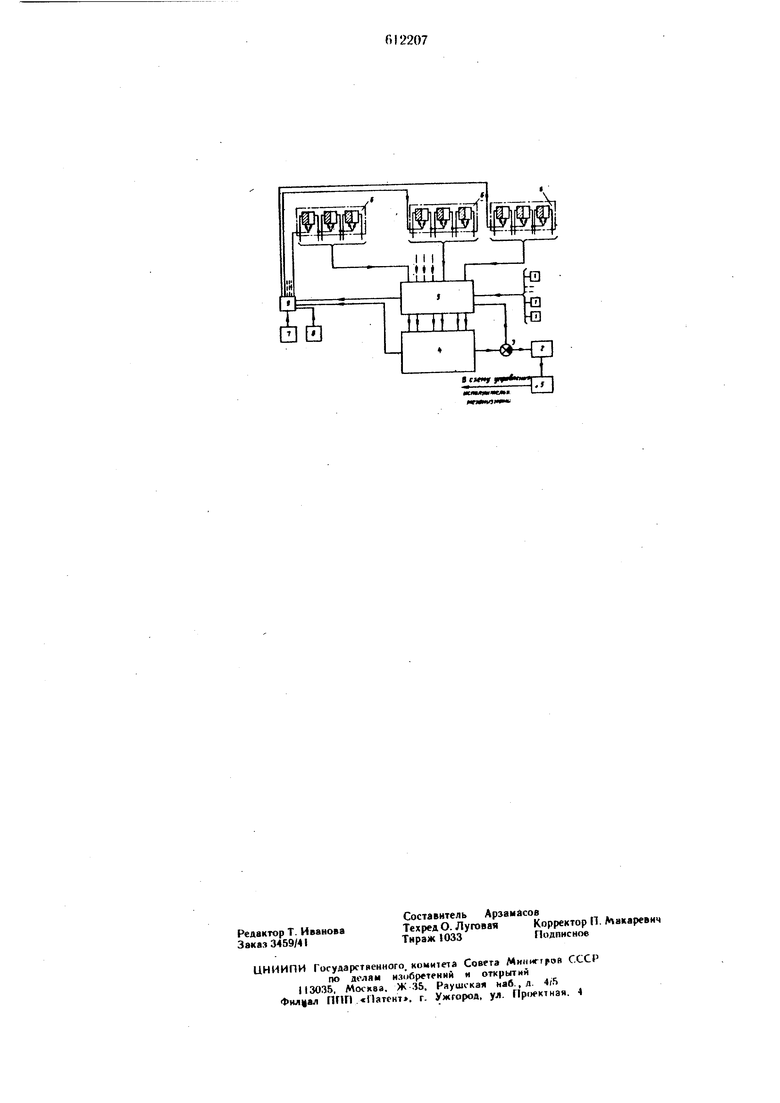

При срабатывании блока 7 поступают сигналы к блокам 6 сдвига тактовых импульсов по времени, сигналы которых поступают черезраспределитель 5 на вход блока 4 квантования уровня параметра. При этом сигнал на выходе первой ячейки соответствующего блока 6 появляется через один период выходного сигнала блока 7, на выходе второй ячейки - через два периода, на выходе третьей ячейки - через четыре периода и т. д. (число ячеек принимается из условия допустимой точности регулировання режимного параметра). Время квантования одного периода регулируется нзмененнем длительности периода колебаний генератора импульсов, встроенного в блок задания частоты тактовых Импульсов 7.

Общее число импульсов, отсчитываемое каждым блоком б, равно числу состояний, т. е. 2, где п - число триггеров. В исходном состоянии все триггеры блоков б находятся в состоянии «О, т. е. одни транзисторы всех триггеров закрыты, а другие открыты.

При поступлении на вход соответствующего блока 6 первого импульса первый триггер переходит в состояние «1, и на правом выходе первого триггера появляется отрицательный потенциал. Второй импульс, поданный на вход блока 6, переводит первый триггер в состояние «О. При этом открывается один из транзисторов триггера, и на его коллекторе появляется нулевой потенциал. Этот сигнал поступает на вход второго триггера и переводит его в состояние «1. Третий импульс, поданный на вход соответствующего блока 6, снова переводит первый триггер в состояние «1 и т, д. Сброс закодированного числа в блоках 6 в исходное состояние осуществляется гюдачей на коллекторы правых транзисторов всех триггеров нулевого потенциала через шину гашения. Состояние «1 всех триггерных ячеек блоков 6, кроме упомянутых выше, продолжается в течение времени одного тактового импульса и паузы, а рабочее состояние первой ячейки каждого блока б определяется продолжительностью паузы между тактовыми импульсами. Блок квантования уровня режимного параметра выдает сигнал на одном из выходов, которые поочередно подключаются через тактовый распределитель 5 к выходам соответствующих блоков 6 сдвига тактовых импульсов по времени для квантования уровня режимного параметра. При в каждом блоке б к. текущий момент времени закодировано определенное число, которое расшифровывается подключаемым тактовым распределителем 5. При расшифровке закодированиого числа (в соответствующем блоке б) происходит срабатывание соответствующих элементов блока 4 и квантование уровня режимного параметра в текущий момент времени в соответствующем объекте управления.

Таким образом, квантование уровня и скорости изменения режимного параметра в каждом объекте управления осуществляется от единого блока 4, что повыи1ает надежность регулятора.

Выбор предельного уровня режимного параметра осуществляется с помощью переключателей, устанавливаемых на панели блока 9, при едином ypoBite регулируемого параметра во всех управляемых объектах устанавливается один переключатель. Прн срабатывании соответствующего элемента блока 4, выбранного переключателем в качестве конечного для формирования предельного уровня параметра, подается сигнал по соответствующему каналу распределителя 5. Прохождение импульса по соответствующему каналу прекращается по окончании процесса управления с помощью устройства 8 контроля длительности процесса в каждом объекте регулирования. При запоминании предельно выбранного уровня режимного параметра соответствующие сигналы поступают на вход соответствующего данному объекту блока б сдвнга тактовых импульсов по времени, что позволяет запомнить закодированное в этом блоке число и поддерживать достигнутый заданный уровень режимного параметра на протяженни всего процесса в управляемом объекте. При этом настройка длительиости управляемого процесса в каждом объекте осуществляется раздельно по каждому каналу, с учетом технологической готовности объектов во времени. Сравнение текущего значения режимного параметра с заданием осуществляется с помощью нуль-органа 3, к которому подключаются через тактовый распределитель 5 соответствующие термодатчикй I.

Формула изобретения

35

Многоканальный регулятор инерционных процессов, содержащий устройство контроля длительности процесса, блок задания частоты тактовых импульсов, тактовый распределитель с

подключенными к нему датчиками и исполнительными механизмами по числу каналов регулирования, блоком управления, нуль органом, подключенным к блокам управления и квантования уровня регулируемого параметра,

отличающийся тем, что, с целью повышения надежности работы регулятора, он содержит блоки сдвига тактовых импульсов по числу kaналов регулирования и блок памяти предельного уровня режимного параметра, входы которого подключены к выходам блока задания

частоты тактовых импульсов, устройства контроля длительности процесса, блоков тактового (распределителя и квантования уровня регулируемого параметра, а выходы через последовательно соединенные блоки сдвига тактовых импульсов и тактовый распределитель подключены к входу блока кваитования уровня регулируемого параметра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный регулятор инерционных процессов | 1979 |

|

SU855611A2 |

| Дискретный регулятор (его варианты) | 1980 |

|

SU960728A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1991 |

|

RU2014740C1 |

| Экстремальный регулятор | 1978 |

|

SU744452A1 |

| Многофазный параметрический стабилизатор постоянного напряжения | 1989 |

|

SU1658130A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Генератор тестов | 1987 |

|

SU1522213A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1980 |

|

SU935914A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

Авторы

Даты

1978-06-25—Публикация

1973-02-19—Подача