(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОК€)В ПОСТОЯННОЙ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство с самоконтролем | 1979 |

|

SU858118A1 |

| Устройство для контроля постоянной памяти | 1979 |

|

SU824316A1 |

| Устройство для контроля блоков постоянной памяти | 1979 |

|

SU881874A1 |

| Устройство для контроля блоков долговременной памяти | 1980 |

|

SU920846A1 |

| Генератор случайного процесса | 1983 |

|

SU1113800A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Генератор случайного процесса | 1985 |

|

SU1739374A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1354196A2 |

| Генератор случайного процесса (его варианты) | 1983 |

|

SU1125624A1 |

| Устройство для обнаружения ошибок в кодовой последовательности | 1989 |

|

SU1780191A1 |

Изобретение относится к запомннающим устройствам.

Известно устройство для контроля блоков постоянной памяти, содержащее регистр со счетным входом, узел установки контрольной суммы и схему сравнения (I). Контроль 14Нформации с помощью та.кого устройства осуществляется путем сравнения, суммы всех содержащихся в устройстве чисел по модулю два с-заранее пОдсчитаиной константой.

Недостатком этого устройства является низкая точность контроля и сложность определения адреса ощийки. .

Из известных устройств наиболее близким во техническому решению к предлагаемому является устройство для контроля блоков постоянной памяти, содержащее регистр адреса, подключенный через дешифратор адреса к выходу устройства, вход которого через регистр числа соединен с сумматором, подключенным к блоку управления (2J. Это устройство автоматически контролирует блоки постоянной памяти по модулю три н .циклической сумме, образуемой путем суммирования всех содержащихся в блоке памяти чесел с переносом единицы переполнения из старшего разряда в младший.

Недостатками этого устройства являются пропуск некоторого вида ошибок (неправильное распределение информации по адресам, перестановка частей информации местами,

взаимокомпенснрующиеся ошибки) и снижение точности контроля при отсутствни в числах контрольных кодов по модулю три.

Цель изобретения - повышение .точности контроля.

Поставленная цель достигается тем, что устройство для контроля блоков постоянной памяти содержит блок задания циклов суммирования, входы которого подключены соответственно к выходам регистра адреса и блока управлення, а выходы - к входам сум.матора и блока управления.

Это позволяет считывать числа из блока постоянной памяти несколько раз, образуя каждый раз новую контрольную сумму, и сравни.вать полученные суммы с контрольными константами.

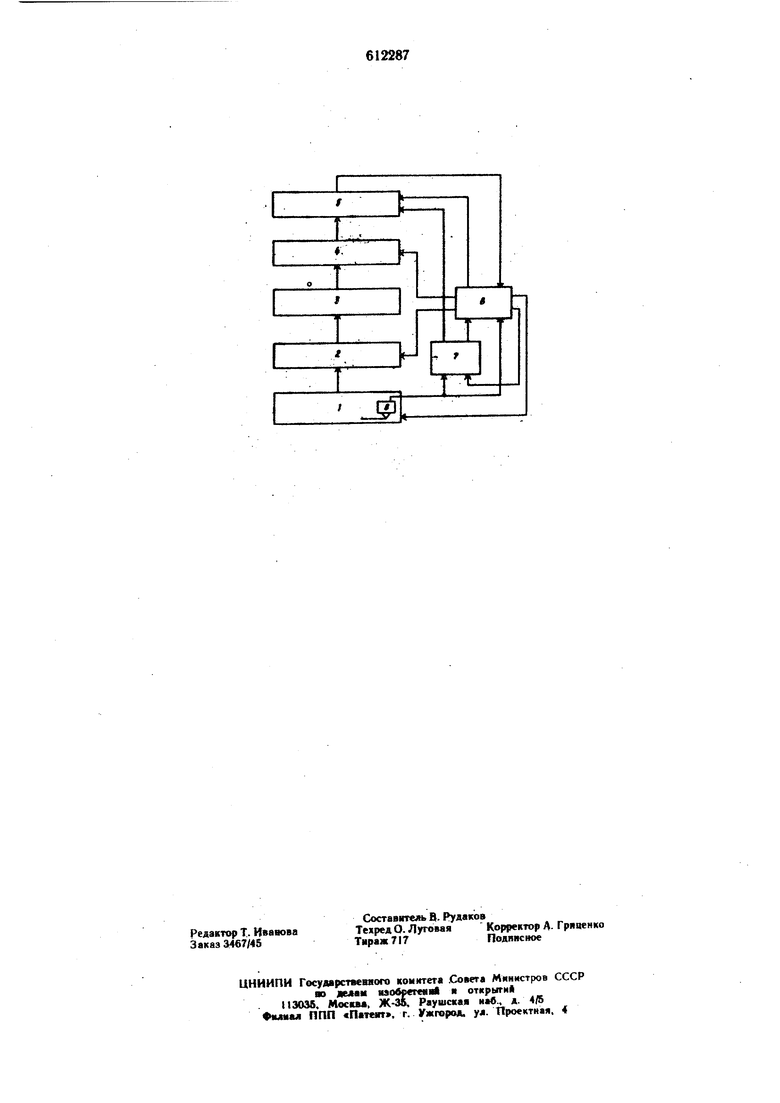

Ни чертеже изображена структурная схема устройства.

Устройство содержит триггерами регистр адреса I, дешифратор адреса 2, подключаемый к проверяемому блоку постоянной памяти 3,

числовой регистр 4, сумматор 5, блок управления 6 н блок 7 задания циклов суммирования 7 входы которого подключены соответствен Но к выходам регистра адреса 1 н блока управления 6, а выходы - к входам сумматора б и блока упраалення 6.

Проверяемый блок постоянной памяти 3, кроме контролируемых чисел, дополнительно содержит контрольные константы, с помощью которых осуществляется контроль. Константами являются либо циклические суммы, либо суммы по модулю два. Количество контрольных констант зависит от объема блока гюстоянной памяти и от возможного количества н своеобразия ошибок, вызванных особенностями конструкции и технологии изготовления блока. НаприМер, первая контрольная константа является циклической суммой всех чисел. Вторая контрольная константа является циклической суммой чисел, полученных путем циклического сдвига в одну сторону каждого последующего числа, считанного с блока постоянной памяти относительно предыдущего на П| разрядов. Третья контрольная константа является циклической суммой чисел, полученных путем циклического сдвига в одну сторону каждого последующего считанного числа отйоснтельно предыдущего на Пг разрядов и т. д. Сумматор 5 предназначен для получения циклических контрольных сумм или сумм по модулю два. Для получения второй, третьей и т. д. контрольных сумм сумматор 5 имеет цепи циклического сдвига, которые управляются блоком 7 задании циклов суммирования. Сумматор 5 имеет индикацию, что позволяет производить контроль блока постоянной памяти 3 при отсутствии в последнем контрольных констант. Блок 7 задания циклов суммирования предназначен для организации второго, третьего и последующих циклов суммирования, при которых вырабатываются импульсы цнгьлического сдвига содержимого сумMaTopai 5 на ni разрядов при втором суммировании, на Па разрядов при третьем суммировании и т. д. Блок управления G предназначен для выработки ие(ходнмых упраш{яющих сигналов, для организации работы устройства контроля и имеет органы управления для переключения режимами работы.

Устройство в автоматическом режиме работает следующим образом.

Под в оздействием управляющих импульсов блока управления 6 регистр адреса I вырабатывает последовательные адреса. У проверяемого блока постоянной памяти 3 последовательно по выработанным адресам считываются на числовой регистр 4 числа. Затем каждое число засылается в сумматор 5. Импульсы циклического сдвига при первом суммировании не вырабатываются. После суммирования всех чисел сигнал переполнения с выхода триггера 8 старшего разряда адресного регистра I поступает на вход блока 7 заданий

ЦИКЛОВ суммироваиия и блок управления 6. Один выход блока 7 дает разрешение на прохождение сигналов сдвига сумматора 5, вырабатываемых блоком управления 6 при последующих циклах суммирования, а другой выход блока 7 определяет количество вырабатываемых блоком управления 6 импульсов сдвига в зависимости от номера цикла суммирования. Блок управления по сигналу переполнения вырабатывает сигналы, которые сравнивают результат суммирования с соответствующей контрольной константой. При положительных результатах контроля блок управления 6 вырабатывает сигналы для образования второй контрольной суммы, но при этом перед каждой засылкой числа в сумматор 5 содержимое последнего циклически сдвигается в одту и ту же сторону на П| разрядов, определяемых выходом блока 7 задания циклов суммирования, в следующем цикле суммирования содержимое сумматора сдвигается на п 2 разрядов и т. д. В конце каждого цикла полученные суммы сравниваются с KOHCI антами. При отрицательных результатах сравнения вырабатывается сигнал «Останов. После записи оператором отличий полученной неправильной суммы от константы проверка продолжается вплоть до полного завершения всех проверок. После завершения последнего цикла суммирования блок 7 задания циклов суммирования через блок управления 6 вырабатывает сигнал «Останов, при этом, если все полученные суммы совпали с константами, блок управления 5 вырабатывает сигнал «Исправно.

Так как каждому числу ставится в соответствие определенная константа сдвига, которая зависит от адреса числа, то ощибки, ироявляюшиеся в неправильном распределении информации по адресам, будут обнаружены. Обнаруживается так же большинство ошибок, взаимокомпенсирующихся при обычном циклическом суммировании.

Формула изобретения

Устройство для контроля блоков постоянной памяти, содержащее регистр адреса, подключенный через дешифратор адреса к выходу устройства, вход которого через регистр числа соединен с сумматором, подключенным к блоку управления, отличающееся тем, что, с целью повышения точности контроля, оно содержит блок задания циклов суммирования, входы которого пЬдключены соответственно к выходам регистра -адреса и блока управления, а выходы - к входам сумматора и блока управления.

Источники информации, принятые во внимание при экспертизе;

S. Авторское свидетельство Я 235108, М.кл. G С 29/00, 1967.

Авторы

Даты

1978-06-25—Публикация

1975-12-29—Подача