автономный генератор двоичных чисел, суммирование -которых ведется комбинационным сумматором и регистром 5 результата. В процессе работы автономный генератор неизбежно попадает в цикл, параметр которого можно наблюдать в старших разрядах регистра 5 результата. Перед проверкой контролируемого блока 3 в блок 12 памяти должны быть записаны параметры всех циклов, соответствующих исправному контролируемому блоку 3. Введение режима настройки позволяет автоматизировать процесс заполнения ячеек блока 12 памяти. В рабочем режиме блок 13 сравнения осуществляет сравнение числа, содержащегося в регистре 5 результата, с параметрами циклов исправного контролируемого блока

Изобретение относится к вычислительной технике, может найти применение при разработке аппаратуры для контроля исправности узлов цифровых машин и является усовершенствованием известного устройства по авт.сво № 1278854.

Цель изобретения - увеличение оперативности контроля за счет обеспечения возможности получения эталонных откликов.

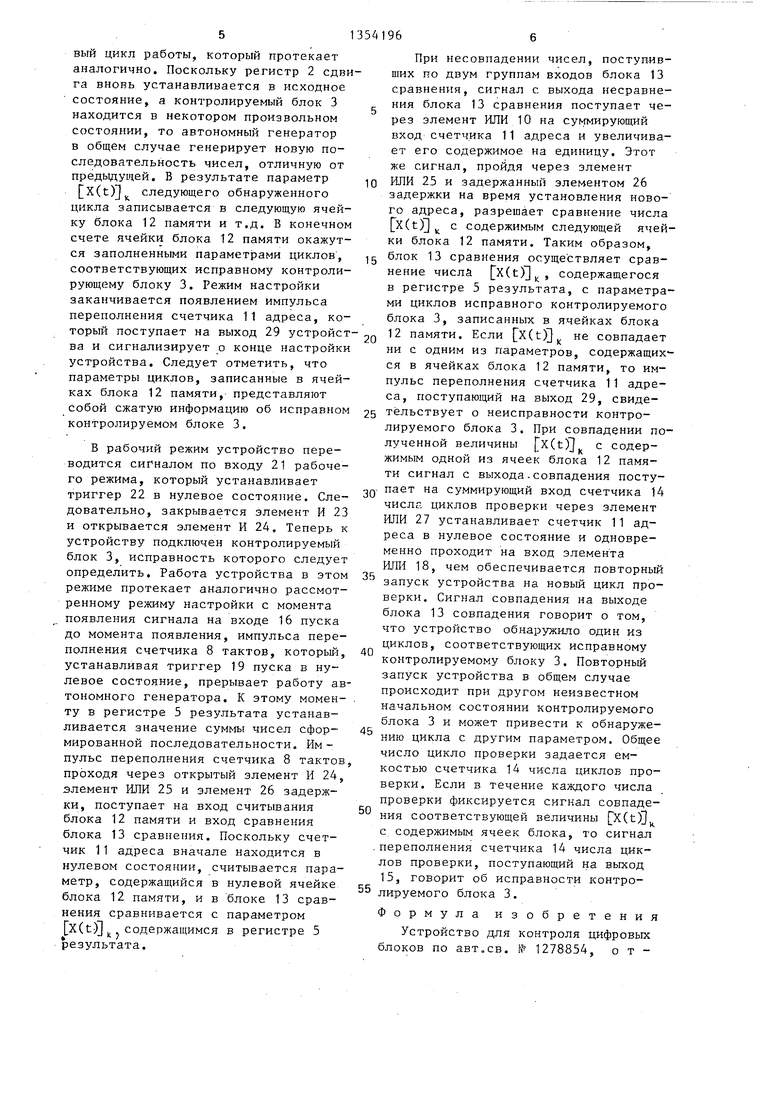

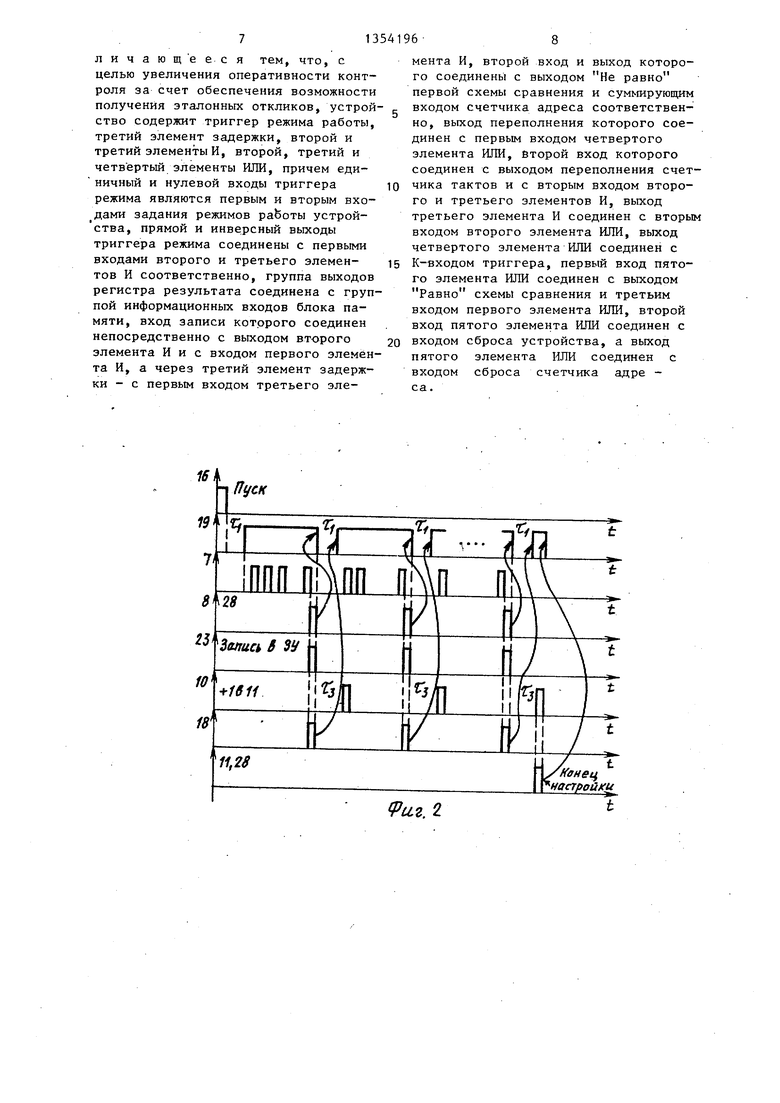

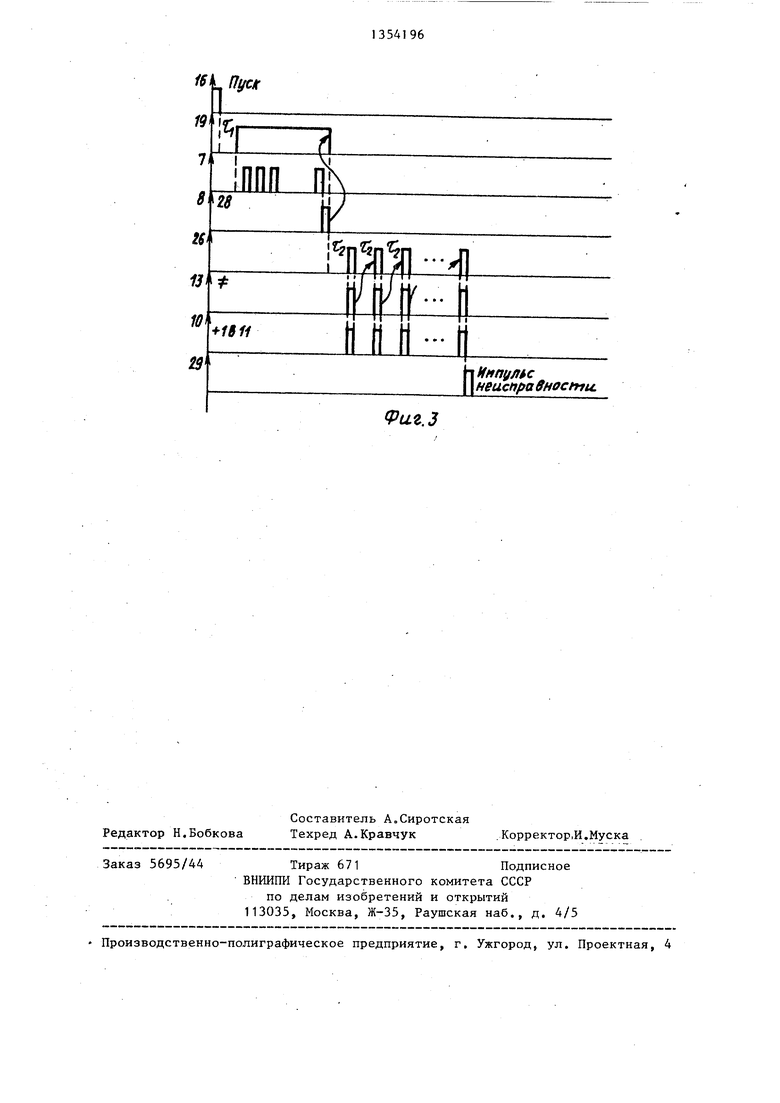

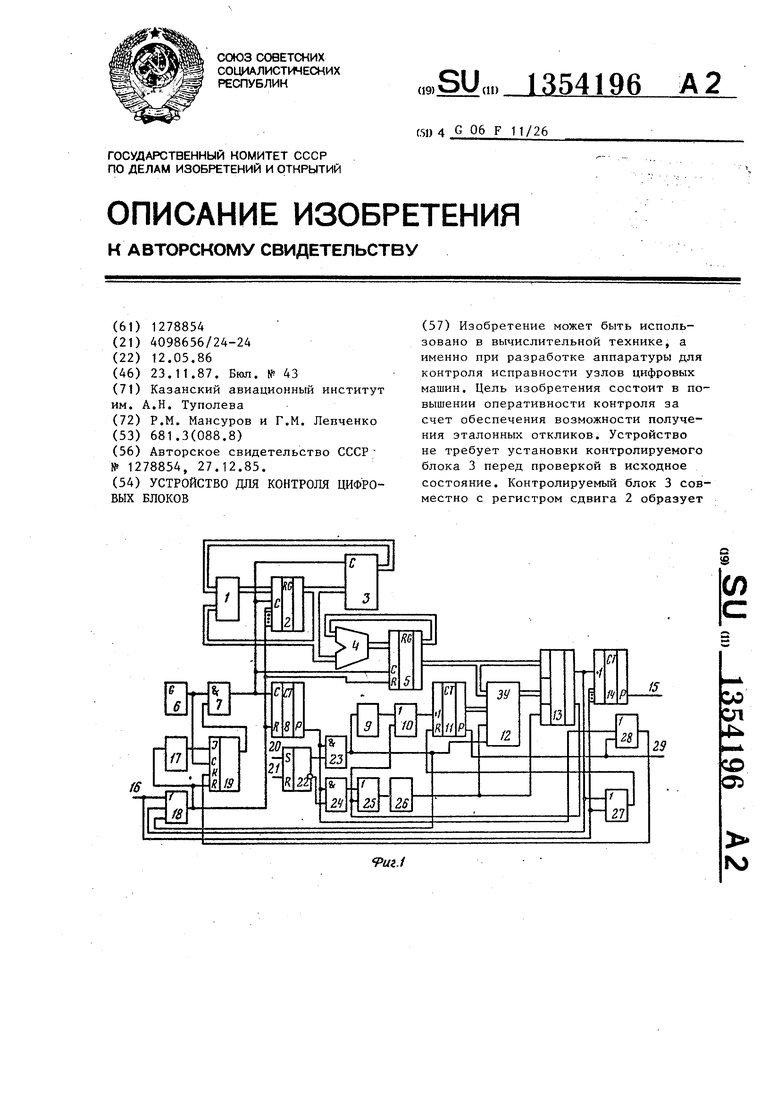

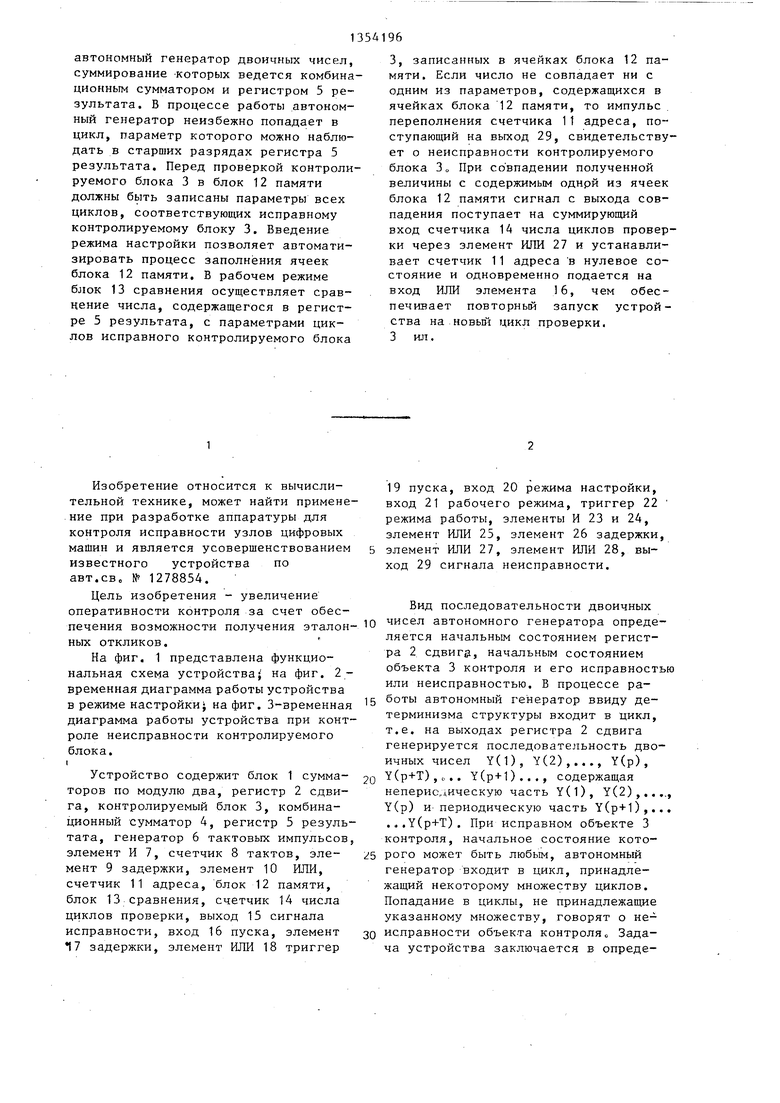

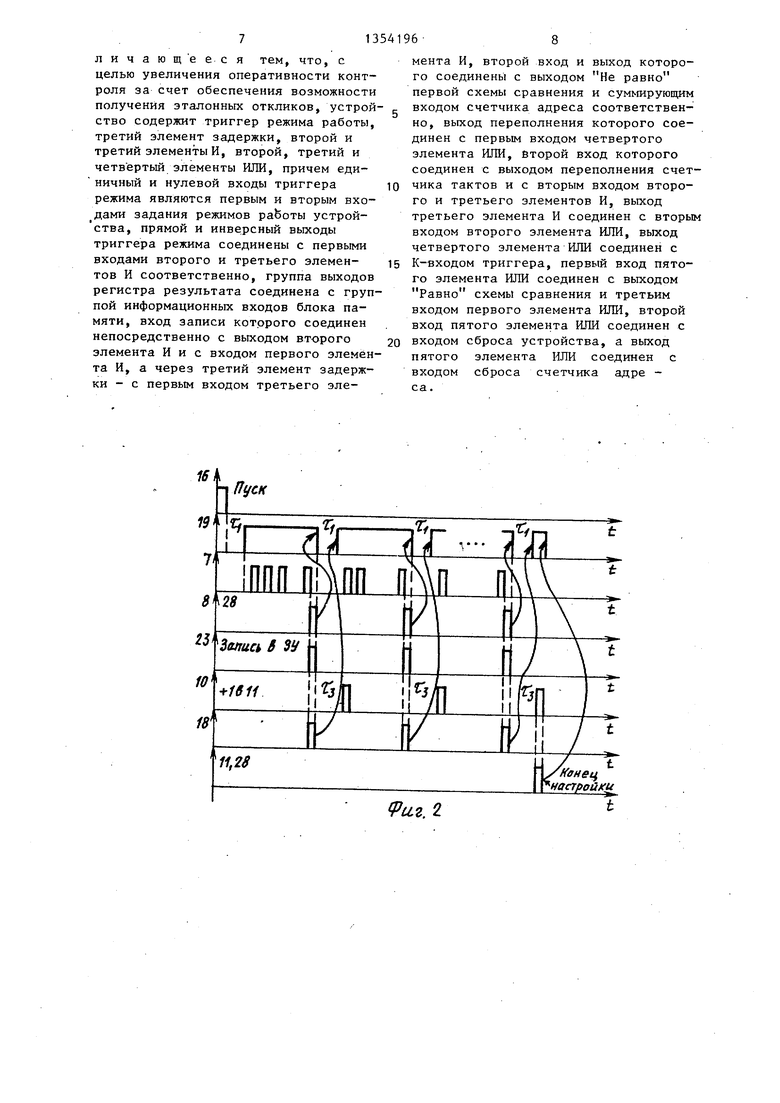

На фиг. 1 представлена функциональная схема устройства; на фиг. 2- временная диаграмма работы устройства в режиме настройки; на фиг. 3-временная диаграмма работы устройст1ва при контроле неисправности контролируемого

блока. I

Устройство содержит блок 1 сумматоров по модулю два, регистр 2 сдвига, контролируемый блок 3, комбинационный сумматор 4, регистр 5 результата, генератор 6 тактовых импульсов, элемент И 7, счетчик 8 тактов, элемент 9 задержки, элемент 10 ИЛИ, счетчик 11 адреса, блок 12 памяти, блок 13 сравнения, счетчик 14 числа циклов проверки, выход 15 сигнала исправности, вход 16 пуска, элемент )7 задержки, элемент ИЛИ 18 триггер

3, записанных в ячейках блока 12 памяти. Если число не совпадает ни с одним из параметров, содержащихся в ячейках блока 12 памяти, то импульс переполнения счетчика 11 адреса, поступающий на выход 29, свидетельствует о неисправности контролируемого блока 3„ При совпадении полученной величины с содержимым однрй из ячеек блока 12 памяти сигнал с выхода совпадения поступает на суммирующий вход счетчика 14 числа циклов проверки через элемент ИЛИ 27 и устанавливает счетчик 11 адреса в нулевое состояние и одновременно подается на вход ИЛИ элемента 16, чем обеспечивает повторный запуск устройства на новьш цикл проверки. 3 ил.

19 пуска, вход 20 режима настройки, вход 21 рабочего режима, триггер 22 режима работы, элементы И 23 и 24, элемент ИЛИ 25, элемент 26 задержки, элемент ИЛИ 27, элемент ИЛИ 28, выход 29 сигнала неисправности.

Вид последовательности двоичных

чисел автономного генератора определяется начальным состоянием регистра 2 сдвига, начальным состоянием объекта 3 контроля и его исправностью или неисправностью. В процессе работы автономный генератор ввиду детерминизма структуры входит в цикл, т.е. на выходах регистра 2 сдвига генерируется последовательность двоичных чисел Y(1), Y(2),..., Y(p),

Y(p+T),c,.. Y(p + 1)..., содержащая

непериодическую часть Y(1), Y(2),...., Y(p) и- периодическую часть Y(p+1),.., .a.Y(p+T). При исправном объекте 3 контроля, начальное состояние которого может быть любым, автономный генератор входит в цикл, принадлежащий некоторому множеству циклов. Попадание в циклы, не принадлежащие указанному множеству, говорят о неисправности объекта контроля« Задача устройства заключается в определении циклов, в которые попадает автономный генератор. В общем случае конкретный цикл характеризуется суммой самих двоичных чисел.

Комбинационный сумматор 4 совместно с накопительным регистром 5 служит для накопления суммы чисел X(t) последовательности, где t - количество суммируемых чисел.

Счетчик 8 служит для задания количества t суммируемых чис ел последовательности. Емкость t счетчика 8 тактов выбирается такой, что самый длинный цикл автономного генератора пройден достаточно большое количеств раз. В этом случае величина xCt) равная значению К старших разрядов X(t), одна и та же для конкретного цикла независимо от начального состо яния объекта контроля. Сумма чисел непериодической части, зависящая от начального состояния объекта контроля, и сумма чисел неполного цикла в конце последовательности сказываются лишь на значениях младших разрядов X(t), которые не учитываются.

Блок 12 памяти служит для хранения параметров циклов, соответствующих эталонному контролируемому объек ту о.

Счетчик 11 адреса служит для хранения адреса считываемой ячейки блока 12 памяти.

Блок 13 сравнения служит для сравнения полученных в процессе контроля величины x(t) 1 с параметрами циклов записанных в ячейках блока 12 памяти.

Счетчик 14 числа циклов проверки задает общее число циклов контроля.

Устройство работает следующим образом. I

В режиме настройки к устройству

подключен эталонный блок. Данный режим задается сигналом, поступающим по входу 20 режима настройки, который устанавливает триггер 22 режима работы в единичное состояние. Работа устройства начинается с приходом сигнала по входу 16 пуска. Этот сигнал устанавливает начальное значение в счетчике 14 числа циклов проверки, сбрасывает в нулевое состояние счетчик 11 адреса, проходя че- рез элемент ИЛИ 27, проходя через элемент ИЛИ 18 устанавливает начальное состояние регистра 2 сдвига, сбрасывает в нулевые состояния регистр 5 результата, счетчик 8 тактов, и триггер 19 пуска. Этот же сигнал, задержанный элементом 17 задержки на время приведения устройства в исходное состояние, устанавливает триггер 19 пуска в единичное состояние. Сигнал с прямого вьжода триггера 19 пуска открывает элемент И 7 и импульсы с выхода тактового генератора 6 поступают на входы синхронизации регистра 2 сдвига, контролируемого блока 3, регистра 5 результата и счетчика 8 тактов. Тактовые импульсы -инициируют работу автономного генератора, состоящего из регистра 2 сдвига, эталонного блока 3 и блока 1 сумматоров по модулю два. С выхода регистра 2 сдвига кодовые комбинации поступают на входы эталонного блока 3, на вход блока 1 сумматоров по модулю два и на вход комбинационного сумматора 4. Реакция на входное воздействие с выхода эталонного блока 3 поступает на вторую Группу входов блока 1 сумматоров по модулю два. Выходные сигналы блока 1 сумматоров по модулю два участвуют в формировании нового значения разрядов регистра 2 сдвига Комбинационный сумматор 4 совместно с регистром 5 результата осуществляет накопление суммы двоичных чисел с выхода регистра 2 сдвига. Число тактов работы автономного генератора определяется емкостью Счетчика 8 тактов, импульс с выхода переполнения которого, проходя через элемент ИЛИ 28, устанавливает нулевое состояние триггера ) пуска, что прерывает поступление тактовьк импульсов в блоки устройства. Одновременно импульс переполнения счетчика 8 тактов, проходя через открытый элемент И 23, поступает на вход записи блока 12 памяти, в нулевую ячейку которого записывается число x(t)j, J являющееся значение К старших разрядов регистра 5 результата, т.е. параметром одного из циклов эталонного блока 3. Импульс с выхода элемента И 23, задержанный элементом 9 задержки, проходя через элемент ИЛИ 10, поступает на суммирующий вход счетчика 11 адресао Тем самым подготавливается для записи информации следующая ячейка блока 12 памяти. Тот же импульс с выхода элемента И 23, проходя через элемент ИЛИ 18, запускает устройство на новый цикл работы, который протекает аналогично. Поскольку регистр 2 сдви га вновь устанавливается в исходное состояние, а контролируемый блок 3 находится в некотором произвольном состоянии, то автономный генератор в общем случае генерирует новую последовательность чисел, отличную от предыдущей. В результате параметр x(t)|| следующего обнаруженного цикла записывается в следующую ячейку блока 12 памяти и т.д. В конечном счете ячейки блока 12 памяти окажутся заполненными параметрами циклов, соответствующих исправному контролирующему блоку 3. Режим настройки заканчивается появлением импульса переполнения счетчика 11 адреса, который поступает на выход 29 устройст ва и сигнализирует о конце настройки устройства. Следует отметить, что параметры циклов, записанные в ячейках блока 12 памяти, представляют собой сжатую информацию об исправном контролируемом блоке 3.

В рабочий режим устройство переводится сигналом по входу 21 рабочего режима, который устанавливает триггер 22 в нулевое состояние. Следовательно, закрывается элемент И 23 и открывается элемент И 24, Теперь к устройству подключен контролируемый блок 3, исправность которого следует определить. Работа устройства в этом режиме протекает аналогично рассмотренному режиму настройки с момента появления сигнала на входе 16 пуска до момента появления, импульса переполнения счетчика 8 тактов, который, устанавливая триггер 19 пуска в нулевое состояние, прерывает работу ав тономного генератора. К этому моменту в регистре 5 результата устанавливается значение суммы чисел сформированной последовательности. Импульс переполнения счетчика 8 тактов проходя через открытый элемент И 24, элемент ИЛИ 25 и элемент 26 задержки, поступает на вход считывания блока 12 памяти и вход сравнения блока 13 сравнения. Поскольку счетчик 11 адреса вначале находится в нулевом состоянии, считывается параметр, содержащийся в нулевой ячейке блока 12 памяти, и в блоке 13 сравнения сравнивается с параметром x(t)j, содержащимся в регистре 5 результата.

При несовпадении чисел, поступивших по двум группам входов блока 13 сравнения, сигнал с выхода несравнения блока 13 сравнения поступает через элемент ИЛИ 10 на суммирующий вход счетчика 11 адреса и увеличивает его содержимое на единицу. Этот же сигнал, пройдя через элемент

10 ИЛИ 25 и задержанный элементом 26 задержки на время установления нового адреса, разрешает сравнение числа X(t) J, с содержимым следующей ячейки блока 12 памяти. Таким образом,

,g блок 13 сравнения осуществляет сравнение числа x(t)|,, содержащегося в регистре 5 результата, с параметрами циклов исправного контролируемого блока 3, записанных в ячейках блока

2д 12 памяти. Если Cx(t)| не совпадает ни с одним из параметров, содержащихся в ячейках блока 12 памяти, то импульс переполнения счетчика 11 адреса, поступающий на выход 29, свиде25 тёльствует о неисправности контролируемого блока 3. При совпадении полученной величины с содержимым одной из ячеек блока 12 памяти сигнал с выхода.совпадения посту20- пает на суммирующий вход счетчика 14 числ. циклов проверки через элемент ИЛИ 27 устанавливает счетчик 11 адреса в нулевое состояние и одновременно проходит на вход элемента ИЛIi 18, чем обеспечивается повторный запуск устройства на новый цикл проверки. Сигнал совпадения на выходе блока 13 совпадения говорит о том, что устройство обнаружило один из циклов, соответствующих исправному контролируемому блоку 3. Повторный запуск устройства в общем случае происходит при другом неизвестном начальном состоянии контролируемого блока 3 и может привести к обнаружению цикла с другим параметром. Общее число цикло проверки задается ем- костью счетчика 14 числа циклов проверки. Если в течение каждого числа проверки фиксируется сигнал совпаде ния соответствующей величины fX(t)J| с содержимым ячеек блока, то сигнал .переполнения счетчика 14 числа циклов проверки, поступающий на выход 15, говорит об исправности контро55 лируемого блока 3.

Формула изобретения

Устройство для контроля цифровых блоков по авт.св. № 1278854, о т 35

40

45

ичающ ееся тем, что, с елью увеличения оперативности контоля за счет обеспечения возможности получения эталонных откликов, устройство содержит триггер режима работы, третий элемент задержки, второй и третий элементы И, второй, третий и четвертый элементы ИЛИ, причем еди- ничный и нулевой входы триггера режима являются первым и вторым входами задания режимов раЬоты устрой- ства, прямой и инверсный выходы триггера режима соединены с первыми входами второго и третьего элементов И соответственно, группа выходов регистра результата соединена с группой информационных входов блока памяти, вход записи которого соединен непосредственно с выходом второго элемента И и с входом первого элемента И, а через третий элемент задержки - с первым входом третьего элемента И, второй вход и выход которого соединены с выходом Не равно первой схемы сравнения и суммирующим входом счетчика адреса соответственно, выход переполнения которого соединен с первым входом четвертого элемента ИЛИ, Второй вход которого соединен с выходом переполнения счетчика тактов и с вторым входом второго и третьего элементов И, выход третьего элемента И соединен с вторым входом второго элемента ИЛИ, выход четвертого элемента ИЛИ соединен с

К-входом триггера, первый вход пятого элемента ИЛИ соединен с выходом Равно схемы сравнения и третьим входом первого элемента ИЛИ, второй вход пятого элемента ИЛИ соединен с

входом сброса устройства, а выход пятого элемента ИЛИ соединен с входом сброса счетчика адре - са.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1985 |

|

SU1278854A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1589280A2 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1196876A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1527636A1 |

| Устройство контроля цифровых блоков | 1985 |

|

SU1339567A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1411750A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для тестирования цифровых блоков | 1988 |

|

SU1656540A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1302285A1 |

Изобретение может быть использовано в вычислительной технике, а именно при разработке аппаратуры для контроля исправности узлов цифровых машин. Цель изобретения состоит в повышении оперативности контроля за счет обеспечения возможности получения эталонных откликов. Устройство не требует установки контролируемого блока 3 перед проверкой в исходное состояние. Контролируемый блок 3 совместно с регистром сдвига 2 образует (Л С Puz.i

Раг.г

Редактор Н.Бобкова

Составитель А„Сиротская Техред А.Кравчук

Заказ 5695/44

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг.З

.Корректор,И.Муска

| Устройство для контроля цифровых блоков | 1985 |

|

SU1278854A1 |

Авторы

Даты

1987-11-23—Публикация

1986-05-12—Подача