1

Изобретение относится к вычислительной технике, а именно к контролю долговременных запоминающих устройств.

Известно устройство для контроля, содержащее сумматор, блок задания циклов суммирования, блок установки контрольных чисел и блок управления. Проверяемый блок постоянной памяти кроме контролируемых чисел дополнительно хранит контрольные константы, с помощью которых осуществляется контроль 1.

Недостатком известного устройства является необходимость хранения большого количества контрольных чисел, что уменьшает полезный объем памяти.

Наиболее близким к предлагаемому по технической сущности является устройство для контроля блоков постоянной памяти, содержащее сумматор, формирователь контрольных разрядов по модулю, коммутатор, регистр сравнения, узел установки контрольных чисел, блок управления и блок задания циклов суммирования. Устройство осуществляет контроль блока долговременной памяти по методу контрольного суммирования 2.

Недостатком известного устройства является излишняя сложность устройства, в частности сумматора.

Цель изобретения - упрощение устройства контроля.

S Поставленная цель достигается тем, что в устройстве для контроля бяоков долговременной памяти, содержащем блок задания циклов суммирования, выход которого подключен к одному управляющему входу ком мутатора, а вход - к первому выходу блока управления, выходы коммутатора подклю чены к одним входам блока сравнения, другие входы которого подключены к вы- ходам блока установки контрольных чисел, управляющий вход блока установки контрольных чисел подключен к второму выходу блока управления, управляющие вход -и выход блока сравнения подключены соответственно к третьему выходу и к входу блока управления, второй управляющий вход коммутатора подключен к четвертому выходу блока управления, сумматор и формирователь сигналов контрольных разрядов, выходы сумматора подключены к входам коммутатора, управляющий вход сумматора под ключей к пятому выходу блока управления.

а входы сумматора подключены к выходам формирователя сигналов контрольных разрядов, входы которого являются входами устройства, управляющий вход формирователя сигналов контрольных разрядов подключен к шестому выходу блока управления.

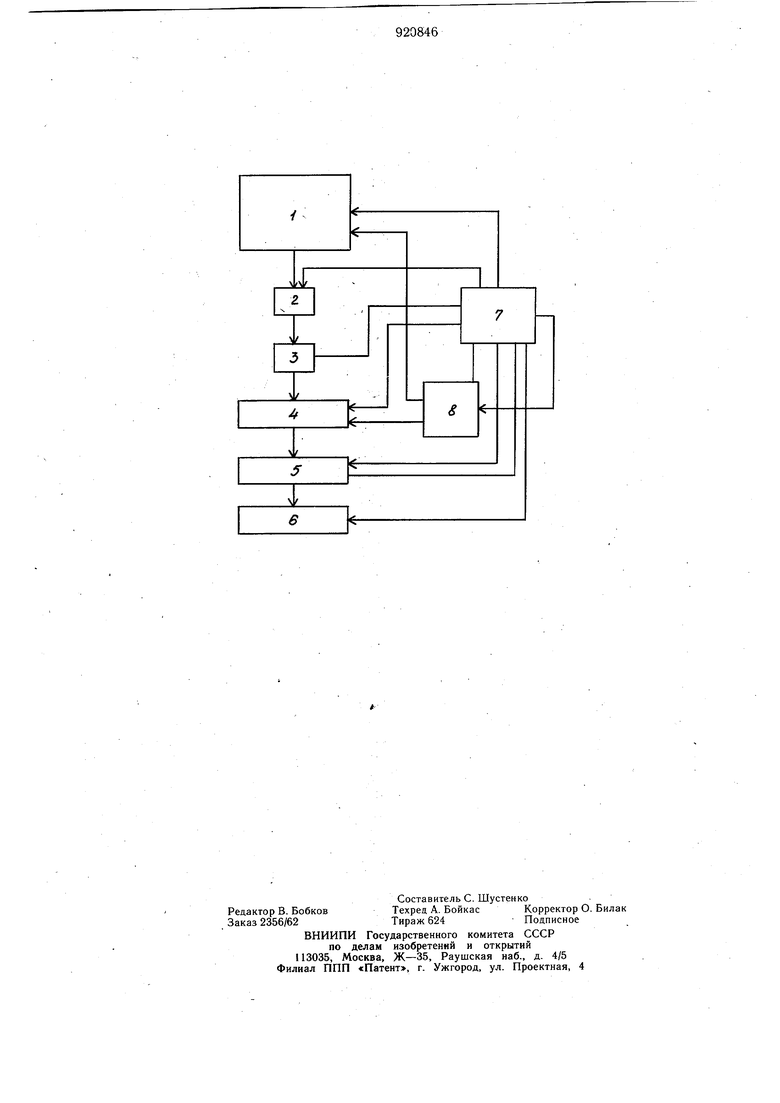

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит подключенный к вы ходам блока Г долговременной памяти формирователь сигналов контрольных разрядов 2, сумматор 3, коммутатор 4, блок 5 сравнения, блок 6 установки контрольных чисе;, блок 7 управления и блок 8-задания циклов суммирования.

Устройство работает следующим образом.

При подаче на вход блока 1 долговременной памяти кода адреса импульса запроса из блока 7 управления и сигнала из блока 8 задания циклов суммирования из блока 1 долговременной памяти считываются числа и посылаются в формирователь сигналов контрольных разрядов 2, в котором производится определение вычета каждого считанного числа, далее производится сложение вычетов в сумматоре 3. После того, как все числа, подлежащие суммированию в очередном цикле, отработаны; в сумматоре 3 хранится сумма вычетов всех считанных в этом цикле чисел. По сигналам управления, поступающим из блока 7 управления и блока 8 задания циклов суммирования, через коммутатор 4 производится запись контрольных разрядов вычета в соответствующие разряды блока 5 сравнения. Сумматор 3 после этого обнуляется. Начинается следующий цикл суммирования. После заполнения всех разрядов блока 5 сравнения в нем производится сравнение полученного кода с контрольным числом, поступающим из блока 6 установки контрольных чисел п.о кЬманде из блока 7 управления.

Результат операции сравнения направляется в блок 7 управления.

Применение предлагаемого устройства позволяет реализовать поставленную задачу контроля, используя сумматор значительно меньщей разрядности, чем в известном. А именно, если используется формирование

контрольных разрядов по модулю,А, то количество контрольных разрядов К будет равно К Iog2 (А + 1), при А 7, К 3. В известном устройстве К М, где М - разрядность слов в блоке памяти. Обычно , 32 и т.д. При этом известно, что поскольку контроль.по вычетам используется для контроля арифметических операций, то возникающие ощибки обнаруживают вычетом и точность контроля не ухудщается.

10

Формула изобретения

Устройство для контроля блоков долговременной памяти, содержащее блок задания циклов суммирования, выход которого подключен к одному управляющему входу коммутатора, а вход - к первому выходу блока управления, выходы коммутатора подключены к одним входам блока сравнения, другие входы которого подключены к

выходам блока установки контрольных чисел, управляющий вход блока установки контрольных чисел подключен к второму выходу блока управления, управляющие входы и выход блока сравнения подключены соответственно к третьему выходу и к входу блока управления, второй управляющий вход коммутатора подключен к четвертому выходу блока управления, сумматор и формирователь сигналов контрольных разрядов, отличающееся тем, что, с целью упрощения устройства, выходы сумматора подключены к входам коммутатора, управляющий вход сумматора подключен к пятому выходу блока управления, а входы сумматора подключены к выходам формирователя сигналов контрольных разрядов, входы которого являются

входами устройства, управляющий вход формирователя сигналов контрольных разрядов подключен к щестому выходу блока управления.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 135105, кл. G 11 С 29/00, 1975.

2.Авторское свидетельство СССР по заявке № 2794982/18-24, кл. G И С 29/00,

1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1979 |

|

SU881874A1 |

| Устройство для контроля постоянной памяти | 1979 |

|

SU824316A1 |

| Устройство для контроля блоков постоянной памяти | 1982 |

|

SU1049984A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU907588A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1080218A2 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля блоков постоянной памяти | 1975 |

|

SU612287A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

Авторы

Даты

1982-04-15—Публикация

1980-07-02—Подача