(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля постоянной памяти | 1979 |

|

SU824316A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU834768A1 |

| Ассоциативное запоминающее устройство с самоконтролем | 1980 |

|

SU858105A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1094071A1 |

| Постоянное запоминающее устройство для многоместных симметричных функций | 1979 |

|

SU873277A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1095240A1 |

| Постоянное запоминающее устройство с самоконтролем | 1983 |

|

SU1153360A1 |

| Устройство для обнаружения и исправления ошибок в блоке памяти | 1980 |

|

SU888213A1 |

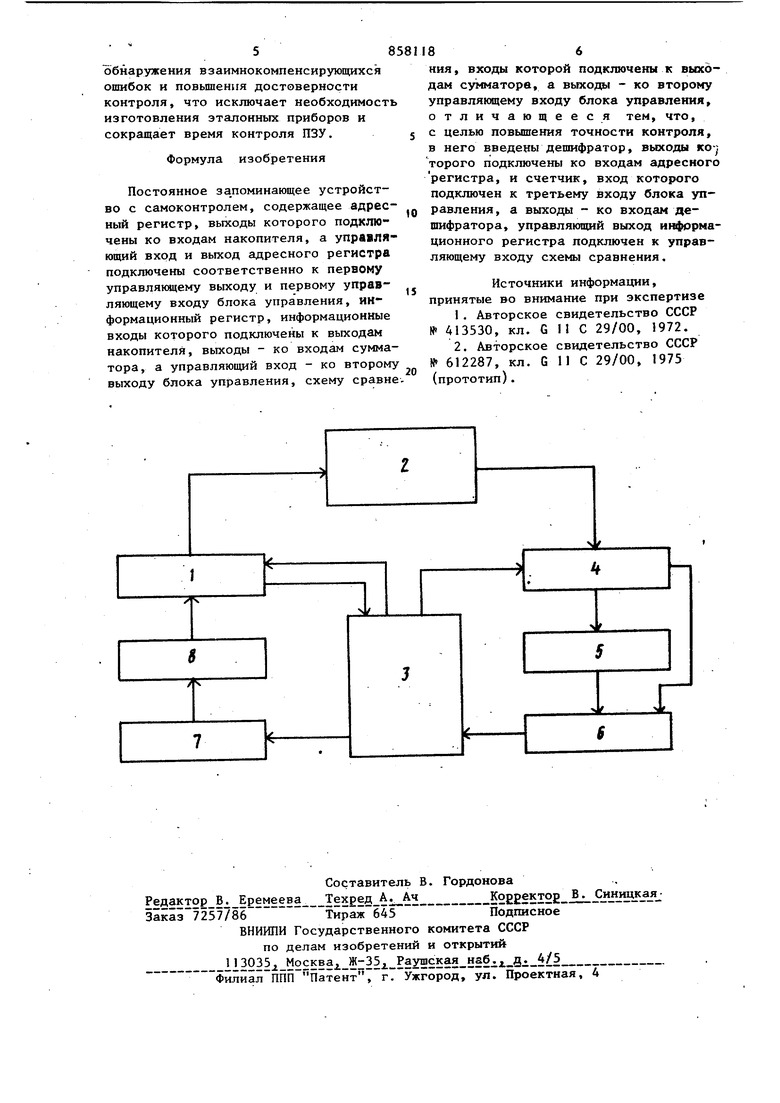

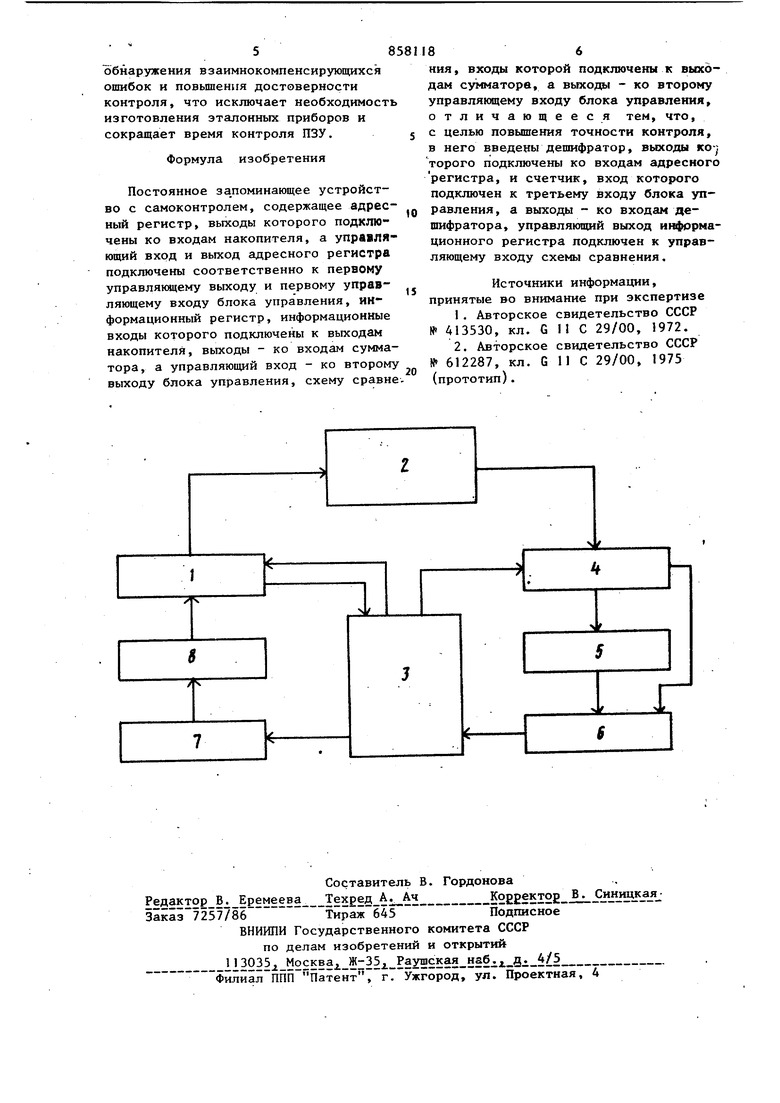

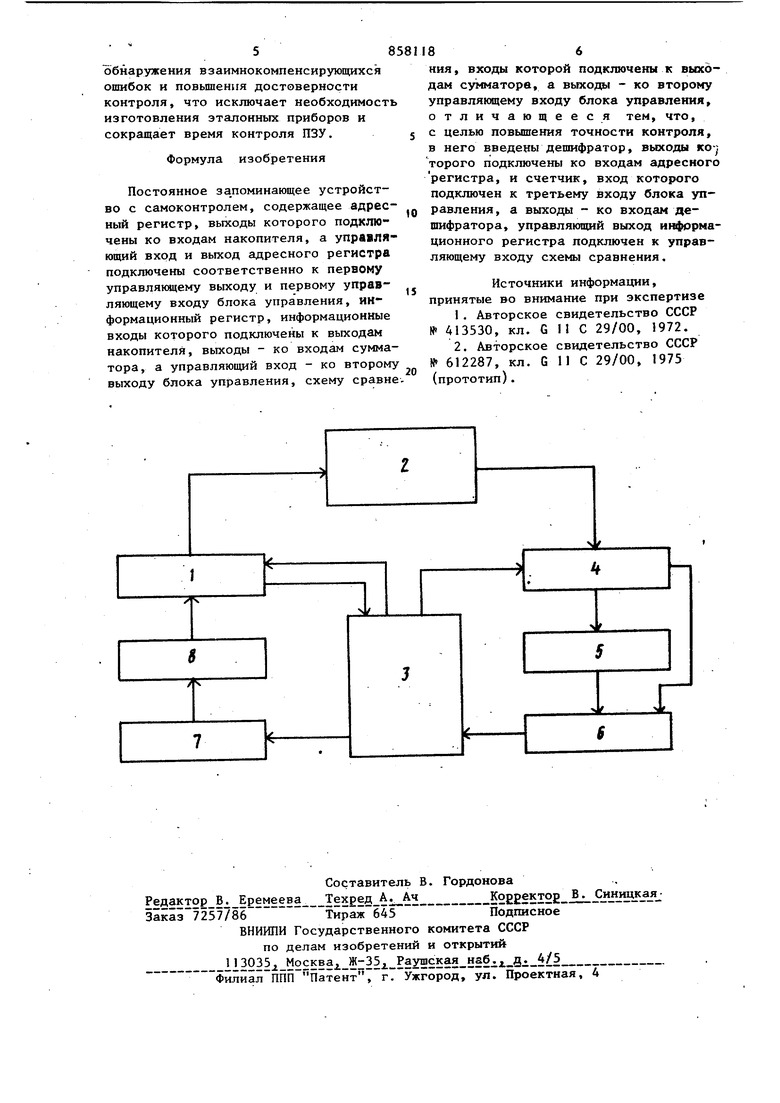

Изобретение относится к области контроля запоминающих устройств . и может быть использовано для контроля постоянных запоминающих устройств (ПЗУ) и блоков постоянной памяти в процессе их производства и эксплуата ции. Известно устройство для контроля запоминающего блока, в котором контроль осуществляется методом последов тельного суммирования чисел по модулю 2 и сравнивании полученной суммы с контрольным числом, содержащее счетчик адресов, выходной регистр, схему сравнения fl J. Недостатком этого устройства явля ется низкая точность контроля и слож ность определения адреса ошибки. Наиболее близким по технической сущности к предлагаемому является ус ройство для контроля блоков постоянной памяти, содержащее регистр адреса, подключенный к блоку управления и выходу устройства, вход которого последовательно через регистр числа, сумматор, подключен к блоку управления, вход которого соединен с регистром числа. Это устройство контролирует блоки постоянной памяти по суммам, образуемым путем циклического суммирования всех содержащихся в блоке памяти чисел с переносом единицы переполнения из старшего разряда сумматора в младший 2 J. Недостатком зтого устройства является низкая точность контроля за счет пропусков взаимнокомпенсирующихся ошибок и отсутствие динанкческих обращений при проверках в реальном масштабе времени. Цель изобретения - повышение точности контроля постоянного запоминающего устройства. Поставленная цель достигается тем, что в постоянное запо1в1нающее устройство с самоконтролем, содержащее адресный регистр, выходы которого подключены ко входам накопителя, а 3 управляющие вход и вьрсод адресного регистра соответственно к первому уп равляющему выходу и первому управляю щему входу блока управления, информа ционный регистр, информационные вход которого подключены к выходам накопи теля, выходы - ко входам сумматора, а управляющий выход - ко второму вхо ду блока управления, схему сравнения входы которой подключены к выходам сумматора, а выходы - к второму управляющему входу блока управления, введены дешифратор, выходы которого подключены ко входам адресного регистра, и счетчик, вход которого под ключен к третьему входу блока управления, а выходы - ко входам дешифратора, управляющий выход информационного регистра подключен к управляющему входу схемы сравнения. На чертеже изображена структурная схема устройства. Постоянное запоминающее устройство с самоконтролем содержит адресный регистр 1, накопитель 2, блок управления 3, информационный регистр 4, сумматор 5, схему сравнения 6, счет чик 7, и дешифратор 8. Устройство в автоматическом режиме работает следующим образом. При запуске устройства блок управ ления 3 вьщает управляющий сигнал на адресный регистр, который проводит последовательный перебор всех адресов проверяемого накопителя 2. Считанная информация через информационный регистр 4 поступает в сумматор 5 который формирует сумму чисел накопителя 3 и вьщает ее на схему .сравне ния 6. По окончании первого цикла суммирования на схему сравнения 6 поступает информация с сумматора 5 и информационного регистра 4, и происходит сравнение полученной суммы и контрольной константы. При положительных результатах сравнения блоком управления 3 выдается сигнал на при бавление I в счетчик 7. Дешифратор по состоянию выходных разрядов счетчика 7 через установочные входы адресного регистра 1 фиксирует разряд адреса в 1. Во втором цикле суммиро вания происходит перебор адресов накопителя 2 при фиксированном значении первого разряда адреса. Полученная при считывании сумма сравнивается с новой константой, и в счетчик 7 прибавляется 1. В резул 8Л тате этого дешифратор 8 во втором разряде адресного регистра 1 фиксирует 1. После получения и сравнения аналогичным образом п+1 суммы формируются суммы при фиксации в разряды регистра адреса 1 логического О, а при окончании одного цикла суммирования происходит его повторение. Адрес ошибки определяется исходя из соответствия контрольных сумм адресам суммирования, путем анализа результатов сравнения сумм цикла. Так, при однократной ошибке, номера несовпавших сумм соответствуют адресу ошибки. Динамический режим обращения к накопителю образуется за счет фиксации разрядов адреса, в результате чего меняется последовательность выбора адреса и достигается наиболее тяжелый режим для накопителя. Предлагаемое устройство позволяет многократно считывать числа из постоянного запоминающего устройс1 ва и формировать контрольные суммы при изменении массивов суммирования, что обеспечивается тем, что проверяемое ПЗУ, кроме контролируемых чисел, содержит контролируемые константы, которые являются циклическими суммами, либо суммами по модулю 2 определенных массивов чисел ПЗУ. Количество контрольных констант зависит от информационного объема ПЗУ и возможного количества и своеобраз }я ошибок, и может достигать значения 2п+, где п - количество необходимых разрядов адреса для контроля ПЗУ. Контрольные константы образуются следующим образом. Первая константа является общей суммой всех чисел ПЗУ, вторая - суммой чисел, первый разряд адреса которых равен I, третья - суммой чисел, второй разряд адреса которых равен 1,...п+1 константа - суммой чисел, разряд адреса которых равен 1. Аналогичным образом формируются константы при установлении каждого из разрядов адреса в 0. Эффективность контроля при таком суммировании достигается тем, что каждое число ПЗУ входит в несколько сумм и при этом суммируется с равными слагаемыми, что обеспечивает обнарзжение большинства взаимокомпенсирующихся ошибок. Предлагаемое устройство позволяет повысить точность контроля за счет 5 обнаружения взаимнокомпенсирующихся ошибок и повышения достоверности контроля, что исключает необходимост изготовления эталонных приборов и сокращает время контроля ПЗУ. Формула изобретения Постоянное за поминающее устройство с самоконтролем, содержащее адресный регистр, выходы которого подключены ко входам накопителя, а упрашляющий вход и выход адресного регистра подключены соответственно к первому управляющему выходу и первому управляющему входу блока управления, информационный регистр, информационные входы которого подключены к выходам накопителя, выходы - ко входам сумматора, а управляющий вход - ко второму выходу блока управления, схему сравне 86 ния, входы которой подключены к выходам сумматора, а выхода - ко второму управляющему входу блока управления, отличающееся тем, что, с целью повьштения точности контроля, в него введены дешифратор, выходы ко-, торого подключены ко входам адресного регистра, и счетчик, вход которого подключен к третьему входу блока управления, а выходы - ко входам дешифратора, управляющий выход информационного регистра подключен к управляющему входу схемы сравнения. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 413530, кл. G 11 С 29/00, 1972. 2.Авторское свидетельство СССР fP 612287, кл. G 11 С 29/00, 1975 (прототип).

Авторы

Даты

1981-08-23—Публикация

1979-12-25—Подача