(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСТОЯННОЙ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1979 |

|

SU858115A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для контроля блокапОСТОяННОй пАМяТи | 1979 |

|

SU809396A1 |

| Устройство кодирования информации для памяти с записью неполными словами | 1983 |

|

SU1267485A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1080218A2 |

| Устройство для контроля памяти | 1977 |

|

SU714503A1 |

| Запоминающее устройство с исправлением ошибок | 1989 |

|

SU1667156A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Постоянное запоминающее устройство с самоконтролем | 1979 |

|

SU858118A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

f

; Изобретение относится к запоми- нанэдим устройствам.

Известно устройство для контроля постоянной памяти, содержащее регистр адреса, дешифратор адреса, числовой регистр, сумматор, блок управления и блок задания циклов суммирования. Это устройство осуществляет контроль за несколько циклов суммирования, в каждом из которых с определенной константой сдвига образуются суммы по модулю два или арифметические суммы с кольцевым переносом .единицы в мпадший разряд сумматора и осуществляется сравнение образованных сумм с

контрольными ЧИСЛс1МИ (YJ .

Недостатком этого устройства является невозможность определения адреса ошибки.

Наиболее близким техническим решением к данному изобретению является устройство для- контроля постоянного запоминающего устройства, содержащее счётчики адресов и разрядов,разрядный коммутатор, группу вентилей, триггерный регистр, блок установки регистра и блок управления. Это устройство регшизует проверки на четность Хэмминга. Для реализации проверок, считываемый из накопителя код

преобразуется из параллельной в последовательную с помощью счетчика разрядов и разрядного коммутатора. Устройство позволяет определить адрес и разряд одиночной ошибки и обнару живать нечетные многократные ошибки

С23Недостатком этого устройства является невысокая точность и большая ,

o длительность контроля при контроле постоянных запоминающих устройств на интегральных запоминающих микросхемах словарного типа.

Цель изобретения - повышение до5 стоверностй контроля и повьипение быстродействия устройства.

Поставленная цель достигается там, что в устройство для контроля постоянной памяти, содержащее счетчик ад0ресов, счетчик разрядов, блок установки контрольных чисел, схему сравнения, элементы И, разрядный коммутатор и блок управления, причем одни входы элементов И подключены к одно5му из выходов счетчика адресов, другие - к выходу разрядного коммутатора, а выходы - к первому входу схем .сравнения, второй вход которой сое динен с выходом блока установки конт0рольных чисел, первый вход разрядного коммутатора подключен к выходу счетчика разрядов, управляющие входеа и выходы счетчиков адресов и разрядов, схемы сравнения, блока установки контрольных чисел подключены к соответствующим выходам и входам блока управления, введены сумматоры, одни иэ входов которых подключены ко входам устройства, другой вход соединен с одним из Ьыходов блока управления, а выходы подключены соответственно ко второму входу разрядного коммутатора и третьему входу схемы сравнения.

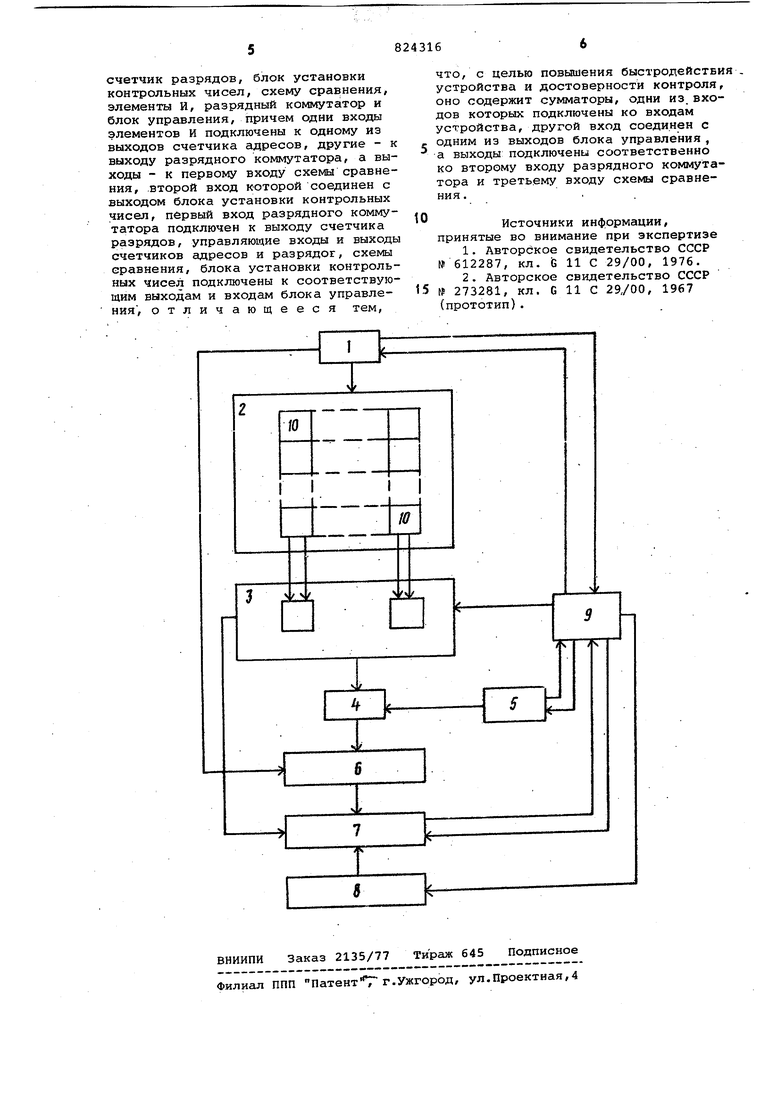

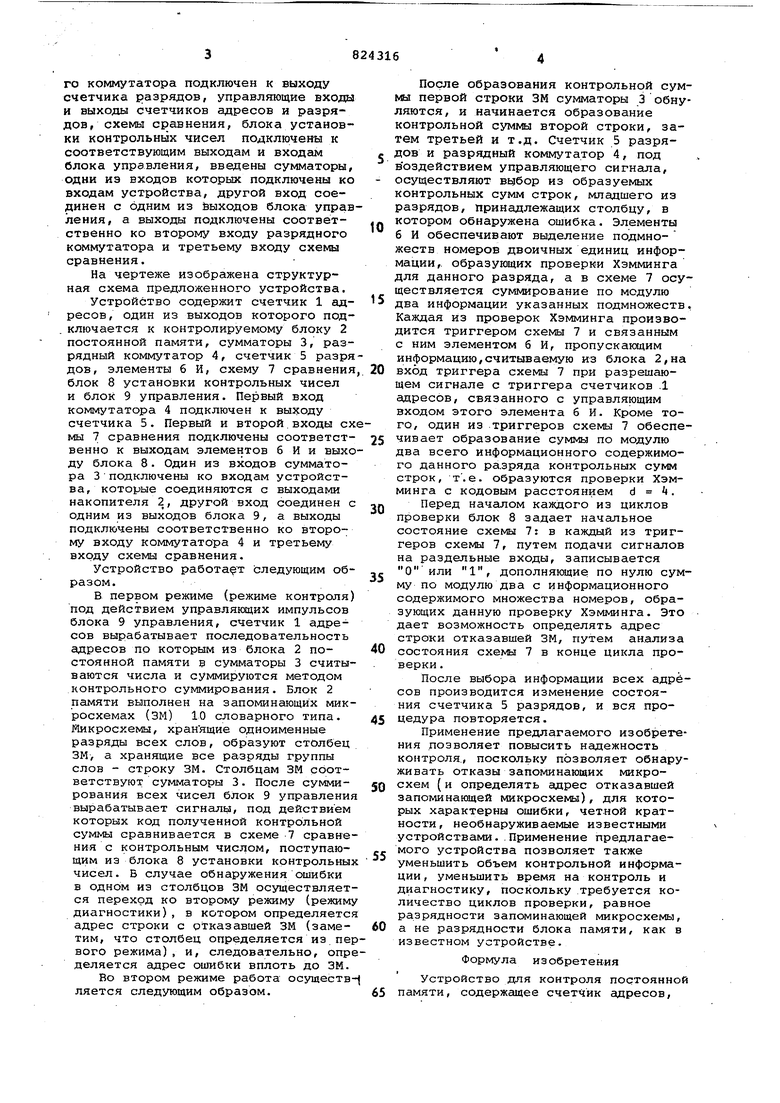

На чертеже изображена структурная схема предложенного устройства.

Устройство содержит счетчик 1 адресов , один из выходов которого подключается к контролируемому блоку 2 постоянной памяти, сумматоры 3, разрядный коммутатор 4, счетчик 5 разрядов, элементы б И, схему 7 сравнения блок 8 установки контрольных чисел и блок 9 управления. Первый вход коммутатора 4 подключен к выходу счетчика 5. Первый и второй.входы схмы 7 сравнения подключены соответственно к выходам элементов б И и выходу блока 8. Один из входов сумматора 3 подключены ко входам устройства, которые соединяются с выходами накопителя 2, другой вход соединен с одним из выходов блока 9, а выходы подключены соответственно ко второму входу коммутатора 4 и третьему входу схемы сравнения.

Устройство работает следующим образом.

В первом режиме (режиме контроля) под действием управляющих импульсов блока 9 управления, счетчик 1 адресов вырабатывает последовательность адресов по которым из блока 2 постоянной памяти в сумматоры 3 считываются числа и суммируются методом контрольного суммирования. Блок 2 памяти выполнен на запоминающих микросхемах (ЗМ) 10 словарного типа. Микросхемы, хранящие одноименные разряды всех слов, образуют столбец ЗМ, а хранящие все разряды группы слов - строку ЗМ. Столбцам ЗМ соответствуют сумматоры 3. После суммирования всех чисел бЛок 9 управления вырабатывает сигналы, под действием которых код полученной контрольной суммы сравнивается в схеме 7 сравнения с контрольным числом, поступающим из блока 8 установки контрольных чисел. Б случае обнаружения ошибки в одном из столбцов ЗМ осуществляется переход ко второму режиму (режиму диагностики), в котором определяется адрес строки с отказавшей ЗМ (заметим, что столбец определяется из первого режима), и, следовательно, определяется адрес ошибки вплоть до ЗМ.

Во втором режиме работа осуществляется следующим образом.

После образования контрольной сумivb первой строки ЗМ сумматоры 3 обнуляются, и начинается образование контрольной суммы второй строки, затем третьей и т.д. Счетчик 5 разрядов и разрядный коммутатор 4, под воздействием управляющего сигнгша, осуществляют вьзбор из образуемых контрольных сумм строк, младшего из разрядов, принадлежащих столбцу, в котором обнаружена ошибка. Элементы 6 И обеспечивают выделение подмножеств номеров двоичных единиц информации,, образующих проверки Хэмминга для данного разряда, а в схеме 7 осуществляется суммирование по модулю два информации указанных подмножеств. Каждая из проверок Хэмминга производится триггером схемы 7 и связанным с ним элементом б И, пропускающим информацию,считываемую из блока 2,на вход триггера схемы 7 при разрешающем сигнале с триггера счетчиков .1 адресов, связанного с управляющим входом этого элемента б И. Кроме того, один из триггеров cxeNsa 7 обеспечивает образование суммы по модулю два всего информационного содержимого данного разряда контрольных сумм строк, т .е. образуются проверки Хэмминга с кодовым расстоянием d i. Перед началом каждого из циклов проверки блок 8 задает начальное состояние схемы 7: в каждый из триггеров схемы 7, путем подачи сигналов на раздельные входы, записывается О или 1, дополняющие по нулю сумму по модулю два с информационного содержимого множества номеров, образующих данную проверку Хэмминга. Это дает возможность определять адрес строки отказавшей ЗМ, путем анализа состояния схемы 7 в конце цикла проверки.

После выбора информации всех адресов производится изменение состояния счетчика 5 разрядов, и вся процедура повторяется.

Применение предлагаемого изобретения позволяет повысить надежность контроля., поскольку позволяет обнаруживать отказы запоминающих микросхем (и определять адрес отказавшей запоминающей микросхемы), для которых характерны ошибки, четной кратности, необнаруживаемые известными устройствами..Применение предлагаемого устройства позволяет также уменьшить объем контрольной информации , уменьшить время на контроль н диагностику, поскольку требуется количество циклов проверки, равное разрядности запоминающей микросхемы, а не разрядности блока памяти, как в известном устройстве.

Формула изобретения

Устройство для контроля постоянной 5 памяти, содержащее счетчик адресов.

Авторы

Даты

1981-04-23—Публикация

1979-06-07—Подача