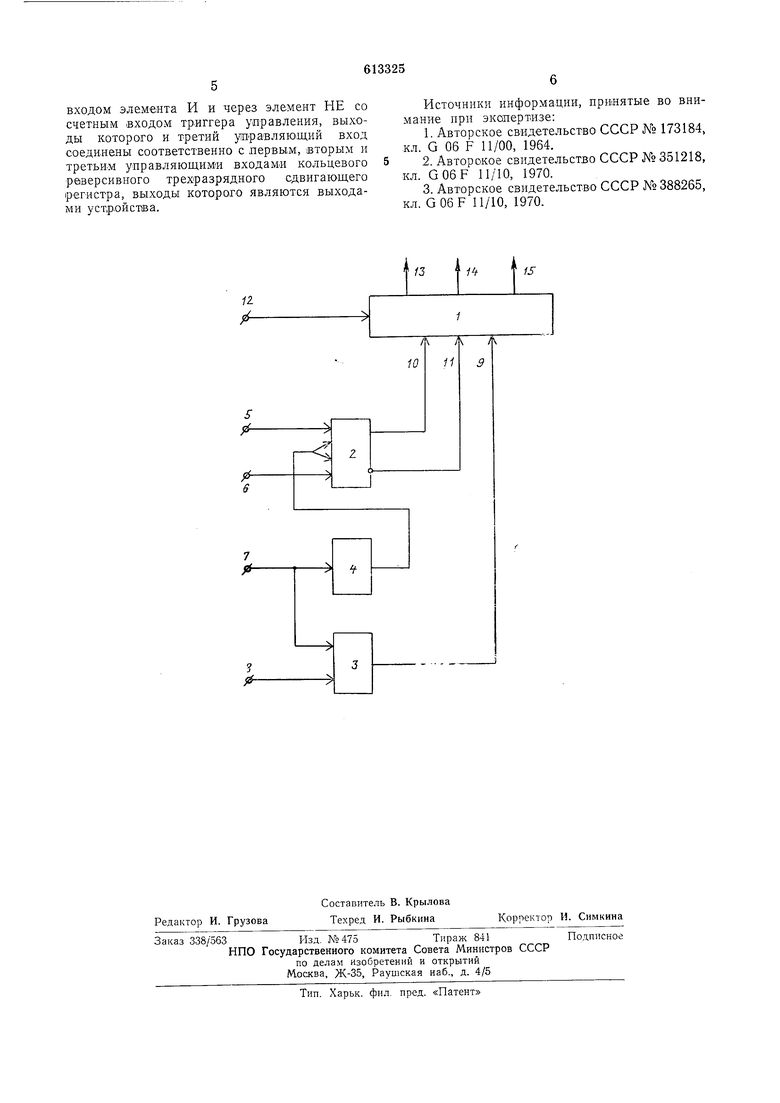

элемента НЕ 4, вход которого соединен с входом 7 -синхронизации. Этот вход 7 подключен к входу элемента И 3, второй ;вход которого соединен с инфармационным входом 8. Выход элемента И 3 соединен с тактирующим входам 9 регистра /. Единичный выход триггера 2 подключен к входу 10, а нулевой - ;к входу // регистра /. Третий управляющий вход 12 устройства соединен с входом регистра 1. Выходы 13, 14 и 15 регистра } представляют собой единичные выходы разрядов релистра / и являются выходными шинами устройства. Работает устройство следующим образом. Перед приходом первого (старщего или младшего) разряда двоичного слова сигнал исходной установки :по входу 12 устанавливает разряды регистра 1 в состояние, при котором :На выходах 13, 14 и 15 появляется код 100. Если попадающие на вход устройСлва слова содержат нечетное число разрядов или же они поступают младшими разрядами вперед, тогда триггер 2 управления сигналов ло входу 5 устанавливается в едилицу. Если же принимаемые слова содержат четное число разрядов, поступающих старшими разрядами вперед, тогда триггер 2 по входу 6 занимает нулево.е исходное состояние. Единичное состояние триггера 2 соответствует разрешению сдвига вправо содержимого регистра 1, а нулевое - влево. После того, как на инфорамационном входе 8 установится значение принимаемого разряда, на вход 7 под-ается синхроимпульс, который в случае единичного значения разряда проходит через элемент И 5 и поступает на тактирующий вход 9 регистра /. В зависимости от текущего состояния приггера 2 управления этот импульс вызывает сдвиг на один разряд влево или влраво единицы, записанной в регистре /. После окончания действия синхроимпульса триггер 2 перебрасывается ло счетному входу, подготавливая цепь сдвига регистра / к приходу следующего разряда принимаемого слова. Например, пусть на вход устройства подается код ОНО, начиная со старщего (левого) разряда. Вследствие того, что слово содержит четное число разрядов, пост ающих начиная со старшего, триггер 2 должен быть установлен в нулевое исходное состояние. Первый пришедший синхроимпульс не вызывает сдвига в регистре / из-за нулевого значения старщего разряда слова. По окончании действия синхроимпульса триггер 2 переключается в «I и второй прищедший синхроимпульс вызывает сдвиг на один разряд влраво содержи.мого регистра /, т. е. на выходах 13, 14 и 15 формируется «од 010. После следующего (третьего) синхроимпульса происх;одит одвиг На одни ра:3ряд влево в регистре 1, так как после второго синхроимпульса триггер 2 переключается в нулевое состояние. Чет1вертый разряд слова не приводит к изменениЯМ в состоянии регистра / и на выходе устройства сохраняется код 100, соответствующий нулевому значению остатка по модулю три принятого числа «6. В случае, если код 10101 поступает в устройство младшими (т. е. начиная с леВ|0го) разрядами вперед, триггер 2 быть в единичном исходном состоянии и первый нринятый разряд формирует на выходе устройства код 010. Второй разряд не изменяет этот .код, третий приводит к сдвигу еще на один разряд вправо в регистре / и образованию на выходе кода 001, четвертый сохраняет это состояние, а с приходом пятого разряда в регистре / происходит еще один сдвиг вправо и, вследствие кольцевого соединения разрядов регистра 1, на выходных щинах устройства образуется код 100, соответствующий тому, что остаток числа «21 по модулю три равен нулю. Если младшими разрядами вперед поступает код 1101, то, в отличие от предыдущего примера, четвертый разряд производит сдвиг влево в регистре / и на выходных шинах устройства формируется код 010, т. е. признак того, что остаток числа «13 по модулю три равен единице. Остатку «2 соответствует код 001 на выходах 13, 14 и 15. Таким образом, в предлагаемом устройстве минимальный период поступления разрядов принимаемого слова определяется суммой времени прохюждения сигнала через элемент И 3, времени переключения триггера в регистре 1 и времени переключения по счетному входу триггера 2 злравления. Задержка формирования значения остатка на выходе устройства по отношению к моменту прихода синхроимпульса, сопровождающего последний разряд принимаемого слова, определяется временем задержки элемента И 5 и временем переключения разряда в регистре /. Кроме того, остаток по модулю три формируется в виде потенпиального позиционного кода. Формула изобретения Устройство для формирования остатка по одулю три, содержащее элементы И и НЕ, о тличающееся тем, что, с целью расщирения частотного диапазона, в устройство введены кольцевой реверсивный трехразрядный сдвигающий регистр и триггер управления, входы установки в «О и в «1 которого являются первым и вторым управляющими ходами устройства, информационный вход Ттройства соединен с первым входом элемента И, выход которого соединен с тактиующ-им входом кольцевого реверсиеного рехразрядного сдвигающего регистра, вход инх/ронизации устройства соединен с вторым

входом элемента И и через элемент НЕ со счетным .входом триггера управления, выходы которого и третий управляющий вход соединены соответственно с лервым, вторым и третьИМ управляющими входами кольцевого реверсивного трехразрядного сдвигающего регистра, выходы которого являются выходами устройства.

Источники информации, принятые во внимание ири экспертизе:

1.Авторское свидетельство СССР № 173184, кл. G 06 F 11/00, 1964.

2.Авторское свидетельство СССР № 351218, кл. G06F 11/10, 1970.

3.Авторское свидетельство СССР № 388265, кл. GQ6F 11/10, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сдвига информации | 1985 |

|

SU1291962A1 |

| Устройство для сдвига информации | 1973 |

|

SU458824A1 |

| Устройство для формирования контрольного кода по четности | 1980 |

|

SU934477A1 |

| СПОСОБ ПОМОЩИ ВОДИТЕЛЯМ ПРИ ПЕРЕСТРОЕНИЯХ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2016 |

|

RU2646782C2 |

| Устройство для сдвига информации | 1983 |

|

SU1188783A2 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1982 |

|

SU1056207A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Запоминающее устройство на сдвиго-ВыХ РЕгиСТРАХ | 1979 |

|

SU841052A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

9

1S

Авторы

Даты

1978-06-30—Публикация

1976-09-13—Подача