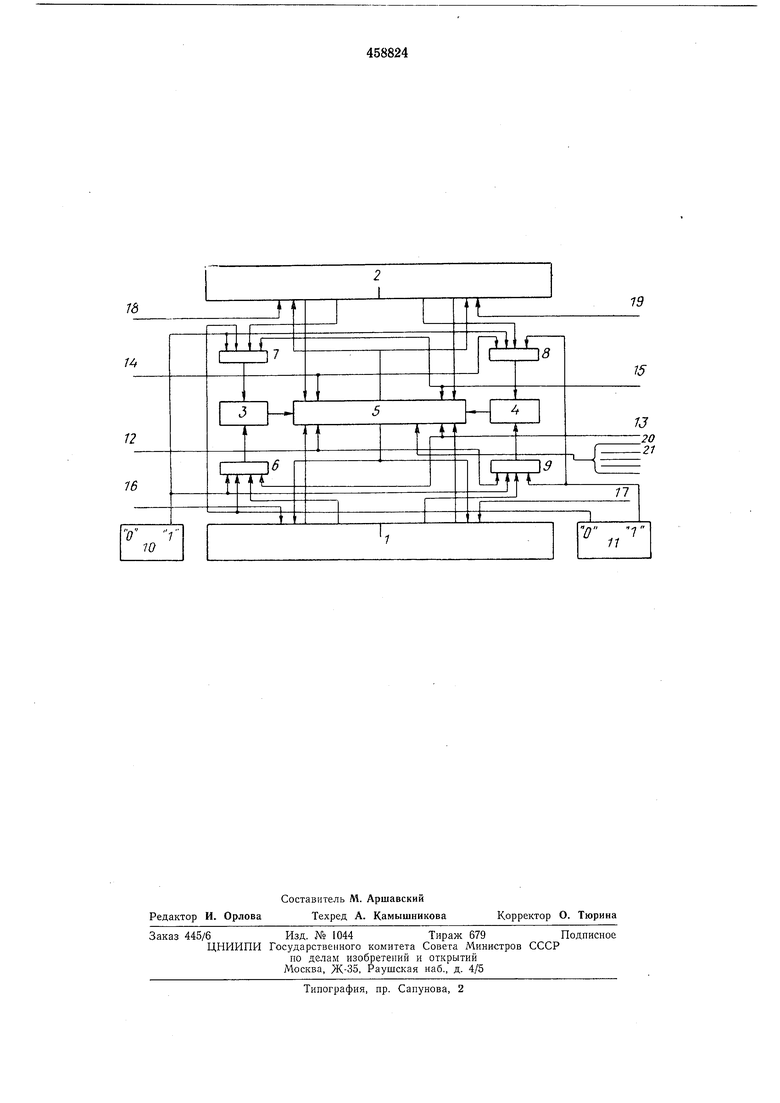

3 сдвига 5 (для Старшей половины двойного слова). Входной регистр 1 через схему «И 9 и далее через схему «ИЛИ 4 соединен с блоком сдвига 5 (для младшей половины двойного5 слова). Выходной регистр 2 через схему «И 7 и далее через схему «ИЛИ 3 соединен с блоком Сдвига 5 (старШая половина двойНОго слова).10 Выходной регистр 2 через схему «И 8 и далее через схему «ИЛИ 4 соединен блоком сдвига 5 (мл адшая половина двойного сЛОеа). Выход «1 триггера длины сдвига соединен15 с вх:одами схем «И 6-9, выход «О триггер.а направления сдвига 11 соединен с входами схем «И 6, 7, а выход «1 триггера направления Сдвига 11 соединен с входами схем «И 8, 9.20 Входы регистров 1, 2 и блока сдвига 5 соединены с выходными шинами 12-19 местного устройства управления и с выходными шинами 20, 21 устройства выработки числа сдвигов (не показаны).25 Работает предлагаемое устрорютво следующим образом. Слово двойной длины, подлежащее обр.аботке, хранится во входном регистре 1 (Старшая ПОловина - в старших разрядах, млад-30 шая половина - в младших разрядах). При сдвиге Слова двойной длины триггер длины сдвига находится в состоянии «1, что Соответствует работе со словами двойной длины, а триггер напр:авления сдвига находится вз5 состоянии, которое соответствует направлению сдвига («1 -сдвиг влево, «О - сдвиг вираво). В предлагаемом устройстве блок сдвига выполнен комбинационным и может за один40 такт осущбствлять сразу необходимое количество сдвигов л-разрядного числа, а также последовательно осуществлять сдвиг на 1, 2, 4, 8, 16 и т. д. разрядов влево и вправо в зависимости от коистанты сдвиг.а и разряд-45 ности числа. В этом Случае число цепей сдвига задается как т /-УП, а количество разрядов, на которое сдвигает каждая цепь в блоке сдвига, равно «/2т. При сдвиге «-разрядного числа оно засыл.ается в старшие разряды50 входного регистра 1 и через «-разрядный блок сдвига обычным образом сдвигается с последующей засылкой результата в выходной регистр 2. При Сдвиге 2«-р1азрядного числа, состояще-55 го из старщей и младшей иоловин по « разрядов каждая, организация сдвига зависит от направления сдвига. При сдвиге влево сначал.а выполняется сдвиг старшей половины, а затем младшей, при сдвиге вправо сдвига-60 ется младшая половина, -а затем старшая половина 2«-разрядвого числа. При сдвиге влево старшего полуслова освобождаются младшие разряды регистра, куда будет записан результат сдвига. Для запол-65 4 нения этих разрядов через элементы 9, 4 (или 8, 4) подключаются старшие разряды младшей половины слова. Младшая половина 2п-р,азрядного числа сдвигается как обычное п-разрядное число. При этом выдвигаемые разряды теряются, они уже были сдвинуты ранее. При сдвиге вправо освобождающиеся старщие разряды мл:адшей половины заполняются через элементы 6, 3 (ил,и 7, 3) младшими р;азрядами старшей половины. Старшая половина 2 г-разрядного числа сдвигается как обычное «-разрядное число. При осуш:ествле1нии сдвигов последовательно на 16, 8, 4, 2, 1 разрядов результат поочередно записывается g регистр 2 или 1, который затем выполняет р входного регистра. На схеме в качестве примера доказаны только шины 21 и 20, по которым приходят сигналы сдвига на 8 и на 4 разряда. в предложенном устройстве Сдвита используются регистры, которые строятся н.а простейших 5-триггерах, работающих в многотактной логике, т. е. если сдвигаемое число находится в регистре 1, то пОСле сдвига число МОжно записать только в 2. Если же регистр 1 построить на триггерах, работающцх по однотактной логике (триггеры D или L.R-типов), то результат СДвига можно занисать в этот же регистр. Сдвиг 2п-разрядно,го числа осуществляется следующим образом. Пусть , тогда в блоке сдвига 5 имеются цепи СДвига на 1, 2, 4, 8, 16 разрядов влево и влраво. Через элементы 9, 4 или 8, 4 коммутируются иа вход .младших разрядов блока сдвига шестнадцать старших разрядов младшей половины 2«-разрядного числа. Через элементы 6, 3 или 7, 3 коммутируются на вход старших разрядов блока сдвига шестнадцать младших разрядов старшей половины 2п-разрядного числа. Пусть 2/г-разрядное число необходимо сдвинуть на двенадцать разрядов влево. Для этого устанавливаются в «1 триггер длины СДвита и триггер направления сдвига. С помощью управляющего сигнала по шине 12 подается на блок сдвига 5 старшая половина 64-разрядного числа; одновременно этот сигнал через элементы 9 и 4 подает старшие шестнадцать разрядов младшей половины числа во входном регистре 1 в младшие разряды блока сдвига. В это же время по шине 21 приходит сигнал в цепь сдвига на восемь разрядов влево, и на выходе блока сдвига получается чиело, Сдвинутое на восемь разрядов влево, младшие восемь разрядов которого заполнены восемью старшими разрядами младшей половины. Управляющим сигналом по шине 18 результат сдвига засылается в старшую половину выходного регистра 2. Затем устанавливается в «О триггер длины сдвига. Управляющим сигналом по шине 13 передается в блок сдвига младшая половина 64-разрядного числа. Элементы «И 9 и «ИЛИ 3 не работают. Управляющим сигналом по шиле 19 сдвинутое .на восемь разрядов число передается в младшую половину регистра 2. Освобождающиеся младшие разряды заполняются нулями.

Таким образом, в регистре 2 получают сдвинутое на восемь разрядов число.

Сдвиг на следующие четыре разряда осуществляется с той разницей, что регистры 1 и 2 меняются ролями. Устанавливается в «1 триггер длины сдвига. Старшая половина числа в регистре 2 передается в блок сдвига сигналом по шине 14. Одновременно старшие шестнадцать разрядов младшей половины регистра 2 через схемы «И 8 и «ИЛИ 4 подаются на младшие разряды блока сдвига. По щине 20 поступает сигнал в цепь сдвига на четыре разряда влево. Сдвинутое число с выхода блока сдвига передается в старшую поповину регистра 1 по сигналу на шине 16. При этом освободившиеся четыре младших разряда заполняются четырьмя старшими разрядами младшей половины 64-разрядного числа.

Устанавливается в «О триггер длины сдвига. Сигналом по шине 15 число с младшей половины регистра 2 подается на блок сдвига и, сдвинутое на четыре разряда, засылается в регистр 1 сигналом по шине 17. Таким образом, на регистре 1 получают число, сдвинутое на двенадцать разрядов влево.

Аналогично производится сдвиг вправо. При этом триггер направления 11 устанавливается в, «О, и работают схемы «И 6 или 7 и схема «ИЛИ 3.

6 Предмет изобретения

Устройство для сдвига информации, содержащее 2п-разрядный входной регистр, 2/г-разрядный выходной регистр, блок сдвига, первые и вторые входы которого соединены с первыми выходами входного и выходного регистров соответственно, триггер направления

сдвига п триггер длины сдвига, отличающееся тем, что, с целью сокращения объема аппаратуры, оно содержит первую и вторую схемы «ИЛИ, выходы которых подключены к третьему и четвертому входам блока

сдвига соответственно, первую и вторую схемы «И, выходы которых подключены к входам первой схемы «ИЛИ, третью и четвертую схемы «И, выходы которых подключены к входам второй схемы «ИЛИ, а блок сдвига

выполнен л-разрядным, причем выходы младших разрядов старших половин входного и выходного регистров соединены с первыми входами первой и второй схем «И, а выходы старших разрядов младших половин входного

и выходного регистров соединены с первыми входами третьей и четвертой схем «И соответственно, нулевой выход триггера направления сдвига соединен с вторыми входами первой и второй схем «И, а единичный выход - с вторыми входами третьей и четвертой схем «И, третьи входы схем «И соединены с единичным выходом триггера длины сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сдвига | 1979 |

|

SU809387A1 |

| Устройство для сдвига информации | 1978 |

|

SU864340A1 |

| Запоминающее устройство | 1979 |

|

SU842967A1 |

| Вычислительное устройство | 1987 |

|

SU1456949A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОГО ОБЪЕДИНЕНИЯ ДАННЫХ СО СДВИГОМ ВПРАВО | 2002 |

|

RU2273044C2 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО для ПЕРЕРАБОТКИ ЧИСЛОВОЙ И БУКВЕННОЙ ИНФОРМАЦИИ | 1969 |

|

SU255656A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Устройство для возведения в квадрат | 1975 |

|

SU606156A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

Авторы

Даты

1975-01-30—Публикация

1973-04-03—Подача