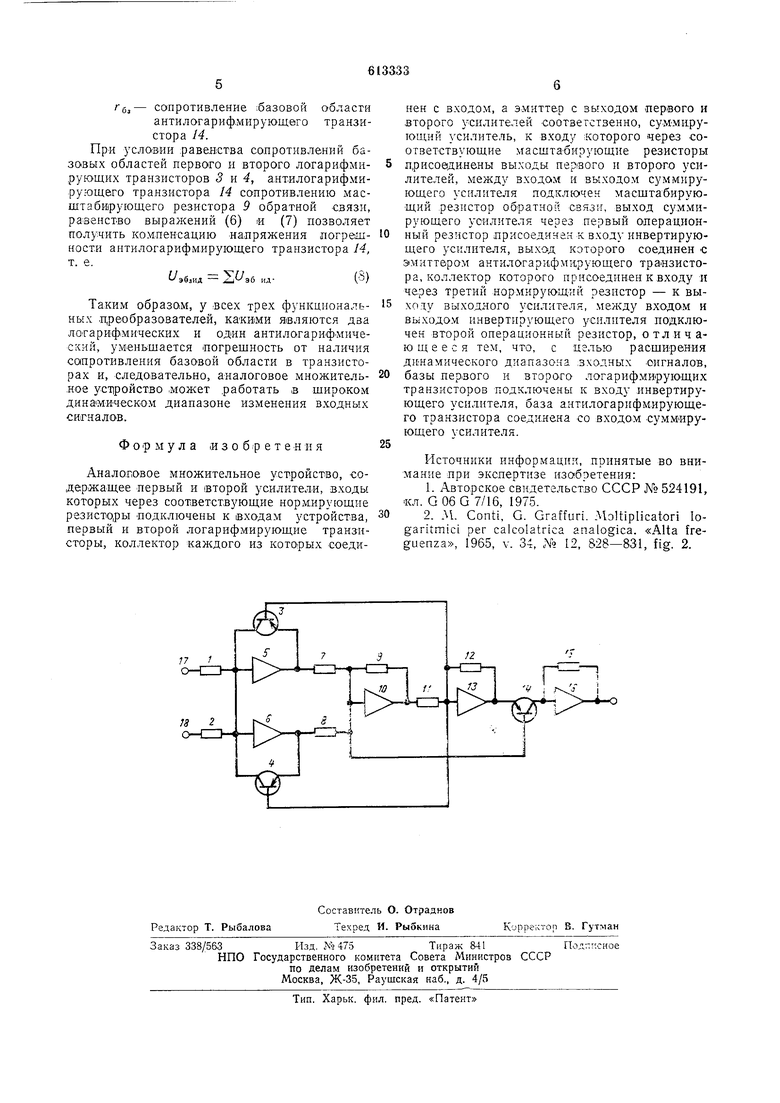

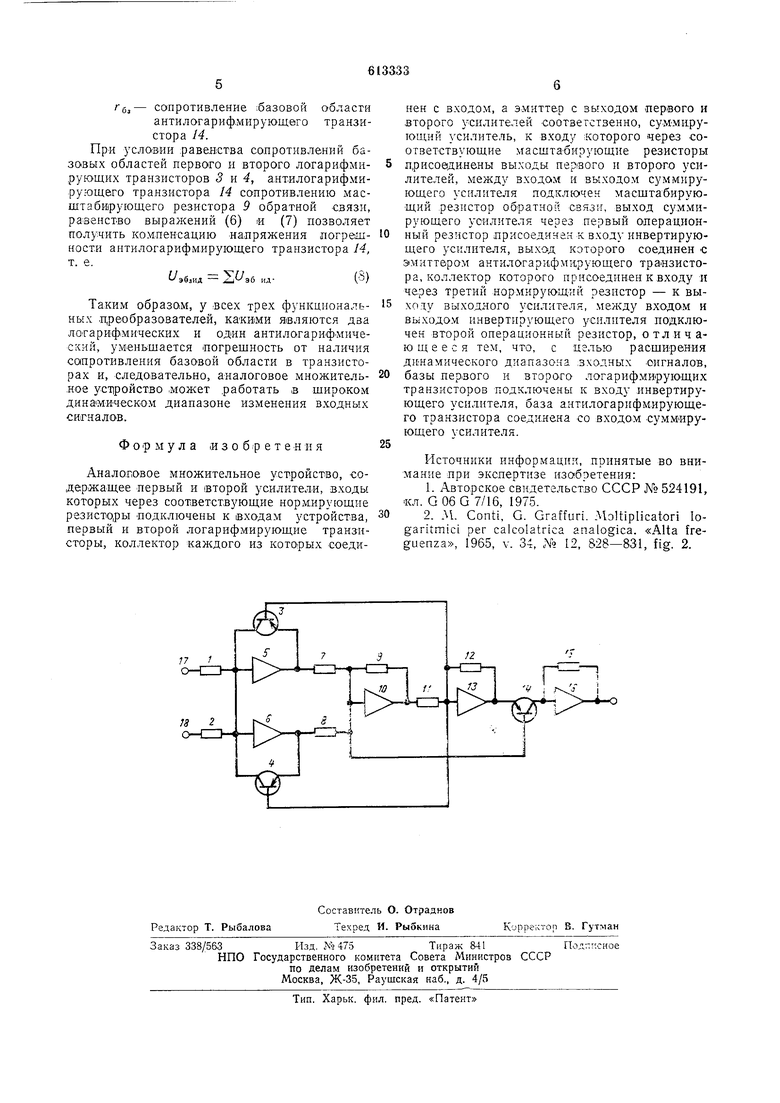

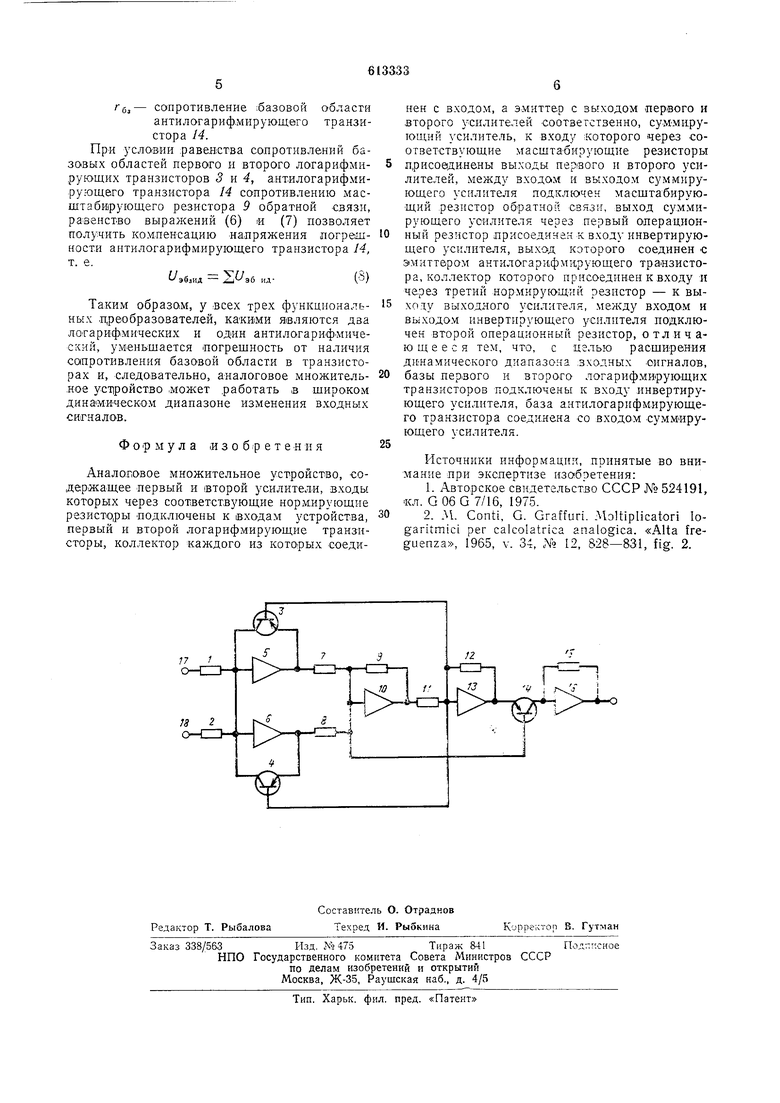

операционные резисторы 11 и 12, инвертирующий усилитель 13, антилагариф.мирующий транзистор 14, третий нормирующий резистор 15, выходной усилитель 16, первый и второй входы устройства /7 и 18. Устройство ра ботает следующим образом. С возрастанием, например, входного сиглала на первом .входе устройства 17 .начинает возрастать коллекторный ток первого , логарифмирующего транзистора 3, а вместе с тем начинает сказываться .падение .напряжения ка сопротивлении базовой области этого транзистора, возникающее от протекания тока базы. Это .на.пряжение ориводит к отк.лонению напряжения перехода э,ммитер- база аер.зогс логарифмирующего транзистора 3 (равное выходно,му напряжению .первого усилителя 5) от логарифмической зависимости и является на пряжением погрешности. Так .как .потенциал базы этого транзистора близок к нулю за счет глубокой обратной связи инвертирующего усилителя 13, то напряжение на .выходе усилителя 5 можно представить в виде; 1 -эбгКД. Г (,1 foi, где i/i - напряжение на выходе первого усилителя 5; зб,;1д - напряжение на переходе эмиттер;-база «идеального первого логарифмирующего транзистора 3; Л б - ТОК базы и сопротивление :базовой области первого логарифмирующего транзистора 3 соответственно. По аналогии с выражением (I) .выходное па/пряжение второго усилителя 6 и 2 - /эб,ид + 4. бе С/2 - напряжение на выходе второго усилителя 6; избгля. - .напряжение на переходе эмиттер-;база «идеального второго лагарифмирук щего транзистора 4; /6г. 6. - ТОК базы и сопротивление ба301ВОЙ области второго логарифмирующего транзистора 4 соответственно. Суммирующий усилитель W аместе с первым и вторым масщтабирующим.и резисторами 7 -и 5 и масштабирующим резистором 9 ооратной связи выполняет функцию сум.матора, где прои сходит слож.ен.ие выходных токов первого и второго усилителей 5 и б и тока базы антилогарифмирующего траааистора 14. Если па;ра,метры первого и вто.рО1Го логарифмирующих транзисторов и 4 и а.нтилогар.ифмирзющего транзистора 14 оди.на-ковы, т. е. величины сопрот:ивл-ен.ий их базовых областей равны между собой, а также при условии равенства ведичил сопротивлений первого и второго маощтабирующих резисторов 7 и 8 и ма.оштабирующего резистора 9 обратной связи, выходное напряжение суммирующего усилителя 10 с точностью до знака после очевидных преобразований разно: 3 эбгаД Г + + Cj f, (3) где f/3 - выходное .напряжение суммирующего усилителя 10; /бз - ток базы антилогарифмирующего транзистора 14; R - сопротивление масщта-бирующего резистора 9 обратной связи. В инвертирующем усилителе 13 |Про.исхоД:ит уменьшение выходного напряжения суммирующего усилителя 10 ровно на величину составляющей погрешности fufS + /б/б б 2 /оИными с.1ава1М.и, выходное напряжение инвертирующего усилителя 13 с точностью до знакас )где U - напряжение на выходе инвертирующего усилителя 13; RI - содротивление первого операдион.ного резистора 11; R - сопротивление второго операционного резистора 12. Если выполнить условие равенства сопротивлений первого и второго операционных .резисторов // и 12 сопротивлению базовых областей перваго, второго логарифмирующих тра.нзисто.ро,в 3, 4 ;и а1нтилогариф.мирующего транз.истора -14, то подставляя в выражение (5) выражения (3) и (4), получают + /б. антилогар.и.фМИрующем транша исто ре 14 с .возрастанием выходного натряжения .инвертирующего усил.ителя 13 такн начинает сказываться падение .напряжения на сопротивлении базовой области, воз-никающее от протекания тока базы. Это на1пряжение лри.водит к отклонению коллекторного антилогари1ф,мирую-щеи) транзи1стор.а /4 от экси|Онен1ЦилльБой aaiBHCHмости и является ;напря;.жением погрешност.и. Так как потенциал базы антилогарифмирую- . щего тра.нзистора 14 близо.к к .нулю за счет глубо.кой обратной связи суммирующего усилитедя 10, то напряжение на выходе инвертирующего усилителя 13 можно представить: 4 - Эбгид + Д/6, где f/36snfl - Нашрял ение .на переходе эмиттер-база «идеально.го аятилогарифм.ирующего транзистора 14; сопротивление :базовой области антилогариф мирующего транзистора 14. При уславйи равеаства сопротивлений базовых областей первого и второго логарифмирующих транзисторов 3 и 4, антилогарифмирующего транзистора 14 сопротивлению масштаби рующего резистора 9 обратной .связи, равенство выражений (6) « (7) позволяет получить компенсацию напряжения norpeinности антилогарифмирующего транзистора 14, т. е Ьэб.ид - ид-(8) Та.ким образам, у всех трех функциональных .дреобразователей, какими являются два логарифмических и один антилогариф-мический, уменьшается погрешность от наличия сопротивления базовой области в транзисторах и, следовательно, аналоговое множитель.кое ус-лройство может работать iS широком динамическом диапазоне изменения входных сигналов. Формула fH 3 о б .р е т е и и я Анало:говое множительное устройство, содержащее первый и второй усилители, входы которых через соответствуюш,ие нормирующие резисторы подключены к входам устройства, первый и второй логарифмирующие транзисторы, коллектор каждого из которых соединен с входом, а эмиттер с выходом пер)вого и второго усилителей соответственно, суММирующий усилитель, к входу ;которого через соответствующие масштабирующие резисторы присоадинены выходы nepieoro и второго усилителей, между входом и выходом суммирующего усилителя подключен масштабирующий резистор обратной связи, выход суммирующего усилителя через первый олерационный резистор присоедннгн к входу инвертирующего усилителя, выход которого соединен с эмиттером антилогарнфмнрующего транзистора, коллектор которого присоединен к входу и через третий нормирующий резистор - к выходу выходного усилителя, между входом и выходом инвертирующего усилителя подключен второй операционный резистор, отличающееся тем, что, с целью расширения динамического диапазона .входных -сигналов, базы первого и второго логарифмирующих транзисторов подключены к входу инвертирующего усилителя, база алтилогарифм.ирующего транзистора соединена со входом суммирующего усилителя. Источники информации, принятые во внимание при экспертизе изобретения: 1.Авторское свидетельство СССР ° 524191, «л. G 06 G 7/16, 1975. 2.Л1. Conti, G. Graffuri. Moltiplicatori logaritmici per calcolatrica analogica. «Alta freguenza, 1965, v. 34, № 12, 828-831, fig. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Аналоговое логарифмическое вычислительное устройство | 1982 |

|

SU1095198A1 |

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Устройство с регулируемым усилением | 1988 |

|

SU1741257A1 |

| Аналоговое логарифмическое вычислительное устройство | 1983 |

|

SU1137486A2 |

| Фотоприемное устройство | 1987 |

|

SU1548673A1 |

| Устройство регулирования уровня сигнала | 1982 |

|

SU1104653A1 |

| Устройство усиления | 1985 |

|

SU1338001A1 |

| Аналоговый логарифмический преобразователь | 1979 |

|

SU790002A1 |

| Множительно-делительное устройство | 1987 |

|

SU1543426A1 |

Авторы

Даты

1978-06-30—Публикация

1976-06-22—Подача