рез второй и третий дополнительные резисторы соответственно, а второй четырехполюсник выполнен в виде последовательно соединенных четвертого, пятого и .шестого дополнительных резисторов, при этом вывод четвертого дополнительного резистора и точка . соединения пятого и шестого дополнительных резисторов являются соот653

ветствующими входами второго четырехполюсника, а второй вывод шестого дополнительного резистора и точка соединения четвертого и пятого дополнительных резисторов являются соответствующими выходами второго четырехполюсника .

Приоритет по пунктам:

26.04.82 по пп. и 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство регулирования уровня сигнала | 1984 |

|

SU1223340A2 |

| Устройство усиления | 1985 |

|

SU1338001A1 |

| Устройство с регулируемым усилением | 1988 |

|

SU1741257A1 |

| Устройство усиления | 1989 |

|

SU1617629A1 |

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Множительно-делительное устройство | 1987 |

|

SU1543426A1 |

| Аналоговое логарифмическое вычислительное устройство | 1982 |

|

SU1095198A1 |

| Аналоговое множительное устройство | 1976 |

|

SU613333A1 |

| Устройство автоматической регулировки усиления | 1988 |

|

SU1732428A1 |

1. УСТРОЙСТВО РЕГУЛИРОВАНИЯ УРОВНЯ СИГНАЛА, содержащее последовательно соединенные первый логарифмический усилитель и первый антилогарифмирующий транзистор, последовательно соединенные второй логарифмический усилитель и второй антилогарифмирующий транзистор, причем каждый логарифмический усилитель образован соответствующим операционным усилителем с дополнительным транзистором в цепи отрицательной обратной связи, при этом базы дополнительных транзисторов являются управляющим входом устройства, отличающееся тем, что, с целью уменьшения уровня шума, в него введены первый инвертирующий усилитель, подключенный к выходу первого антилогарифмирующего транзистора, второй инвертирующий усилитель, включенный между выходом второго антилогарифмирующего транзистора и входом первого инвертирующего усилителя, а также первый и второй четырехполюсники, входы второго четырехполюсника подключены к входу и выходу первого четырехцолюсника. выходы - к входам первого и второго логарифмических усилителей соответственно, при этом один из четырехполюсников выполнен нелинейньм. 2.Устройство по п. 1, отличающееся тем, что первый четырехполюсник выполнен в В1аде первого дополнительного инвертирзпощего усилителя, а второй четырехполюсник - в виде соединенный последовательно встррчно первого и второго лиодов, первые выводы которых являются соответствующими входами -второго четьфехполюсника, параллельно каждому диоду включены последовательно соединенные первый и второй резисторы, Сточка соединения которых является соответствующим выходом второго четырехполюсника; 3.Устройство по п. 1, отличающееся тем, что первый четырехполюсник содержит входной резистивный делитель напряжения, к отводу которого подключен неинHffiei вертирующий вход первого дополнительного операционного усилителя с 4 дополнительным диодом в цепи отрицательной обратной связи, к выходу первого дополнительного операционного 01 усилителя подключены последовательно со соединенные дополнительный анти- . .логарифмирующий транзистор и второй дополнительный инвертирующий усили- . тель с первым дополнительным резистором в цепи отрицательной обратной связи, выход которого является выходом первого четьфехполюсника, инвертирующие входы первого дополнительного операционного усилителя и -второго дополнительного инвертирующего усилителя подключены к шине питания че

f

Изобретение относится к радиотехнике и может быть использовано в устройствах регулирования уровня сигнала, реализующих принцип электронного управления.

Известен, например, усилитель с переменным усилением, в котором используется дифференциальный каскад на транзисторах с управляемым режимом смещения ij.

Эти транзисторы вместе со вспомогательными цепями являются источниками шума,понизить уровень которого оказывается затруднительным.

Наиболее близким по технической сущности к изобретению является устройство регулирования уровня Ъигна|ла, содержащее последовательно соединенные первый логарифмический усилитель и первый антилогарифмирующий транзистор, последорательно соединенные второй логарифмический усилитель и второй антилогарифмирующий транзистор, причем каждый логарифмический усилитель образован соответствующим операционным усилителем с дополнительным транзистором в цепи отрицательной обратной связи, при этом базы дополнительных и антилогарифмирующих транзисторов являются управляющими входами устройства С2 .

Однако транзисторы в известном устройстве также являются основными источниками шума, причем практически равноценными, особенно при максимальном коэффициенте передачи регулятора уровня (усилителя). Снижение уровня шума в известном устройстве путем, например, уменьшения тока оказывается неэффективным, так как приводит к снижению усиления этих транзисторов по напряжению и возрастанию влияния U

шумов связанных с ними операционных усилителей.

Целью изобретения является уменьшение уровня шума.

Цель достигается тем, что в устройстве регулирования уровня сигнала содержащем последовательно соединенные первый логарифмический усилитель и первый антилогарифмирующий транзистор, последовательно соединенные второй логарифмический усилитель и второй антилогарифмирующий транзистор. Причем каждый логарифмический усилитель образован соответствующим операционным усилителем с дополнительным транзистором в цепи отрицательной обратной связи, при этом базы дополнительных транзисторов являются управляющим входом устрой ;тва ;введены первый инвертирующий усилитель, подключенный к выходу первого антилогарифмирующего транзистора, второй инвертирующий усилитель, включенный между выходом второго антилогарифмирующего транзистора и входом первого инвертирующего усилителя, а также первый и второй четырехполюсники, входы второго четырехполюсника подключены к входу и выходу первого четырехполюсника, выходы -к входам первого и второго логарифмических усилителей соответственно,при этом один из четырехполюсников выполнен нелинейным.

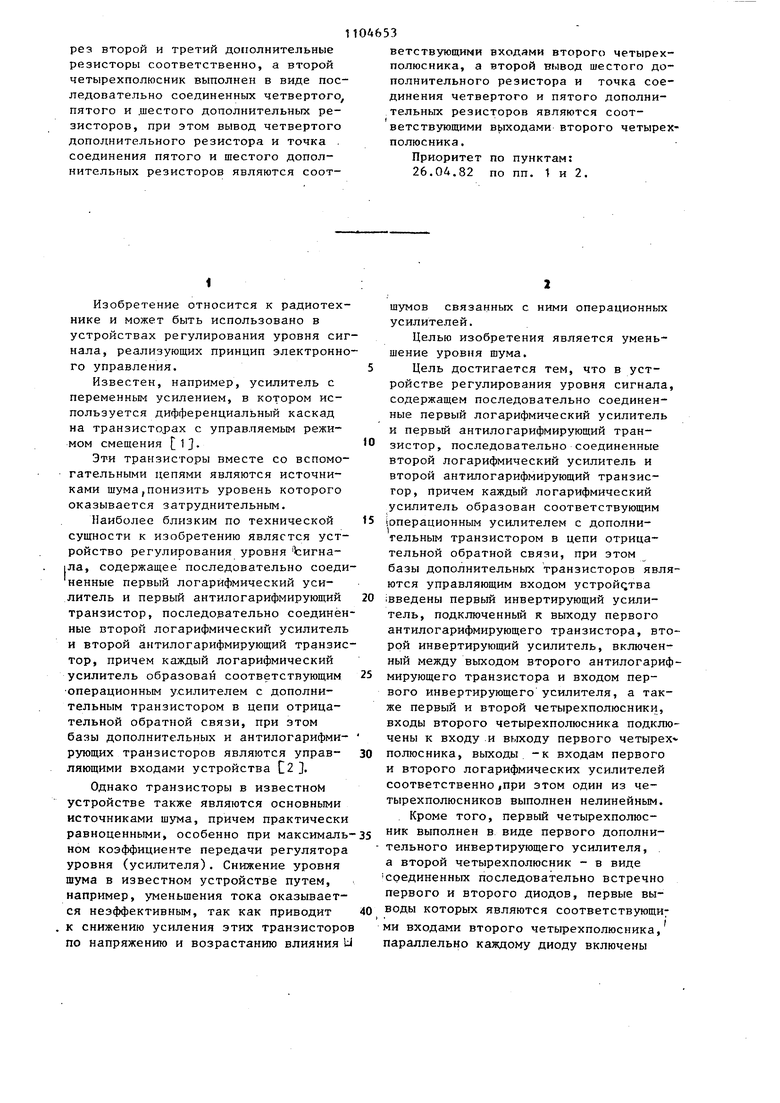

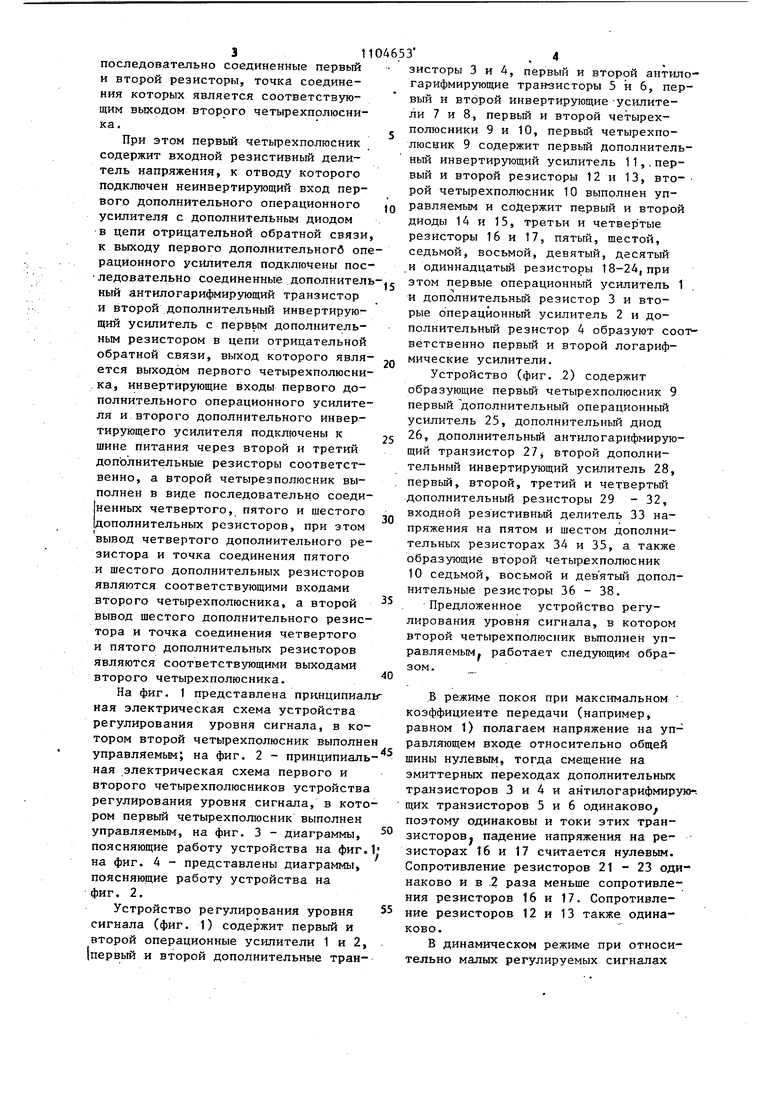

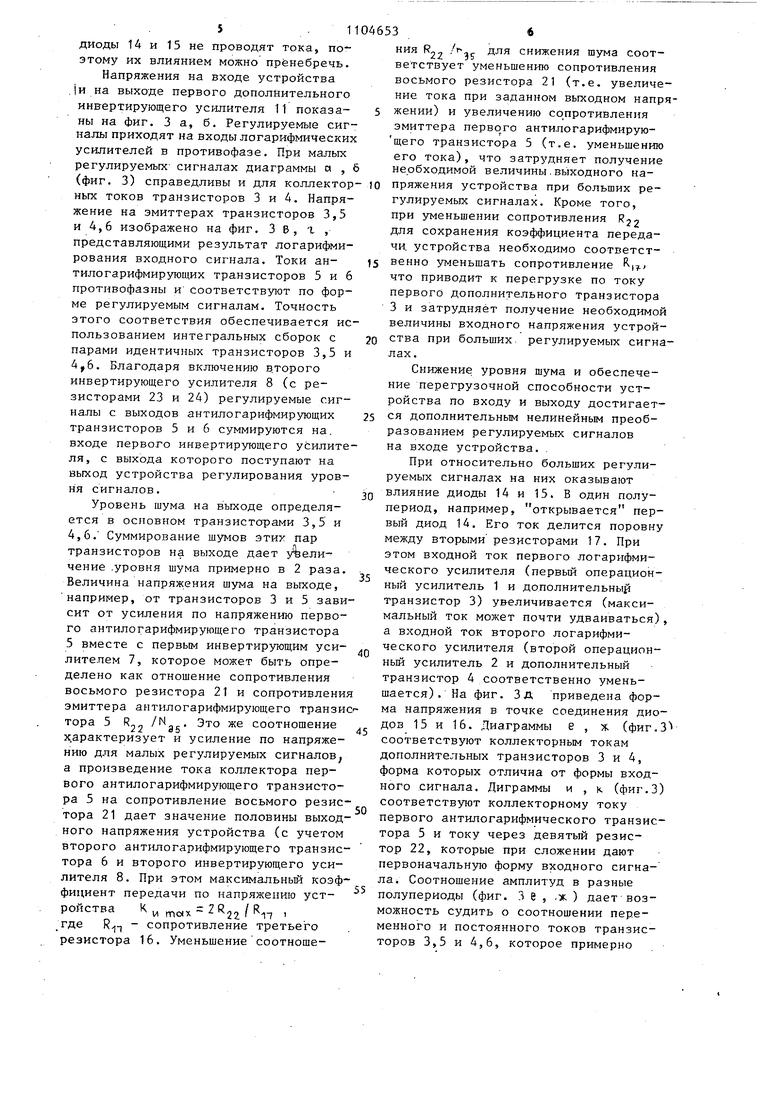

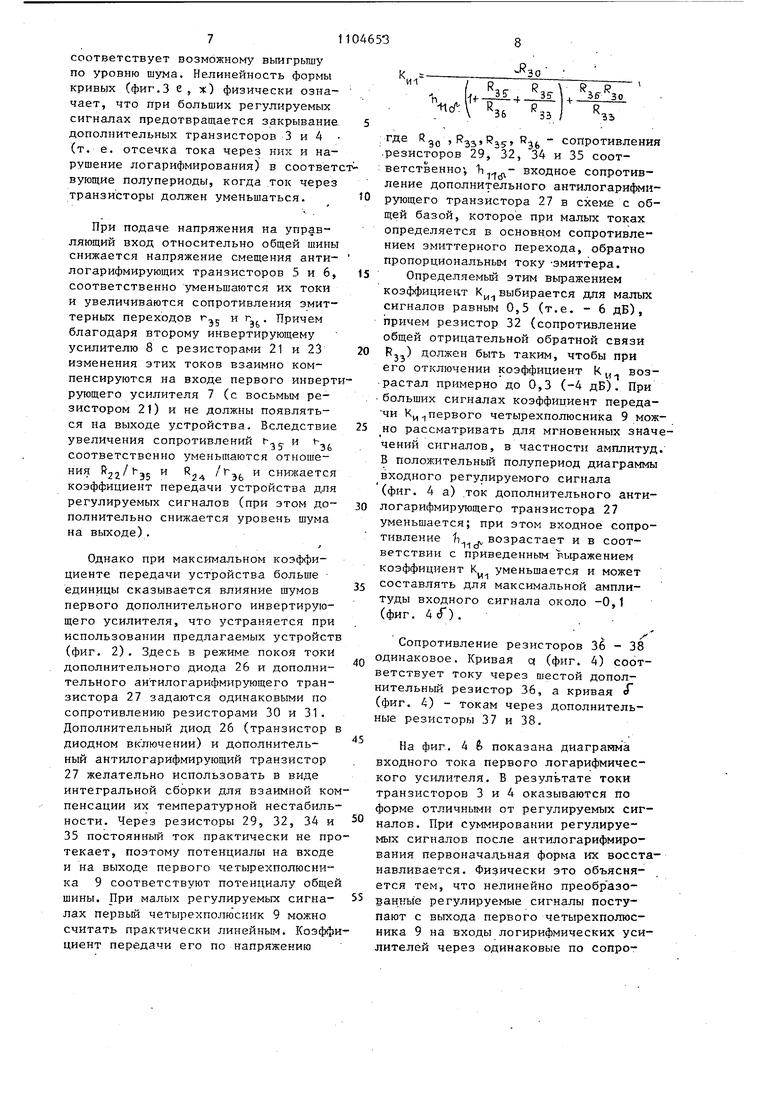

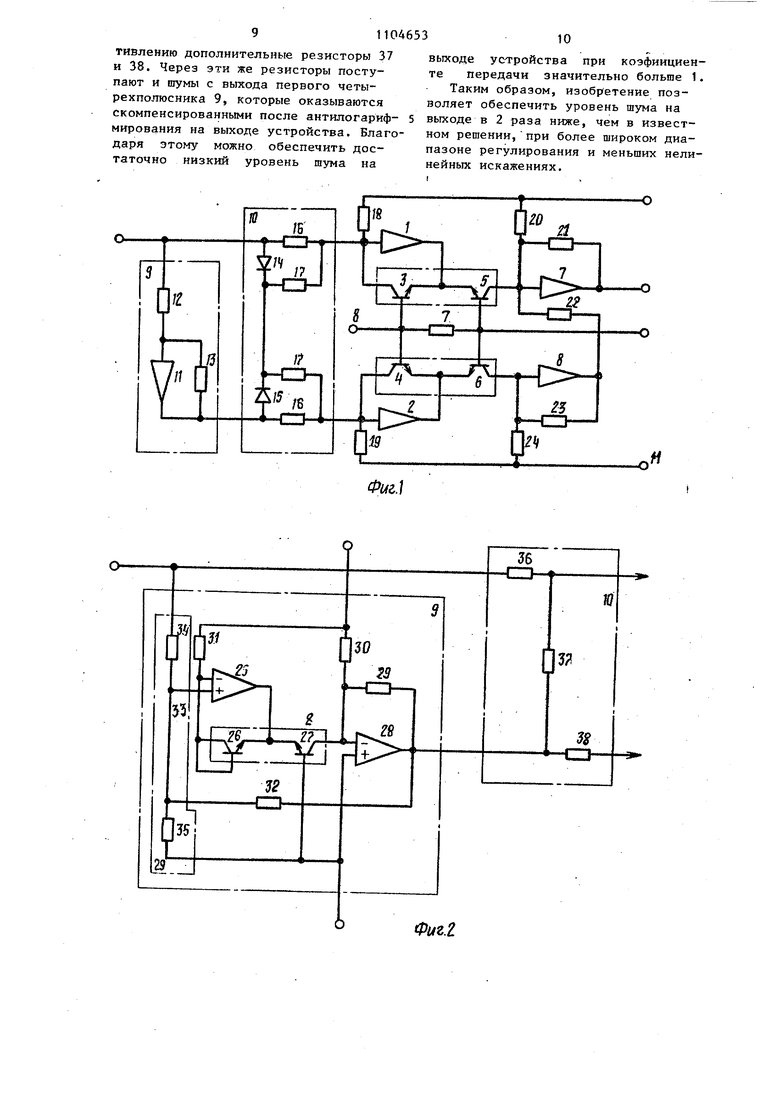

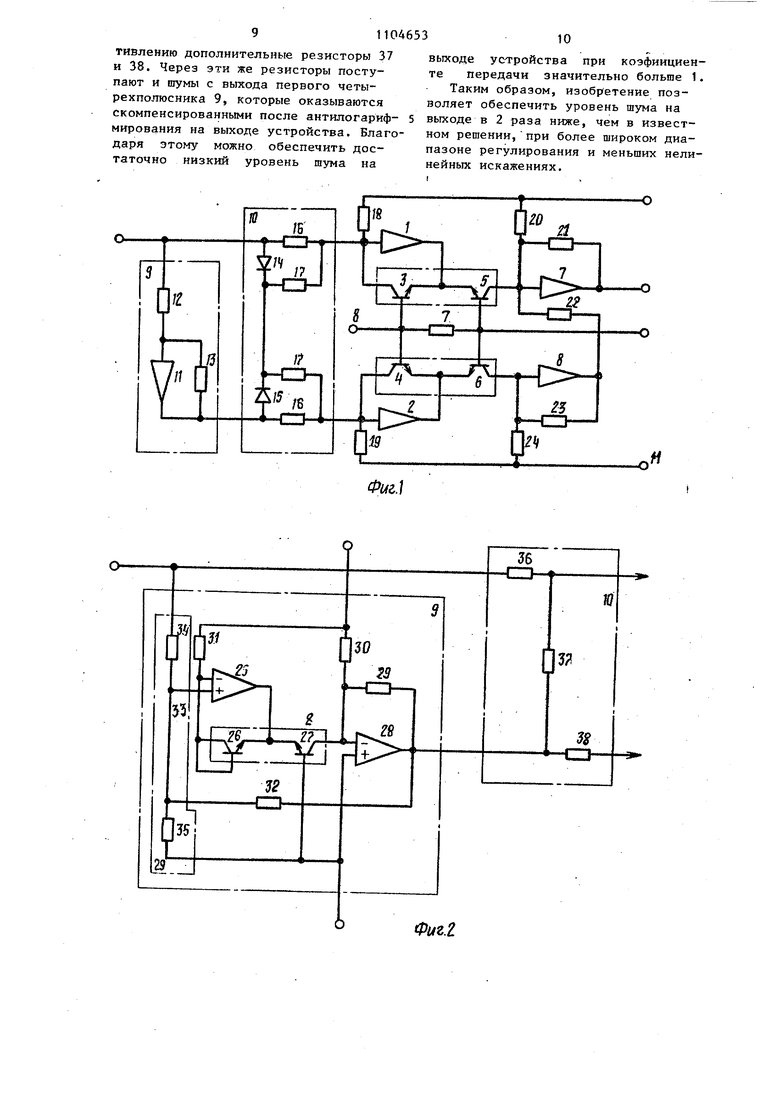

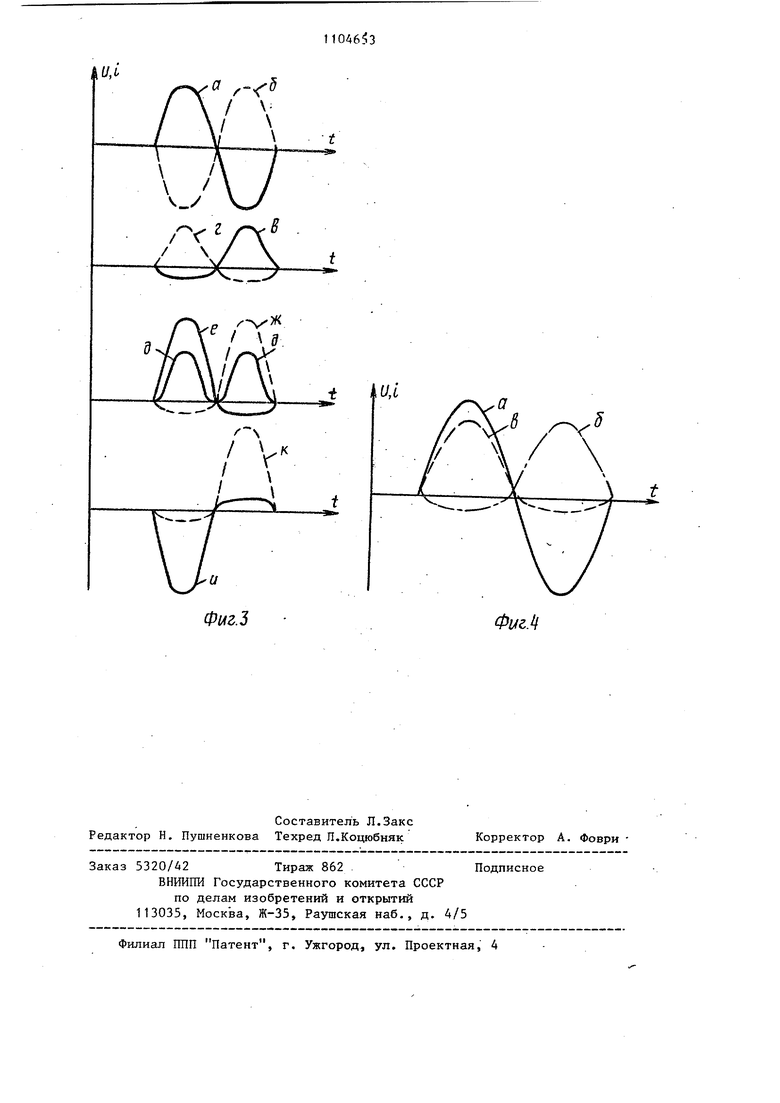

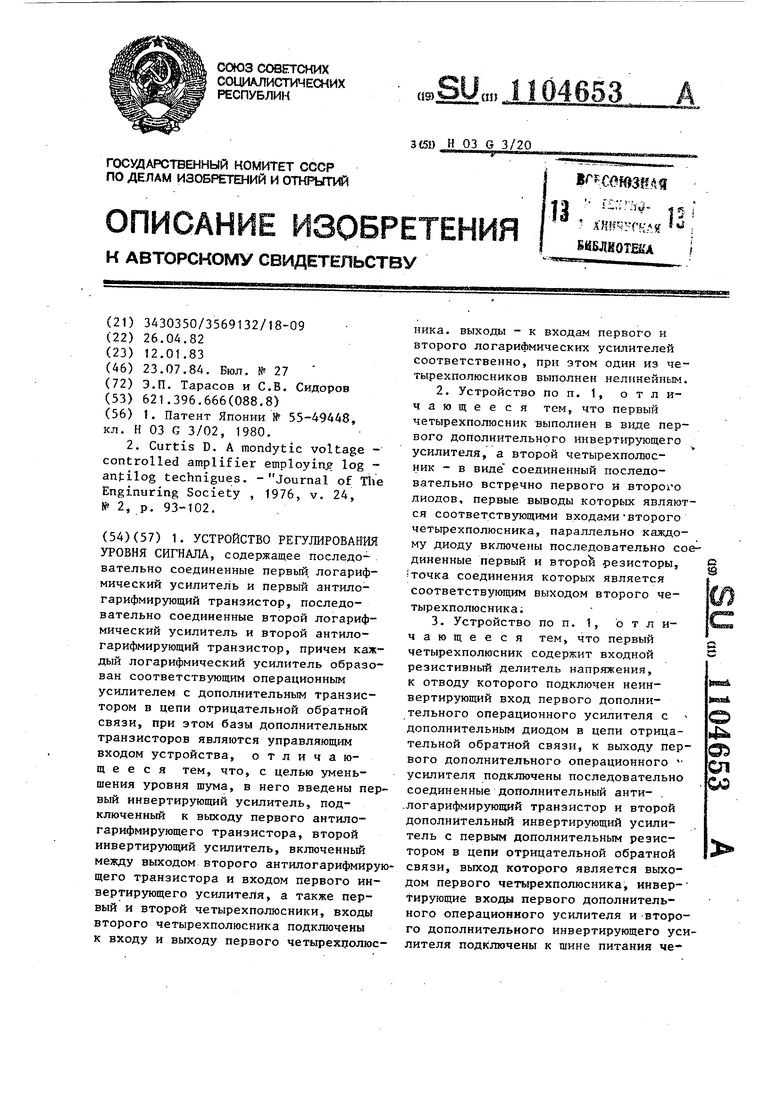

Кроме того, первый четырехполюсник выполнен в виде первого дополнительного инвертирующего усилителя, а второй четырехполюсник - в виде соединенных последовательно встречно первого и второго диодов, первые выводы которых являются соответствующими входами второго четырехполюсника, параллельно каждому диоду включены последовательно соединенные первый и второй резисторы, точка соединения которых является соответствующим выходом второго четырехполюсника. При этом первый четырехполюсник содержит входной резистивньй делитель напряжения, к отводу которого подключен неинвертирующий вход первого дополнительного операционного усилителя с дополнительным диодом в цепи отрицательной обратной связи, к выходу Первого дополнительногб опе рационного усилителя подключены последовательно соединенные дополнитель ный антилогарифмирующий транзистор и второй дополнительный инвертирующий усилитель с первьгм дополнительным резистором в цепи отрицательной обратной связи, выход которого является выходом первого четырехполюсника, инвертирующие входы первого дополнительного операционного усилителя и второго дополнительного инвертирующего усилителя подключены к шине питания через второй и третий дополнительные резисторы соответственно, а второй четырезполюсник выполнен в виде последовательно соединенных четвертого, пятого и шестого дополнительных резисторов, при этом вывод четвертого дополнительного резистора и точка соединения пятого и шестого дополнительных резисторов являются соответствующими входами второго четырехполюсника, а второй 1вывод щестого дополнительного резистора и точка соединения четвертого и пятого дополнительных резисторов являются соответствующими выходами второго четырехполюсника. На фиг. 1 представлена принципиал ная электрическая схема устройства регулирования уровня сигнала, в котором второй четырехполюсник выполне управляемым; на фиг. 2 - принципиаль ная электрическая схема первого и второго четырехполюсников устройства регулирования уровня сигнала, в кото ром первый четырехполюсник выполнен управляемым, на фиг. 3 - диаграммы, поясняющие работу устройства на фиг на фиг. 4 - представлены диаграммы, поясняющие работу устройства на фиг. 2. Устройство регулирования уровня сигнала (фиг. 1) содержит nepBbrti и второй операционные усилители 1 и 2 |первый и второй дополнительные транзисторы 3 и 4, первый и второй антило- гарифмирующие транзисторы 5 и 6, первый и второй инвертирующие-усилители 7 и 8, первый и второй четырехполюсники 9 и 10, первый четырехполюсник 9 содержит первый дополнительный инвертирующий усилитель 11,.первый и второй резисторы 12 и 13, вто- рой четырехполюсник 10 выполнен управляемым и содержит первый и второй диоды 14 и 15, третьи и четвертые резисторы 16 и 17, пятый, шестой, седьмой, восьмой, девятый, десятый и одиннадцатый резисторы 18-24, при этом первые операционный усилитель 1 , и дополнительный резистор 3 и вторые операционный усилитель 2 и дополнительный резистор 4 образуют соответственно первый и второй логарифмические усилители. Устройство (фиг. 2) содержит образующие первый четырехполюсник 9 первый дополнительный операционный усилитель 25, дополнительный диод 26, дополнительный антилогарифмирующий транзистор 27j второй дополнительный инвертирующий усилитель 28, первый, второй, третий и четвертьп дополнительный резисторы 29 - 32, входной резистивный делитель 33 напряжения на пятом и шестом дополнительных резисторах 34 и 35, а также образующие второй четырехполюсник 10 седьмой, восьмой и девятый дополнительные резисторы 36 - 38. Предложенное устройство регулирования уровня сигнала, в котором второй четырехполюсник вьшолнен управляемым, работает следующим образом. В режиме покоя при максимальном коэффициенте передачи (например, равном 1) полагаем напряжение на управляющем входе относительно общей шины нулевым, тогда смещение на эмиттерных переходах дополнительных транзисторов 3 и 4 и антипогарифмирую-. щих транзисторов 5 и 6 oдинaкoвo поэтому одинаковы и токи этих транзисторов, падение напряжения на резисторах 16 и 17 считается нулевым. Сопротивление резисторов 21-23 одинаково и в .2 раза меньше сопротивления резисторов 16 и 17. Сопротивление резисторов 12 и 13 также одинаково, В динамическом режиме при относительно малых регулируемых сигналах диоды 14 и 15 не проводят тока, поэтому их влиянием можно пренебречь. Напряжения на входе устройства .JH на выходе первого дополнительного инвертирующего усилителя 11 показаны на фиг. 3 а, б. Регулируемые сигналы приходят на входы логарифмических усилителей в противофазе. При малых регулируемых сигналах диаграммы а , (фиг. 3) справедливы и для коллектор ных токов транзисторов 3 и 4. Напряжение на эмиттерах транзисторов 3,5 и 4,6 изображено на фиг. 3 В, i ,представляющими результат логарифмирования входного сигнала. Токи антилогарифмирующих транзисторов 5 и 6 противофазны и соответствуют по форме регулируемым сигналам. Точность этого соответствия обеспечивается ис пользованием интегральных сборок с парами идентичных транзисторов 3,5 и 4,6. Благодаря включению второго инвертирующего усилителя 8 (с резисторами 23 и 24) регулируемые сигналы с выходов антилогарифмирующих транзисторов 5 и 6 суммируются на. входе первого инвертирующего усилите ля, с выхода которого поступают на вьгход устройства регулирования уровня сигналов. Уровень шума на выходе определяется в основном транзисторами 3,5 и 4,6. Суммирование шумов этих пар транзисторов на выходе дает у ели-чение .уровня шума примерно в 2 раза. Величина напряжения шума на выходе, например, от транзисторов 3 и 5 зави сит от усиления по напряжению первого антилогарифмирующего транзистора 5 вместе с первым инвертирующим усилителем 7, которое может быть определено как отнощение сопротивления восьмого резистора 21 и сопротивлени эмиттера антилогарифмирующего транзи тора 5 Я„„ /NOC-- Это же соотношение JL во х.арактеризует и усиление по напряжению для малых регулируемых сигналов; а произведение тока коллектора первого антилогарифмирующего транзистора 5 на сопротивление восьмого резис тора 21 дает значение половины выход ного напряжения устройства (с учетом второго антилогарифмирующего транзис тора 6 и второго инвертирующего усилителя 8. При этом максимальный коэф фициент передачи по напряжению устройства К , , , где , - сопротивление третьего резистора 16. Уменьшение соотношедля снижения шума соответствует уменьшению сопротивления восьмого резистора 21 (т.е. увеличение тока при заданном выходном напряжении) и увеличению сопротивления эмиттера первого антилогарифмирующего транзистора 5 (т.е. уменьшению его тока), что затрудняет получение необходимой величины.выходного напряжения устройства при больших регулируемых сигналах. Кроме того, при уменьшении сопротивления для сохранения коэффициента передачи, устройства необходимо соответственно уменьшать сопротивление что приводит к перегрузке по току первого дополнительного транзистора 3 и затрудняет получение необходимой величины входного напряжения устройства при больших, регулируемых сигналах. Снижение уровня шума и обеспечение перегрузочной способности устройства по входу и выходу достигается дополнительным нелинейным преобразованием регулируемых сигналов на входе устройства. . При относительно больших регулируемых сигналах на них оказывают влияние диоды 14 и 15. В один полупериод, например, открывается первый диод 14. Его ток делится поровну между вторыми резисторами 17. При этом входной ток первого логарифмического усилителя (первый операционный усилитель 1 и дополнительны транзистор 3) увеличивается (максимальный ток может почти удваиваться), а входной ток второго логарифмического усилителя (второй операционный усилитель 2 и дополнительный транзистор 4 соответственно уменьшается) . На фиг. Зд приведена форма напряжения в точке соединения диодов 15 и 16. Диаграммы е , ж (фиг.З соответствуют коллекторным токам дополнительных транзисторов 3 и 4, форма которых отлична от формы входного сигнала. Диграммы и , к. (фиг.З) соответствуют коллекторному току первого антилогарифмического транзистора 5 и току через девятый резистор 22, которые при сложении дают первоначальную форму входного сигнапа. Соотношение амплитуд в разные полупериоды (фиг. 3 е , .ж ) дает возможность судить о соотношении переменного и постоянного токов транзисторов 3,5 и 4,6, которое примерно соответствует возможному вьгигрьшу по уровню шума. Нелинейность формы кривых (фиг.З е , ж) физически означает, что при больших регулируемых сигналах предотвращается закрывание дополнительных транзисторов 3 и 4 (т. е. отсечка тока через них и нарушение логарифмирования) в соответ вующие полупериоды, когда ток через транзисторы должен уменьшаться. При подаче напряжения на управляющий вход относительно общей шины снижается напряжение смещения антилогарифмирующих транзисторов 5 и 6, соответственно уменьшаются их токи и увеличиваются сопротивления эмиттерных переходов и г . Причем благодаря второму инвертирующему усилителю 8 с резисторами 21 и 23 изменения этих токов взаимно компенсируются на входе первого инверт рующего усилителя 7 (с восьмым резистором 21) и не должны появляться на выходе у.стройства. Вследствие увеличения сопротивлений з ъь соответственно уменьшаются отношения снижается коэффициент передачи устройства для регулируемых сигналов (при этом дополнительно снижается уровень шума на выходе). Однако при максимальном коэффициенте передачи устройства больше единицы сказывается влияние шумов первого дополнительного инвертирующего усилителя, что устраняется при использовании предлагаемых устройст (фиг. 2). Здесь в режиме покоя токи дополнительного диода 26 и дополнительного антилогарифмирующего транзистора 27 задаются одинаковыми по сопротивлению резисторами 30 и 31. Дополнительный диод 26 (транзистор диодном включении) и дополнительный антилогарифмирующий транзистор 27 желательно использовать в виде интегральной сборки для взаимной ко пенсации их температурной нестабиль ности. Через резисторы 29, 32, 34 и 35 постоянный ток практически не пр текает, поэтому потенциалы на входе и на выходе первого четырехполюсника 9 соответствуют потенциалу обще шины. При малых регулируемых сигналах первый четырехполюсник 9 можно считать практически линейным. Коэфф циент передачи его по напряжению К : гДе 30 33 35 36 сопротивления .резисторов 29,32, 34 и 35 соответственно; входное сопротивление дополнительного антилогарифмирующего транзистора 27 в схеме с общей базой, которое при малых токах определяется в основном сопротивлением эмиттерного перехода, обратно пропорциональным току -эмиттера. Определяемьп этим вьфажением коэффициент К выбирается для малых сигналов равным 0,5 (т.е. - 6 дБ), причем резистор 32 (сопротивление общей отрицательной обратной связи Rj) должен быть таким, чтобы при его отключении коэффициент K возрастал примерно до 0,3 (-4 дБ). При больших сигналах коэффициент передачи К первого четырехполюсника 9 рассматривать для мгновенных значечений сигналов, в частности амплитуд. В положительньм полупериод диаграммы входного регулируемого сигнала (фиг. 4 а) .ток дополнительного антилогарифмирующего транзистора 27 уменьшается; при этом входное сопротивление 1-1 возрастает и в соотП1 d ветствии с приведенным вьфажением коэффициент К уменьшается и может составлять для максимальной амплитуды входного сигнала около -0,1 (фиг. 4). Сопротивление резисторов 36 - 38 одинаковое. Кривая q (фиг. 4) соответствует току через шестой дополнительный резистор 36, а кривая «Г (фиг. 4) - токам через дополнительые резисторы 37 и 38. На фиг. 4 fe показана диаграмма входного тока первого логарифмического усилителя. В результате токи транзисторов 3 и 4 оказываются по форме отличными от регулируемых сигналов. При cy Jмиpoвaнии регулируемых сигналов после антилогарифмирования первоначадьная форма их восстанавливается. Физически это объясняется тем, что нелинейно преобразованные регулируемые сигналы поступают с выхода первого четырехполюсника 9 на входы логирифмических усилителей через одинаковые по сопро9110465тнвлению дополнительные резисторы 37 и 38. Через эти же резисторы поступают и шумы с выхода первого четырехполюсника 9, которые оказываются скомпенсированными после антилогариф- 5 мирования на выходе устройства. Благодаря этому можно обеспечить достаточно низкий уровень шума на

/Б О

.М выходе устройства при коэфинциенте передачи значительно больше 1, Таким образом, изобретение позволяет обеспечить уровень шума на выходе в 2 раза ниже, чем в известном решении,при более широком диапазоне регулирования и меньших нелинейных искажениях.

ku,i

Фкг.4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Curtis D | |||

| А mondytic voltage controlled amplifier employing log ant Hog technigues | |||

| - Journal of Tiie Enginuring Society , 1976, v | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

| Домовый номерной фонарь, служащий одновременно для указания названия улицы и номера дома и для освещения прилежащего участка улицы | 1917 |

|

SU93A1 |

Авторы

Даты

1984-07-23—Публикация

1982-04-26—Подача