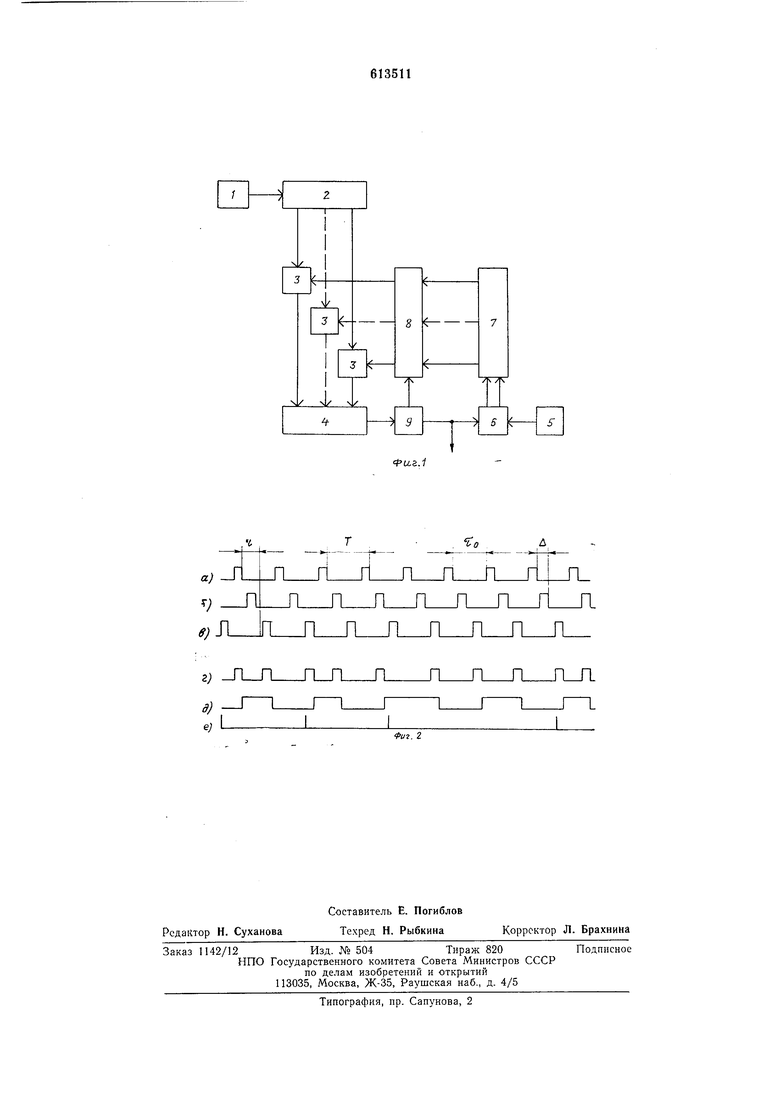

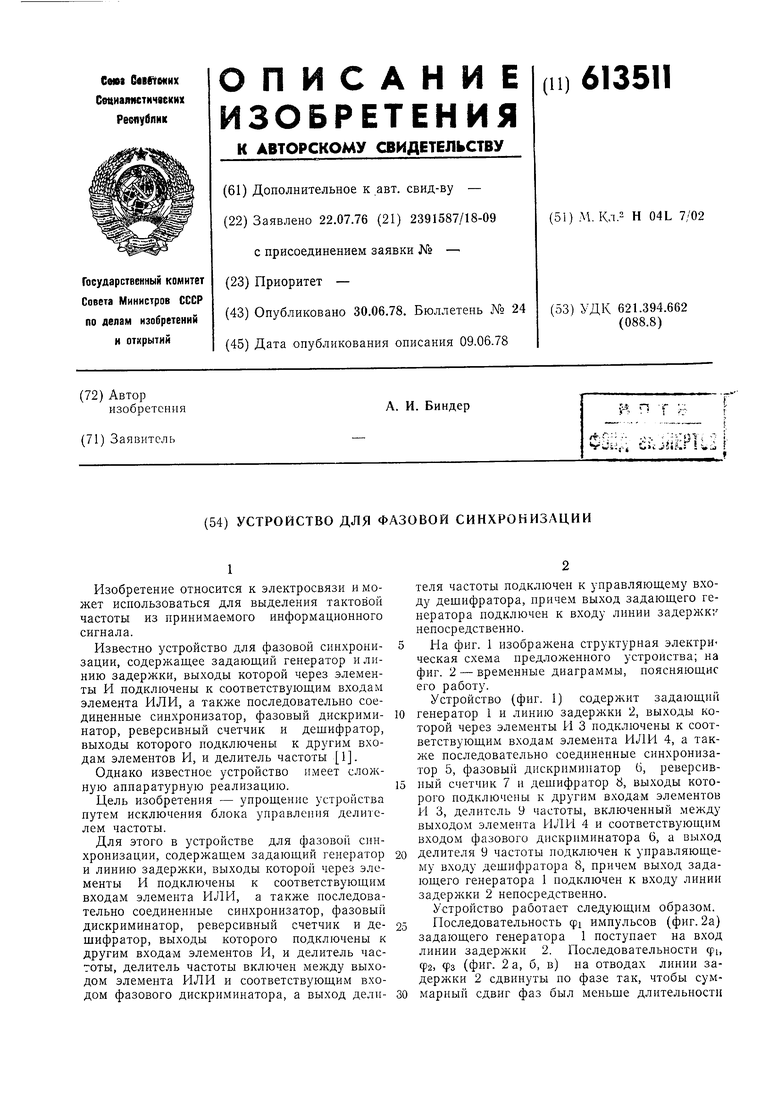

тактового интервала этих последовательностей на величину сдвига фаз между соседними последовательностями. Последовательности ф1, ф2, фз поступают на первые входы элементов И 3, вторые входы которых соединены с выходами дешифратора 8, логика работы которого обеспечивает подачу логической «единицы на вход одного из элементов И 3. Соответствующая последовательность фо (фиг. 2г) через элемент ИЛИ 4 поступает на вход делителя 9 частоты.

В фазовом дискриминаторе 6 происходит сравнение фаз поступающих на его входы последовательностей фт, фс (фиг. 2д, е), где фт - последовательность на выходе делителя 9 частоты; фс - последовательность внешних синхроимпульсов от синхронизатора 5. В соответствии с результатом сравнения фаз рт и фс изменяется состояние дешифратора 8, что приводит к «перемещению логической «единицы со второго входа элемента И 3 на второй вход предыдущего или последующего элемента И 3. Например, при отставании фазы фт от фазы фс происходит «перемещение логической «единицы по «кольцу из элемента И 3, в соответствии с чем на вход делителя 9 частоты в качестве фо поочередно поступают последовательности фь ф2, фз в следующем порядке:

Ф1-фз-ф2-Ф1-фз п т. д. до тех пор, пока не будет устранено рассогласование фаз фсифт.

Таким образом, шаг коррекции фазы выходного сигнала фт равен величине задержки между соседними отводами линии задержки 2, причем процесс коррекции фазы фт осуществляется без измепения коэффициента деления делителя 9 частоты.

Для нормальной работы устройства необходимо выполнение следующих условий:

А.о;

,

где Д - щаг коррекции фазы;

т - задержка между моментом прихода на вход элемента ИЛИ 4 отрицательного фронта импульса последовательности фо и моментом изменения состояния элемента И 3 под воздействием сигналов дешифратора 8;

TO - науза между положительными импульсами последовательности фь

Т - период следования импульсов последовательности ф.

Выполнение приведенных условий может быть обеспечено различными способами. Например, в состав дешифратора 8 могут быть введены элементы памяти (триггеры), синхронизируемые сигналами с промежуточного выхода делителя 9 частоты.

В данном устройстве за счет замены управляемого делителя частоты незправляемыми, т. е. с постоянным коэффициентом деления, Зпрощается аппаратурная реализация и повыщается надежность.

Формула изобретения

Устройство для фазовой синхронизации, содержащее задающий генератор и линию задержки, выходы которой через элементы И подключены к соответствующим входам элемента ИЛИ, а также последовательно соединенные синхронизатор, фазовый дискриминатор, реверсивный счетчик и дешифратор, выходы которого подключены к другим входам элементов И, и делитель частоты, отличающееся тем, что, с целью упрощения устройства путем исключения блока управления делителем частоты, делитель частоты включен между выходом элемента ИЛИ и соответствующим входом фазового дискриминатора, а выход делителя частоты подключен к управляющему входу дешифратора, причем выход задающего генератора подключен к входу линии задержки непосредственно.

Источники информации, принятые во внимание при экспертизе

I. Авторское свидетельство СССР №308533, кл. И 04L 7/02, 1971.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| ВСЕСОЮЗН.АЯ ГAT:irriiG-ii:](Kn^ECHAeБ-^ | 1971 |

|

SU291357A1 |

| РАДИОНАВИГАЦИОННАЯ СИСТЕМА (БАГИС-А) | 1995 |

|

RU2097780C1 |

| УСТРОЙСТВО для ИЗМЕРЕНИЯ ДИФФЕРЕНЦИАЛЬНОЙ ФАЗЫ СИГНАЛОВ ЦВЕТНОГО ТЕЛЕВИДЕНИЯ | 1973 |

|

SU393811A1 |

| Преобразователь азимута | 1988 |

|

SU1609987A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для измерения фазочастотных характеристик четырехполюсников | 1988 |

|

SU1597784A1 |

| Устройство для фазовой синхронизации | 1982 |

|

SU1062879A1 |

| Устройство синхронизации | 1982 |

|

SU1167748A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

Авторы

Даты

1978-06-30—Публикация

1976-07-22—Подача