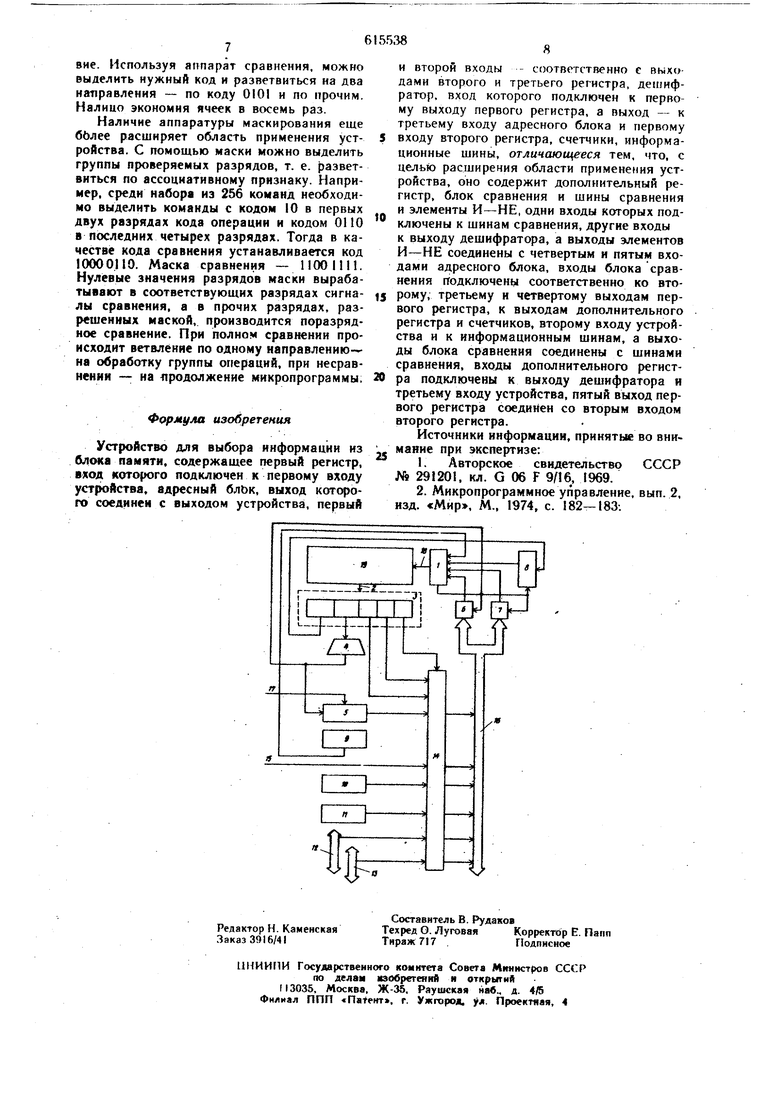

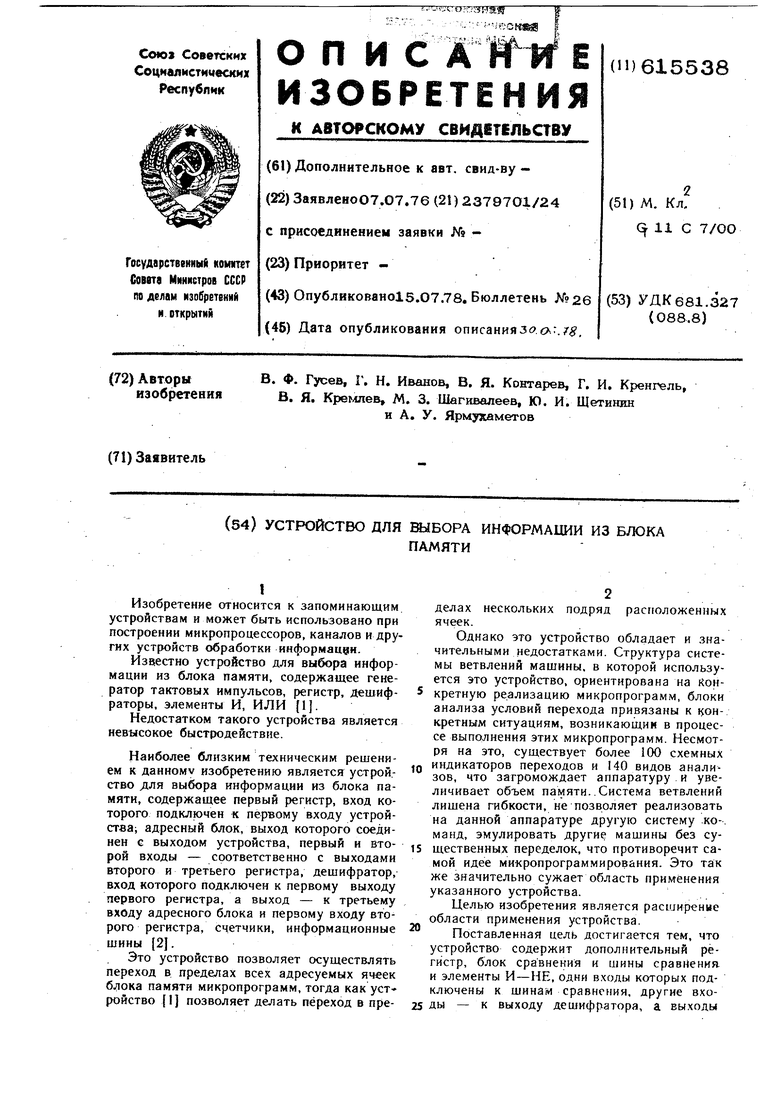

элементов И-НЕ соединены с четвертым и пятым входами адресного блока,входы 0лока сравнения подключены соответственно ко второму, третьему и четвертому выходам первого регистра, к выходам дополнительного регистра, и счетчиков, второму входу устройства и к информационным шинам, а выходы блока сравнения соединены с шинами сравнения, входы дополнительного регистра подключены к выходу дешифратора и третьему входу устройства, пятый выход первого регистра соединен со вторым входом второго регистра. Па чертеже изображена блок-схема предлагаемого устройства. Устройство содержит адресный блок I, предназначенный для выработки адреса еледующей выбираемой ячейки памяти. Первый вход 2 устройства подключен ко входу первого регистра 3. Регистр 3 предиаз.начеи для хранения команд и содержит поле констант, операционное поле, поле кода сравнения, поле маски и поле анализов. Устройство также содержит дешифратор 4, предиазпаченный для выработки сигналов микроопераций, дополнительный регистр 5, служащий для хранения анализа, состояний, элементы И-НЕ 6. 7, второй 8 и третий 9 регистры, служащие соответственно для храneHHif информации о переходах и начальном адресе, счетчики 10 и 11. информационные шины 12 и 13, блок сравиеикя 14, второй вход 15 устройства, шииы сравнения 16, третий вход 17 устройства. Выход блока I соединен с выходом 18 устройства. Ко входу 2 и выходу 18 устройства подключен блок памяти 9. Первый и второй входы блока I соединены соответственно с выходами регистров 8 и 9, Вход дешифратора 4 подключен к первому выходу регистра 3, а выход к третьему входу блока I и первому входу регистра 8. Один входы элементов 6 и 7 подключены к шинам 16, другие вхбды - к выходу дешифратора 4, а выходы соединены с четвертым и пятым входами блока I, Входы блока 14 подключены соответствеино ко второму, третьему и четвертому выходам регистра 3, к выходам регистра 5 и счетчиков 10, 11, второму входу 15 устройства и шинам 12, 13. Входы регистра 5 подключены к выходу дешифратора 4 и третьему входу 17 устройства. Пятый выход регистра 3 соединен со вторым входом perHCjtpa 8. Устройств работает следующим образом. ПредпЬложим, устройством выполняет ся некоторая команда системы команд. Код команды предварительно загружается на регистр 9 и по сигналу с дешифратора 4, поступающему на вход адресного блока I, содержимое регистра 9 подается на блок памяти 19, например, односторонней в качестве начального адреса микропрограммы выполненной данной команды. Адрес первой микрокоманды каждой микропрограммы содержнт код команды в качестве с(х:тавной части. Адресованная ячейка блока памяти 19 .читается на регистр 3. Операционное поле этого регистра дешифруется на дешифратора 4, и сигналы микроприка.з()в с его выхода управляют устройством в течение одного такта работы. Это могут быть микроприказы загрузки констант на счетчики 10 и 11, пересылки данных по шинам 12 и 13 и т. п. действия по обработке информации. Достаточно сложные микропрограммы, как правило, имеют общие блоки стандартной обработки данных - так называемые микропрограммы. Для возврата на основную ветвь микропрограммы перед входом в мнкропрограмму по сигналу из дешифратора 4 на регистр перехода 8 загружается из поля констант адрес возврата, специфичный для каждого случая. Последняя ячейка микропрограммы содержит микроприказ безусловного возврата на основную ветвь. Сигналом с дешифратора 4, содержнмое регистра 8 передается через адресный блок 1 в блок памяти 19 в качестве адреса продолжения основной ветви микропрограммы. Таким образом в устройстве осуществляется безуС ловный возврат на Микропрограмму из мнкроподпрограммы. Набор команд современных вычислительных машин можно разделить на группы по различным признакам.. Одним из этих признаков может служить источник операндов, например, оперативная память, быстрые регистры, определенное тюле команды и т. д., однако вид обработки данных, определяемый командами, может быть один и тот же. Другим признаком может служить формат данных (операнды длиной в слово, полуслово, двойной длниы, в четыре слова и т. п.). Прн этом внд обработки один и тот же. В этих случаях для сокращения объема памяти микропрограммы целесообразно иметь одну общую микропрограмму обработки с разными входами и разными выходами. Как правило, существуют команды, в которых совпадают как источники данных,так и приемы их обработки, за исключением одного-двух действий, специфичных для коикретной команды. Примером могут служить операции логической обработки полей перемеиной длины. В этих операциях осиовное время и подавляющее количество микрокоманд предиазначено для выполнения процессов извлечення операндов из памяти, их выравнивания, компановки и г. п., а собственно логическая обработка занимает один-два такта. В таких случаях целесообразно иметь одну микропрограмму для всех операц|;й, с общям входом и общим выходом, но выделять небольшие специфичные участки для каждой команды. Встречаются также и taKHe случаи, когда несколько . Можно выполнять по одной и той же микропрограмме, но закончить обработку в разйое время. Примером может служнть команда сравнения, устанавлива щая прнзнак (больше, меньше, равно), м не изменяющая операндов, у команду

можно выполнять по микропрограмме пычитания, т рервайее выполнение до ветви записи результата. В этом случае решение о прекрашетжн операции принимается по колу команды. Команду умножения полуслов можио выполнять по микропрограмме умножения целых слов, прервав цикл по содержимому счетчиков. Иногда возникает необходимость проанализнровать передаваемые по информационным шинам данные для принятия решения с ветвлений, например, проверить знак результата и т, п.

Для оптимальной реализации вышеперечисленных примеров предлагается аппарат ветвления по адресу возврата при сравнении.

Рассмотрим работу устройства в режиме ухода по адресу возврата при сравнении.

В одном из первых тактов микропрограммы выполнения группы операций по сигналу из дешифратора 4 на регистр 8 загру жается из поля констант регистра 3 адрес перехода, например адрес начала выборки следующей команды. На определенном этапе выполнения микропрограммы производится анализ содержимого определенного регистра, например регистра 9. Номер проверяемого регистра задается полем анализов регистра 3. Сигнал анализа либо непосредственно из поля, либо с некоторого дешифратора (на чертеже не показан) включает блок сравнения 14, к входам которого подключен проверяемый регистр. На другие входы блока 14 подается код сравнения из поля кода сравнения регистра 3 и маска сравнения из поля маски регистра 3. Блок срав;нения 14 выполняет операцию поразрядного сравнения содержнмого регистра и содержимого поля кода сравнения под маской, определяемой содержимым поля маски. Наличие единицы в соответствующем разряде кода маски разрешает операцию сравнения, наличие нуля - з«1рещает сравнение. Блок сравнения 14 вырабатывает сигнал сравнения в том разряде, где код сравнения совпал со значением разряда регистра и в том разряде, где нулевая маска. Элементы И-НЕ 6 и 7 проверяют наличие совпадения во всех шинах 16. Одновременно с микроприказом анрлиза дешифратором 4 вырабатываются микроприказы сравнения, которые поступают на элементы И-НЕ 6 и 7 в зависимости от заданного режима переходов. Если все шины 16 указывают, что поразрядное сравнение на выбранном блоке прошло и включен элемент И-НЕ 6, то он вырабатывает сигнал на адресный блок I, который передает содержимое регистра 8 в качестве следуюшего адреса в блок памяти 19. Таким образом нормальное течение микропрограммы прерывается, устройство начинает выполнять выборку следуюшей команды или другую ветвь микропрограммы. Если же совпадения не произошло, то микропрограмма выполняется дальше по обычной нормальной последовательности адресов.

{{ели включен ; лемент И-НИ 7 и нл inniiax 16 зги{)иксир()вано сравнение, то сигнал с элемента 7 поступает на адресный блок и вызывает модификацию 5 нескольких разрядов следующего адреса микрокоманды. Это второй метод ветвления по сравнению.

Регистр 5 предназначен для хранения результатов анализа состояния блоков устройства. Результат анализа состояния блоков (аппаратура анализа на чертеже не. показана) по входу 17 записывается в регистр 5 и сохраняется там до тех пор, пока не возникает нужда в результатах анализа. Загрузка регистра 5 производится попутно в процессе передачи информации между блоками. Зачастую возникает необходимость использовать результат анализа данных или состояния, которые были несколько тактов назад. Этот прием позволяет экономить время и ячейки памяти.

0 Вход устройства 15 в отличие от регистра 5 предназначен для осуществления переходов по сравнеь,1ю, когда анализы производятся в такте ветвления. Результат анализа состояния блоков устройства по входу 15 поступает на блок сравнения 14 и в этом

же такте производится анализ сравнения, т. е. сигналом из поля анализов включается блок сравнения 14. В остальном работа устройства аналогнчна вышеописанной.

Выходы блока сравнения 14 выполнены

на элементах, позволяющих объединять их

на шинах 16, например на элементах с тремя устойчивыми состояниями.

Применение данного устройства позволяет значительно сократить объем памяти микропрограмм, во-первых, в результате выделения однотипных блоков стандартной обработки в микропрограммы, которые используются во многих микропрограммах. Причем устройство позволяет переключаться из микропрограммы на основную ветвь б«з потерь времени н затрат дополнительных ячеек. Во-вторых, ветвление по результату сравнения дает значительный выигрыш в адресах при сравнении при незначительных аппаратных затратах. Наличие аппаратуры сравнения кода регистров с кодом сравнения дает возможность разветвиться на два направления - либо найден искомый код, либо все остальные. В известном устройстве 2J ветвление производится по нескольким направлениям, из которых в одном случае производится одно действие, а во всех

0 прочих - однотипное другое действие. Например, необходимо выполнить одно действие при состоянии счетчика 0101 н другое действие при всех прочих его состояния. Если ветвление производится путем молие фикации адреса присвоением значения счетчика, некоторым разрядам адреса (так называемый функциональный переход. IBM- 360), то занимаются 16 ячеек памяти, из которых в пятнадцати выполняется однотипное действие, н только в ячейке с адресом

0 XXOIOI выполняется запланированное деист

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Запоминающее устройство | 1976 |

|

SU613401A1 |

| Запоминающее устройство | 1976 |

|

SU877613A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Микропроцессор | 1977 |

|

SU943735A1 |

| Микропроцессор | 1977 |

|

SU943734A1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Запоминающее устройство | 1976 |

|

SU613402A1 |

Авторы

Даты

1978-07-15—Публикация

1976-07-07—Подача