(5) МИКРОПРОЦЕССОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1977 |

|

SU943734A1 |

| Микропрограммное устройство управления | 1977 |

|

SU943727A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Микропроцессор | 1982 |

|

SU1035610A1 |

| Микропрограммное устройство для сопряжения процессора с абонентами | 1987 |

|

SU1539787A1 |

| Устройство микропрограммного управления | 1974 |

|

SU528568A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропроцессор | 1982 |

|

SU1045231A1 |

1

Изобретение относится к вычислительной технике и может быть использовано при построении процессоров ЭВМ различных классов и, в частности, микропрограммируемых эмулирующих однокристальных микропроцессоров.

Известно микропрограммное устройство управления, содержащее блок управления, память микрокоманд, регистр ,ц адреса микрокоманд, регистр микрокоманд },

Недостатком известного устройства является большой объем памяти и низкое быстродействие.

Наиболее близким по технической сущности является устройство для управления, содержащее регистр команд, арифметико-логический блок, блок регистров, два дешифратора, элементы И,2о ИЛИ, память микрокоманд, регистр микрокоманд, модификатор адреса, соединенные между собой соответствующим образом 2 .

Однако устройство характеризуется недостаточным быстродействием при работе с различными системами команд.

Целью изобретения является повышение быстродействия микропроцессора.

Поставленная цель достигается тем, что в микропроцессор, содержащий арифметико-логический блок, соединенный двусторонней связью с блоком регистров, другой вход которого через последовательно соединенные первые дешифратор и элемент ИЛИ соединен с выходом регистра команд, первый вход которого является первым входом микропроцессора , а второй вход соединен с первым выходом блока регистров, второй выход которого и первый выход арифметико-логического блока являются первым и вторым выходами микропроцессора, второй вход микропроцессора, выход регистра команд и второй выход арифметико-логического блока соединены со входами соответствующих элементов И группы, регистр адреса микрокоманд через память микрокоманд соединен с входом регистра микрокоманд, первый и второй выходы которого соединены соответственно с первым входом регистра адреса микрокоманд и входом второго дешифратора, дополнительно введены регистр номера системы команд, регистр адреса внешних микрокоманд, регистр внешних микрокоманд, коммутационная матрица, элементы ИЛИ, элементы И, коммутатор третий и четвертый дешифраторы,приче первый и второй выходы коммутатора соединены со входом первого элемента ИЛИ, второй выход коммутатора через второй элемент ИЛИ соединен с первым входом коммутационной матрицы остальные выходы коммутатора через элементы И группы соединены со входами третьего элемента ИЛИ, выход которого через коммутационную матрицу соединен со вторым входом регистра адреса микрокоманд и входом первого элемента И, третий, четвертый и пятый выходы регистра микрокоманд соединены со входами второго, третьего и четвертого элементов И, шестой выход регистра микрокоманд соединен со входом пятого элемента И и первым входом регистра адреса внешних микрокоманд, седьмой выход регистра микрокоманд соединен со входом шестого элемента И и через первый элемент И со вторым входом регистра адреса внешних микрокоманд, первый, второй и третий выходы регистра внешних микрокоманд через третий, пятый и шестой элементы И соединены соответственно с третьим входом регистра адреса внешних микрокоманд и третьим, четвертым входами регистра адреса микрокоманд, четвертый выход регистра внешних микрокоманд через четвертый элемент И соединен со входом третьего дешифратора и первым входом четвертого дешифратора, вход которого соединен со вторым выходом регистра микрокоманд, выходы второго, третьего и четвертого дешифраторов соединены со входами коммутатора, пятый выход регистра внешних микрокоманд через второй элемент И соединен с четвертым входом регистра адреса внешних микрокоманд и первым входом регистра номера системы команд, второй вход и выход которого являются третьими входом и ВЫ.ХОДОМ микропроцессора соответственно, пятый вход и выход

регистра адреса внешних микрокоманд являются четвертыми входом и выходом микропроцессора соответственно, входы регистра внешних микрокоманд и второго элемента ИЛИ являются пятым и шестым входами микропроцессора.

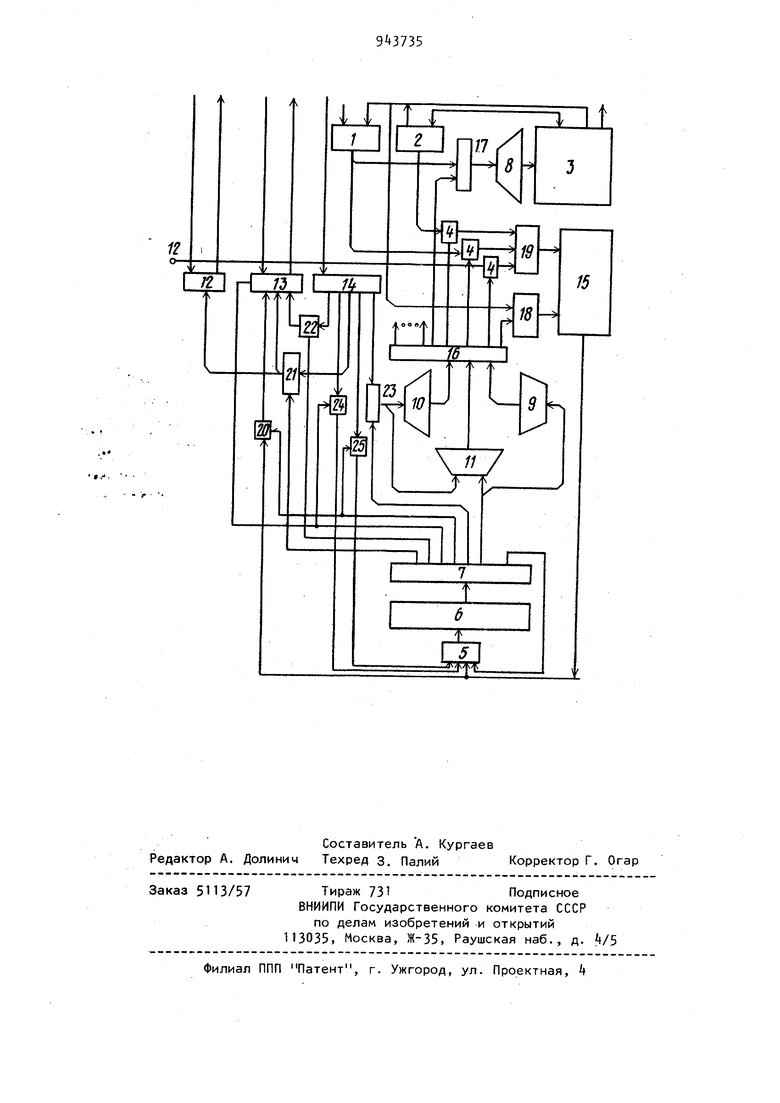

Структурная схема микропроцессора приведена на чертеже.

Микропроцессор содержит регистр 1 команд, арифметико-логический блок 2 блок 3 регистров, группу элементов И Ц, регистр 5 адреса микрокоманд, память 6 микрокоманд, регистр 7 микрокоманд, дешифраторы 8-11, регистр 12 номера систем команд, регистр 13 адреса внешних микрокоманд, регистр 1 внешних микрокоманд, коммутационная матрица 15, коммутатор 1б, элементы ИЛИ 17-19, элементы И 20-25.

Микропроцессор работает следующим образом.

По внешнему сигналу в регистрах 5, 13 и 12 устанавливаются начальные адреса, а в регистре И - начальное состояние. В соответствии с кодом регистра 5 из памяти 6 записывается в регистр 7 код микрокоманды, который затем расшифровывается дешифратором 9 или 11.

По начальному коду регистра 5 в регистр 7 принимается первая микрокоманда подпрограммы интерпретации в соответствии с которой читается из внешней памяти и записывается в регистр 1 код команды.

По микроприказам условий, поступающим через коммутатор 1б, регистр 1 через элементы И и элемент ИЛИ 13 подключается к коммутационной матрице 13, на которую также подается код маски через элемент ИЛИ 18. По коду адреса маски через элемент ИЛИ 17 и дешифратор 8 выбирается один из регистров блока 3, в котором записан код маски, определяющий группу анализируемых разрядов команды. Анализ команды или кодов условий осуществляется путем формирования адреса следующей микрокоманды.

Сформированный адрес записывается в регистр 5 и является адресом первой внутренней микрокоманды исполнительной части одной из основных команд, адресом внутренней микрокоманды читающей и интерпретирующей внешнюю микроконанду, микрокоманды, обеспечивающей переход к одной из эмулируемых систем команд или адресом микрокоманды, продолжающей интерпретацию команды.

При выполнении внутренней микропрограммы исполнительной части одной из основных команд работа устройства происходит аналогично описанной при интерпретации команды.

Выполнение подпрограммы смены номера системы команд осуществляется при вызове одной из эмулируемых систем команд с помощью дополнительной команды, содержащей абсолютный, относительный или косвенный адрес микропрограммы этой системы команд. При этом реализуется пересылка адреса из регистра 1 в регистр 12 и регистр 13 или по косвенному адресу, указанному в этой команде, читают из регистра блока 3 или из внешней памяти абсолютный адрес микропрогра мы одной из эмулируемых систем команд и записывают его в регистр 12 Переход от основной системы команд к одной из эмулируемых систем команд может быть осуществлен также с использованием, например, команды записи по адресу, входящей в основ ную систему команд, если она реализована внешней микропрограммой. В этом случае последнюю микрокоманду исполнительной части микропрограммы команды записи по адресу, реализующую при выполнении только основной системы команд возврат к выполнению подпрограммы интерпретации, распола гают в поле внешней памяти, доступном программисту. Для перехода к од ной из эмулируемых систем команд в адресной части команды записи по адресу указывается адрес ячейки памяти, содержащей последнюю микрокоманду этой же команды, по которому из арифметико-логического блока или одного из регистров блока 3 записывается ранее сформированная в нем микрокоманда безусловного пере хода первого типа. Эта микрокоманд и осуществляет переход к микропрограмме одной из эмулируемых систем команд, устанавливая в регистрах 12 и 13 соответствующий код адреса. Этот код .в регистре 12 сохраняется в течение выполнения микропрограммы данной эмулируемой системы команд. Аналогичные адресные команды (напри мер, записи по адресу) используются для программного перехода от одной из эмулируемых систем команд к другой или для возврата к основной системе команд процессора. В последнем случае вместо последней микрокоманды команды записи по адресу, входящей

в состав эмурируемой системы команд и осуществляющей во внешней микропрограмме возврат к блоку интерпретации этой системы команд, формируется микрокоманда безусловный переход

второго типа.

Переход к подпро|-рамме интерпретации внешних микрокоманд осуществляется при выполнении команд основной системы команд, не имеющих соответствующих исполнительных микропрограмм в памяти 6 и выполняемых внешними микропрограммами, или при вызове (с помощью команды записи по адресу) одной из эмулируемых систем команд. При переходе к подпрограмме интерпретации внешней микрокоманды в регистре 5 устанавливается нулевой код адреса, в соответствии с которым в регистр 7 записывается код микрокоманды, содержащей базовый адрес внутренних.микрокоманд, код основных микроприказов, расшифровываемых дешифраторами .9 или 11 и дополнительный микроприказ. В соответствии с основными микроприказами выполняется чтение внешней микрокоманды из внешней памяти по адресу, указанному в регистрах 12 и 13 и запись ее в регистр 1. Дополнительный микроприказ увеличивает содержимое регистра 13, например, на единицу младшего разряда и открывает элемент И 24. Адрес следующей внутренней микрокоманды формируется из кода адреса, содержащегося в текущей внутренней микрокоманде, и кода внешней микрокоманды, поступающих с регистра 7 и регистра 14 и записывается в регистр 5. В cooтвeтctвии с кодом регистра 5 из памяти б выбирается и принимается в регистр 7 микрокоманда, содержащая нулевой адрес следующей микрокоманды и микроприказ, открывающий элементы И 23- При этом код микроприказов с регистра 1 проходит через элементы И 23, дешифраторы 10 и 11 и, пройдя через коммутатор 16, поступает на элемент ИЛИ 17 и другие узлы микропроцессора, вызывая выполнение внешней микрокоманды выполнить. Микроприказы условий микрокоманда выполнить не формирует. Переход к выполнению внешней микропрограммы условный переход осуществляется в случае, если в регистр 1 принята микрокоманда условный переход. Соответственно внешней микрокоманде условный переход с по мощью внутренней микрокоманды осуществляется последовательно выбор группы, затем в каждой группе отдельных сигналов условий и/или анали зируемых разрядов команды, по которым затем осуществляется ветвление по внешней микропрограмме формированием соответствующего адреса в регистре 13) и, кроме того,возврат к выполнению подпрограммы интерпретации внешних микрокоманд, В соответствии с кодом регистра 5 из памяти 6 выбирается и принимается в регистр 7 микрокоманда, содержащая нулевой адрес следующей микрокоманды и дополнительные микроприказы. Один микроприказ открывает элемент И 23, разрешая дешифрацию, передачу на коммутатор 16 поля внешней микрокоманды условный переход и формирование соответствующих микроприказов, в том числе микроприказов условий, открывающих соответствующие элементы И 4, и код адреса маски на элементе ИЛИ 17 или код маски на элементе ИЛИ 18. Таким образом, осуществляется выбор группы сигналов условий, поступающих с элементов И 4 в коммутационную матрицу 15 и выбор в последней соответственно коду маски на ее входах анализируемых разрядов условий. Коммутационная матрица 15 выбирает из группы сигналовна ее входах только те, которые необходимы для анализа при ветвлении во внешней (или внутренней) микропрограмме, и запрещая остальные. Сигналы условий, прошедшие на выход коммутационной матрицы 15 и код маски с регистра 14 через элемент И 25 складывается, а результат через элемент И 20 записывается в регистр 13, благодаря чему осуществляется ветвление во внешней микропрограмме. Одновременно код через элементы И 22 с регистра 1 записывается в регистр 13, определяя во внешней памяти зону ветвлений, В регистр 5 с регистра 7 записывается нулевой код, осуществ ляя тем самым возврат к выполнению интерпретации внешних микрокоманд. Если на регистр 14 принята внешняя микрокоманда безусловный переход первого типа, то согласно этой микрокоманде с помощью внутренней микрокоманды осуществляется безусловный переход во внешней микропрограмме формированием в регистре 13 адреса микрокоманды, к которой осуществляется безусловный переход и затем возврат к выполнению интерпретации внешних микрокоманд, В соответствии с кодом регистра 5 из памяти 6 выбирается и принимается в регистр 7 микрокоманда, содержащая нулевой код адреса следующей микрокоманды и дополнительные микроприказы, открывающие элементы И 21, 22, пройдя через которые код регистра 14 записывается в регистр 13, т.е. в регистре 13 формируется адрес, указанный в поле внешней микрокоманды безусловный переход первого типа, Нулевой код адреса следующей микрокоманды регистра 7 записывается в регистр 5, осуществляя тем самым возврат к выполнению интерпретации внешних микрокоманд. Если на регистр 14 принята внешняя микрокоманда безусловный переход второго типа, то согласно этой микрокоманде с помощью внутренней микрокоманды осуществляется безусловный переход во внешней микропрограмме и переход к выполнению интерпретации, команд. Эта микрокоманда используется после выполнения внешней микропрограммы и означает возврат к выполнению внутренней микропрограммы . В соответствии с кодом регистра 5 из памяти 6 выбирается и записывается в регистр 7 микрокоманда, содержащая код адреса первой микрокоманды подпрограммы интерпретации комднд и дополнительные микроприказы, под действием которых содержимое поля микрокоманды безусловный переход второго типа .с регистра 14 проходит через элементы И 21, 22 и записывается в регистр 13. Код адреса регистра 7 записывается в регистр 5, и внутреннее устройство управления переходит к выполнению Интерпретации команд. Быстродействие процессора улучшено за счетструктурно-микропрограммной реализации универсальных средств анализа призна(ов условий и систем команд вне зависимости от их кодирования и форматов. Предложенное устройство содержит средства, принципиально позволяющие проанализировать, в частности, формат любой команды из любой.системы команд с помощью одной микрокоманды условного перехода, и средства, обеспечивающие программный переход от микропрограмм основной системы команд к микропрограмме любой из эмулируемых систем команд или от одной из эмулируемых систем команд к другой. Для анализа кодов условий в микропроцессоре предусмотрены взаимно-дополняющие по функциональным возможностям средства выбора группы условий, маскирования и формирования адресов зоны внешней памяти при ветвлениях. Формула изобретения Микропроцессор, содержащий арифме тико-логический блок, соединенный двусторонней связью с блоком регистров, другой вход которого через последовательно соединенные первые дешифратор и элемент ИЛИ соединен с выходом регистра команд, первый вход которого является первым входом микропроцессора , а второй вход соединен с первым выходом блока регистров второй выход которого и первый выход арифметико-логического блока являются первым и вторым выходами микропроцессора, второй вход микропроцессора, выход регистра команд и второй выход арифметико-логического блока соединены со входами соответствующих элементов И группы, регистр адреса микрокоманд через память микрокоманд соединен с входом регистра микрокоманд, первый и второй выходы которого соединены соответственно с первым входом регистра адреса микрокоманд и входом второго дешифратора, отличающийся тем, что, с целью повышения быстродействия, в него введены регистр номера системы команд, регистр адреса внешних микрокоманд,.регистр внешних мик рокоманд, коммутационная матрица, элементы ИЛИ, элементы И, коммутатор, третий и четвертый дешифраторы, причем первый и второй выходы коммутатора соединены со входом первого эле мента ИЛИ, второй выход коммутатора через второй элемент ИЛИ соединен с 510 первым входом коммутационной матрицы, остальные выходы коммутатора через элементы И группы соединены со входами третьего элемента ИЛИ, выход которого через коммутационную матрицу соединен со вторым входом регистра адреса микрокоманд и входом первого элемента И, третий, четвертый и пятый выходы регистра микрокоманд соединены со входами второго, третьего и четвертого элементов И, шестой выход регистра микрокоманд соединен со входом пятого элемента И и первым входом регистра адреса внешних микрокоманд, седьмой выход регистра микрокоманд соединен со входом шестого элемента И и через первый элемент И со вторым входом регистра адреса внешних микрокоманд, первый, второй и третий эыходы регистра внешних микрокоманд через третий, пятый и шестой элементы И соединены соответственно с третьим входом регистра адреса внешних микрокоманд и третьим, четвертым входами регистра адреса микрокоманд, четвертый выход регистра внешних микрокоманд через четвертый элемент И соединен со входом третьего дешифратора и первым входом четвертого дешифратора, второй вход которого соединен со вторым выходом регистра микрокоманд, выходы второго, третьего и четвертого дешифраторов соединены со входами коммутатора, пятый выход регистра внешних микрокоманд через второй элемент И соединен с четвертым входом регистра адреса вйешних микрокоманд и первым входом регистра номера системы комйнд, второй вход и выход которого являются третьим входом и выходом микропроцессора соответственно, пятый вход и выход регистра адреса внешних микрокоманд являются четвертыми входом и выходом микропроцессора соответственно, входы регистра внешних микрокоманд и второго элемента ИЛИ являются пятым и шестым входами микропроцессора. Источники информации, принятые во внимание при экспертизе . Авторское свидетельство СССР ff 331387, Kji. G 06 F 9/16, 1970. 2. Булей Г. Микропрограммирование, гл. 1,3, М., Мир, 1973 (прототип).

Авторы

Даты

1982-07-15—Публикация

1977-08-03—Подача