Изобретение относится к вычислительной технике и может быть использовано в качестве элемента ассоциативного поля в ассоциативных запоминающих устройствах и ассоциативных процессах с параллельной и последовательно поразрядной обработкой данных.

Известен накопитель для ассоциативного запоминающего устройства содержащий ассоциативные лчейки, каждая из которых содержит элемент памяти, выходы которого подключены к входам элемента сравнения, причем адресные входы элементов памяти и выходы элементов сравнения ячеек каждой строки ассоциативной матрицы подключены соответственно к шине адреса и шине сравнения данной строки, а Одноименные информационные входы элементов памяти и сравнения ассоциативных ячеек каждого столбца ассоциативной матрицы подключены к соответствующим информационным шинам данного столбца ассоциативной матрицы 1 .

Недостатком этого накопителя является его сложность вследс вие большого числа элементов ассоциативной ячейки и большого числа внешних выводов.

Наиболее близким техническим решением к данному изобретению является накопитель для ассоциативного запоминающего устройства, содержащий матрицу ассоциативных эле35ментов памяти и логические блоки по числу столбцов матрицы, каждый из которых содержит элементы И-НЕ и НЕРАВНОЗНАЧНОСТЬ, причем входы первого элемента И-НЕ и элемента НЕРАВНОЗНАЧНОСТЬ подключены к ин40формационным шинам матрицы, а выходы - к входам второго элемента И-НЕ, выход которого является контрольным выходом накопителя 2 . . .

Недостатком известного накопи45теля является невысокая достоверность считываемой информации, что снижает надежность накопителя.

Цель изобретения - повышение надежности накопителя.

50

Поставленная цель достигается тем, что а накопитель для ассоциативного эапс 1инающего устройства, содержащий матрицу ассоциативных элементов памяти, шины данных и

55 разрешения записи и логические блоки, каждый из которых содержит элементы И и элементы НЕ, причем один из входов и выход каждого ассоциативного элемента памяти каждой строки

60 атрицы подключены соответственно к шине адреса и шине результата сравнения, а другие входы каждого ассоциативного элемента памяти каждого столбца подключены к информационным шинам, в каждый логический блок введен элемент памяти, причем первые входы элемента памяти и первого элемента И и вход первого элемента НЕ подключены к шине данных выход первого элемента НЕ подключен к первому входу второго элемента И, вторые и третьи входы элементов И -соединены соответственно с выходами второго элемента НЕ и элемента памяти, второй вход которого и вход второго элемента НЕ подключены к шине разрешения записи, выходы элементов И подключены к информационным шинам.

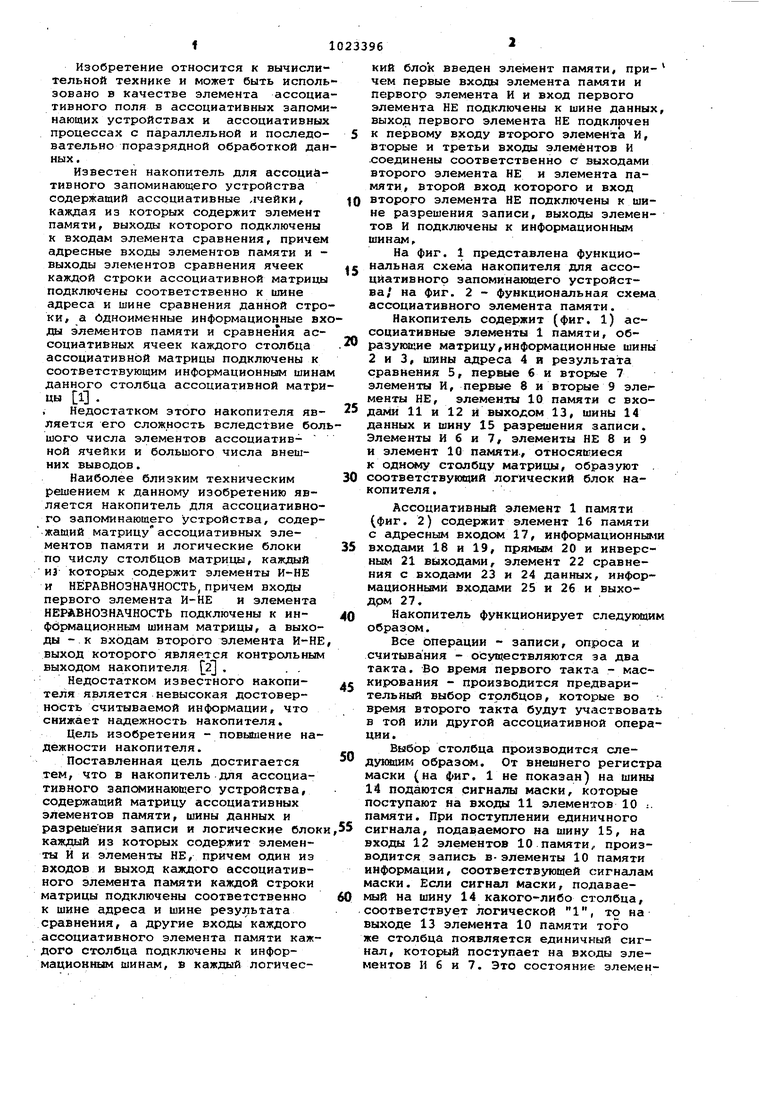

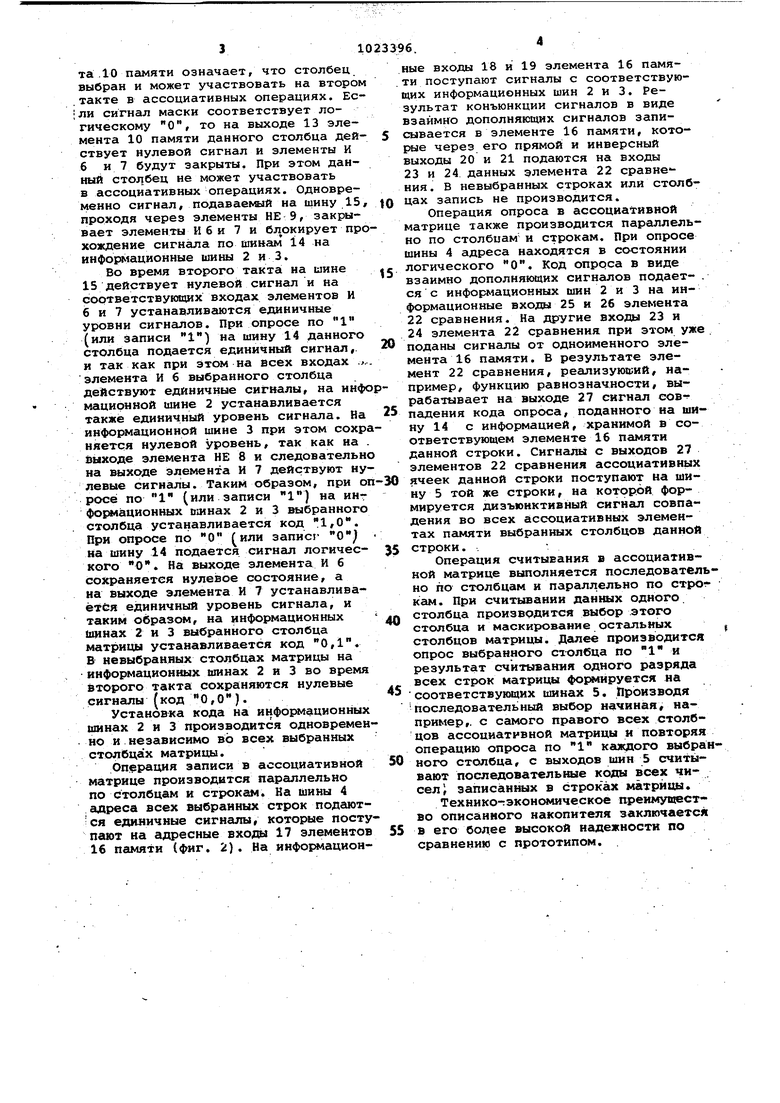

На фиг, 1 представлена функциональная схема накопителя для ассоциативного запоминающего устройства/ на фиг. 2 - функциональная схема ассоциативного элемента памяти.

Накопитель содержит (фиг, 1) ассоциативные элементы 1 памяти, образующие матрицу,информационные шины 2 к 3, шины адреса 4 и результата сравнения 5, первые 6 и вторые 7 элементы И, первые 8 и вторые 9 элегменты НЕ, элементы 10 памяти с входами 11 и 12 и выходом 13, шины 14 данных и шину 15 разраиения записи. Элементы И 6 и 7, элементы НЕ 8 и 9 и элемент 10 памяти., относящиеся к одисялу столбцу матрицы, образуют . соответствующий логический блок накопителя ,

Ассоциативньлй элемент 1 памяти (фиг, 2) содержит элемент 16 памяти с адресным входе 17, информационным входами 18 и 19, прямым 20 и инверсным 21 выходами, элемент 22 сравнения с входами 23 и 24 данных, информационными входами 25 и 26 и выходрм 27.

Накопитель функционирует следукяяи образом.

Все операции - записи, опроса и считывания - осуществляются за два такта. Во время первого такта - маскирования - производится предварительный выбор столбцов, которые во время второго такта будут участвоват в той или другой ассоциативной операции.

Выбор столбца производится следукяаим образе. От внешнего регистр маски (на фиг. 1 не показан) на шины 14 подаются сигналы маски, которые поступают на входы 11 элементов 10 :. памяти. При поступлении единичного сигнала, подаваемого на шину 15, на входы 12 элементов 10 памяти, производится запись в-элементы 10 памяти информации, соответствующей сигналам маски. Если сигнал маски, подаваемый на шину 14 какого-либо столбца, соответствует логической 1, то на выходе 13 элемента 10 памяти того же столбца появляется единичный сигнал, который поступает на входы элементов И 6 и 7, Это состояние: элемента .10 памяти означает, что столбец выбран и может участвовать на втором .такте в ассоциативных операциях. Ес;ли сигнал маски соответствует логическому О, то на выходе 13 элемента 10 памяти данного столбца действует нулевой сигнал и элементы И 6 и 7 будут закрыты. При этом данный столбец не может участвовать в ассоциативных операциях. Одновременно сигнал, подаваеко й на шину 15, проходя через элементы НЕ 9, закрывает элементы И б и 7 и бл окирует прохождение сигнала по ишнам 14 на инфop faциoнныe шины 2 и 3.

Во время второго такта на шине

15действует нулевой сигнал и на соответствующих входах элементов И б и 7 устанавливаются единичны.е уровни сигналов. При опросе по 1 (или записи 1) на шину 14 данного столбца подается единичный сигнал,. и так как при этом на всех входах ..элемента И 6 выбранного столбца действуют единичные сигналы, на инфомационной шине 2 устанавливается также единичный уровень сигнала. На информационной шине 3 при этом сохраняется нулевой уровень, так как на . выходе элемента НЕ 8 и следовательно

на выходе элемента И 7 действуют нулевые сигнашы. Таким образом, при оп росе по 1 (или записи 1) на информационных кшнах 2 и 3 выбранного столбца устанавливается код 1,0. При опросе по О (или записг О) на шину 14 подается сигнал логического О, На выходе элемента И б сохраняется нулевое состояние, а на выходе элемента И 7 устанавливается единичный уровень сигнала, и таким образом, на информационных шинах 2 и 3 выбранного столбца матрицы устанавливается код 0,1. В невыбранных столбцах матрицы на информационных шинах 2 и 3 во время второго такта сохраняются нулевые сигналы (код 0,0).

Установка кода на информационных шинах 2 и 3 производится одновременно и независимо во всех выбранных столбцах матрицы,

ОП| рация записи в ассоциативной матрице производится параллельно по столбцам и строкам. На шины 4 адреса всех выбранных строк подаются едш4ичные сигналы, котоЕше поступгиот на гшресные входы 17 элементов

16памяти (фиг. 2). На информационые входы 18 и 19 элемента 16 памяи поступают сигналы с соответствуюих информационных шин 2 и 3. Результат конъюнкции сигналов в виде заимно дополняющих сигналов запиывается в элементе 16 памяти, которые через его прямой и инверсный ыходы 20 и 21 подаются на входы

23и 24 данных элемента 22 сравнения. В невыбранных строках или столбцах запись не производится.

Операция опроса в ассоциативной атрице также производится параллельно по столбцам и строкам. При опросе ины 4 адреса находятся в состоянии логического О, Код опроса в виде взаимно дополняющих сигналов подает- . сяс информационных шин 2 и 3 на информационные входы 25 и 26 элемента 22 сравнения. На другие входы 23 и

24элемента 22 сравнения при этом уже поданы сигналы от одноименного элемента 16 памяти, В результате элемент 22 сравнения, реализую&;ий, например, функцию равнозначности, вырабатывает на выходе 27 сигнал совпадения кода опроса, поданного на шину 14 с информацией, хранимой в соответствующем элементе 16 памяти данной строки. Сигна ш с выходов 27 элементов 22 сравнения ассоциативных ячеек данной строки поступают на шину 5 той же строки, на которой формируется дизъюнктивный сигнал совпадения во всех ассоциативных элементах памяти выбранных столбцов данной строки. .

Операция считывания в ассоциативной матрице выполняется последовательно по столбцам и параллельно по стро кам. При считывании дан1шх одного столбца производится выбор этого столбца и маскирование остальных столбцов матрицы, Дгшее производится опрос выбранного стчэлбца по 1 и результат считывания одного разряда всех строк матрихда формируется на соответствующих шинах 5. Производя последовательный выбор начиная, например,, с самого правого всех столбцов ассоциативной матрицы и повторяя операцию опроса по 1 каждого выбранного столбца, с выходов шин 5 считывают последователыше коды всех чисел записанных в строках матрицы.

Технико-тэкономическое преимущество описанного накопителя заключается в его бодее высокой надежности по сравнению с прототипом.

j и

7

и

;1

| название | год | авторы | номер документа |

|---|---|---|---|

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2025796C1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1785039A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1718274A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2037892C1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1824650A1 |

| Ассоциативное запоминающее устройство | 1978 |

|

SU701349A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| Ассоциативное запоминающее устройство | 1984 |

|

SU1277210A1 |

НАКОПИТЕЛЬ ДЛЯ АССОЦИАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА, содержащий матрицу ассоциативных элементов пгшяти, шины данных и разрешения записи и логические блоки, каждый из которых содержит элементы И и элементы НЕ, причем 6д{ин из входов и выход каждого ассоциативного эле. мента, памяти каждой строки матрицы , --:: подключены соответственно к шине адреса и шине результата сравнения, а другие входы каждого ассоциативного элемента памяти каждого столбца подключены к информационна шинам, отличающийся тем, что, с. целью повышения надежности, накопителя, в кёикдый логический блок введен элемент памяти, причем первый входы элемента памяти и первого элемента И и вход первого элемента НЕ .подключены к шине данных, выходшервогр элемента НЕ подключен к первому входу второго элемента И, вторые и третьи входы элементов И соединены соответственно с выходами второго элемента 5 НЕ и элемента памяти, второй вход ко торого и вход второго элемента НЕ подключены к шине разрешения записи, выходы элементов И подключены к информационным шинам. кэ со DO СО Л

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ассоциативная запоминающая матрица | 1976 |

|

SU615543A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU898504A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-06-15—Публикация

1982-01-28—Подача