(50 АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ

1

Изобретение относится к запоминающим устройствам и может быть использовано в ассоциативных прЬцессорах для последовательно поразрядной обработки данных.

Известна ассоциативная матрица, содержащая ассоциативные ячейки, выполняющие операции ассоциативной записи, сравнения (опроса) и считывания til.

Недостатком этой ассс.оциативной матрицы является большое число внешних выводов.

Наиболее близким к предлагаемому является ассоциативная запоминающая матрица, содержащая ассоциативные ячейки и управляемые ключи, каждая

ячейка состоит из элемента памяти

элементов записи и сравнения, выходы элемента записи подключены к входам элемента памяти, выходы которого подключены к первым двум входам элемента сравнения, выходы элементов сравнения ячеек каждой строки МАТРИЦА

подключены к шине сравнения данной строки, первые входы элементов записи ячеек каждой строки подклочены к шине адреса данной строки, вторые и третьи входы элементов записи и вторые два .входа элементов сравне ния ячеек каждого столбца соединены попарно и подключены к соответствующим информационным шинам,данного столбца, вход и выход управляемого

10 ключа каждой строки подключены соответственно к шине сравнения и адресной шине той же строки, управляющие входы всех управляемых ключей объединены и подключены к шине раз15решения опроса 2.

Недостатками этой ассоциативной матрицы являются 2е сложность вследствие большого числа внешних выводов, низкая степень интеграции и

20 низкая технологичность ее изготовления в виде интегральной схемы.

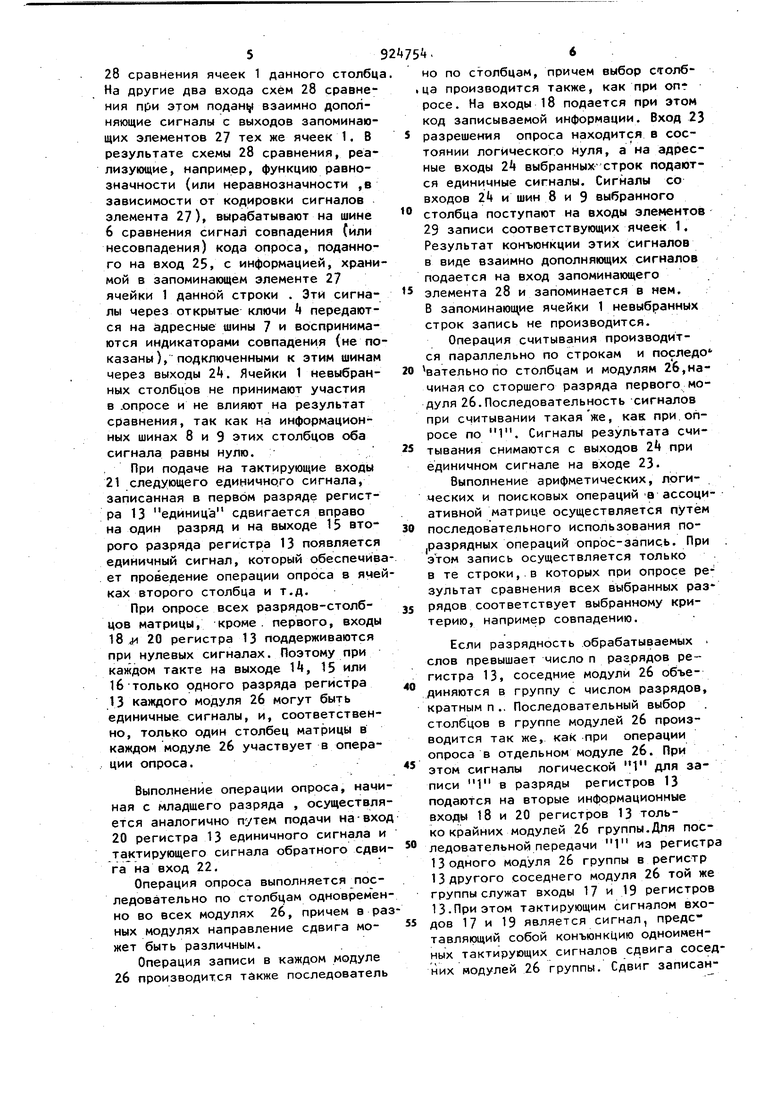

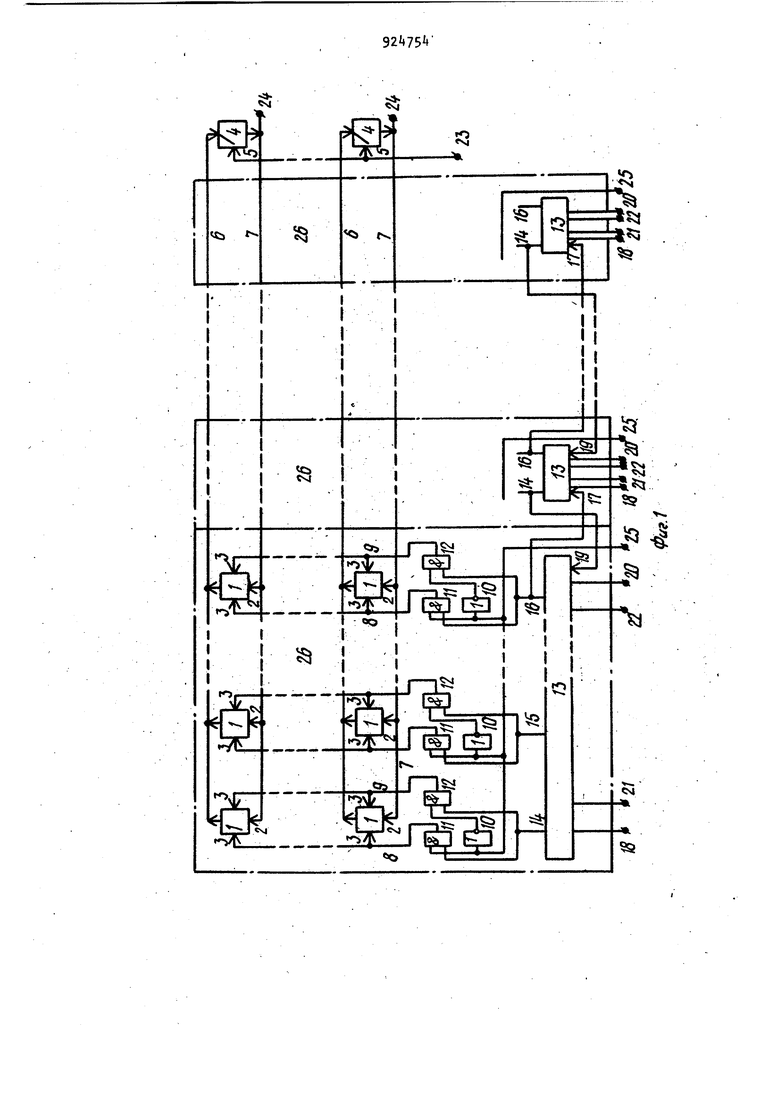

Цель изобретения - упрощение ассоциативной запоминающей матрицы, и, следовательно, повышение степени интеграции и технологичности ее из готовления. Поставленная цель достигается тем; что ассоциативная запоминающая матрица, содержащая запоминающие , ячейки и ключи, причем .адресные вхо ды и выходы запоминающих ячеекКаждой строки матрицы подключены соответственно к выходу и к входу COOTветствующего ключа, информационные входы запоминающих ячеек каждого столбца матрицы соединены соответственно с первой и второй информа ционными шинами, управляющие входы ключей объединены и являются входом разрешения опроса матрицы, она держит регистры сдвига, элементы НЕ и элементы И, причем первые входы одних из элементов И соединены с входами соответствующих элементов НЕ и являются информационными входами матрицы, первые входы других элементов И подключены соответствен но к выходам элементов НЕ, выходы одних из элементов И соединены соот ветственно с первыми, а выходы других элементов И - с вторыми информа ционными шинами соответствующих столбцов матрицы, вторые входы элементов И подключены к соответствующим выходам регистров сдвига, первый инверсный информационный вход и последний выход каждого регистра сдвига, кроме последнего, соединены соответственно с первым выходом и с первым прямым информационным входом последующего регистра сдвига, вторы прямые и инверсные информационные входы и тактирующие входы регистров сдвига являются входами матрицы. На фиг. 1 представлена функциональная схема предлагаемой матрицы; на фиг. 2 - функциональная схема з поминающей ячейки. Ассоциативная запоминающая матри ца содержит (фиг. 1) запоминающие ячейки 1 с адресными 2 и информационными 3 входами , ключи Л с управляющими входами 5, шины 6 сравнения адресные шины 7, первые 8 и вторые 9 информационные шины, элементы НЕ 10, одни 11 и другие 12 элементы И, регистры 13 сдвига реверси ного типа с числом разрядов п и с выходами 1 и 15 и 16 , гюрвыми 1 и вторыми 18 прямыми информационным входами, первыми 19 и вторыми 20 и версными информационными входами, тактирующими входами 21 (прямого сдвига) и 22 (обратного сдвига). На фиг. 1 обозначены вход 23 разрешения опроса, адресные входы и выходы 2 и информационные входы 25 матрицы. На фиг. 1 обозначен также модуль 26, в который конс,тоуктивно объединяются регистр сдвига-, подключенный к его выходам через элементы и запоминающие ячейки и соответствующие элементы НЕ. Запоминающая ячейка (фиг. 2) содержит запоминающий элемент 27, например, триггер,.схему 28 сравнения и элемент записи 29. . Предлагаемая матрица работает следующим образом. При выполнении опроса на вход 23 подается сигнал логической 1 и открываются ключи 2. На входы 25 подается сигнал.логической 1 при опросе по единице или сигнал логического О при опросе по нулю. Выбор одного разряда-столбца матрицы в каждом модуле 26 и маскирование остальных разрядов-столбцов производится с помощью регистра 13, все разряды которого с помощью, сигнала сброса предварительно устанавливаются в нулевое состояние, которому соответствуют нулевые сигналы на выходах . При опросе , начиная с первого (старшего) разряда регистра 13 на входы 18 и на входы 21 (прямого сдвига) регистра 13 подаются единичные сигналы, которые обеспечивают запись 1 в первый разряд регистра 13. На выходе И первого разряда регистра 13 при этом появляется 1, а на остальных выходах 15 и 16 сохраняются нулевые сигналы. Если на вход 20 или вход 18 регистра 13 не подан единичный сигнал, состояния выходов Й-16 всех его разрядов не изменяются, даже при наличии тактирующего сигнала сдвига на входах .21 и 22. На шинах 8 и 9 первдго столбца матрицы при опросе по 1 возникают сигналы соответственно Г и О, а при опросе по О - сигналы и 1 . На шинах 8 и 9 всех остальных маскируемых столбцов при этом присутствуют ч сигналы О и О, так как на вторых входах элементов И 11 и 12 этих столбцов нулевые сигналы. Сигналы с шин 8 и 9 выбранного столбца поступают на входы схем

28 сравнения ячеек 1 данного столбц На другие два входа схем 28 сравнения при этом подану взаимно дополняющие сигналы с выходов запоминающих элементов 27 тех же ячеек 1. В результате схемы 28 сравнения, реализующие, например, функцию равнозначности (или неравнозначности ,в зависимости от кодировки сигналов элемента 27), вырабатывают на шине 6 сравнения сигнал совпадения (или несовпадения) кода опроса, поданного на вход 25, с информацией, хранимой в запоминающем элементе 27 ячейки 1 данной строки . Эти сигналы через открытые ключи k передаются на адресные шины 7 и воспринимаются индикаторами совпадения (не показаны), подключенными к этим шинам через выходы 2. Ячейки 1 невыбранных столбцов не принимают участия в .опросе и не влияют на результат сравнения, так как на информационных шинах 8 и 9 этих столбцов оба сигнала равны нулю.

При подаче на тактирующие входы 21 следующего единичного сигнала, записанная в первом разряде регистра 13 единица сдвигается вправо на один разряд и на выходе 15 второго разряда регистра 13 появляется единичный сигнал, который обеспечивает проведение операции опроса в ячейках второго столбца и т.д.

При опросе всех разрядов-столбцов матрицы, кроме . первого, входы 18 и 20 регистра 13 поддерживаются при нулевых сигналах. Поэтому при каждом такте на выходе 1, 15 или 16ТОЛЬКО одного разряда регистра 13 каждого модуля 26 могут быть единичные сигналы, и, соответственно, только один столбец матрицы в каждом модуле 26 участвует в операции опроса.

Выполнение операции опроса, начиная с младщего разряда , осуществляется аналогично путем подачи на-вход 20 регистра 13 единичного сигнала и тактирующего сигнала обратного сдвига на вход 22.

Операция опроса выполняется последовательно по столбцам одновременно во всех модулях 2б, причем в разных модулях направление сдвига может быть различным.

Операция записи в каждом модуле 2б производится также последователь

НО по столбцам, причем выбор столбца производится также, как при onf росе. На входы 18 подается при этом код записываемой информации. Вход 23 разрешения опроса находится в состоянии логического нуля, а на адресные входы 2 выбранных строк подаются единичные сигналы. Сигналы со входов 2k и шин 8 и 9 выбранного

0 столбца поступают на входы элементов 29 записи соответствующих ячеек 1. Результат конъюнкции этих сигналов в виде взаимно дополняющих сигналов подается на вход запоминающего

5 элемента 28 и запоминается в нам. В запоминающ,ие ячейки 1 не выбранных строк запись не производится.

Операция считывания производится параллельно по строкам и последо вательно по столбцам и модулям 26,на0чиная со сторшего разряда первого модуля 26.Последовательность сигналов при считывании такаяже, как при.опросе по 1. Сигналы результата считывания снимаются с выходов 2 при

5 единичном сигнале на входе 23.

Выполнение арифметических, логических и поисковых операций в ассоциативной матрице осуществляется путём

0 последовательного использования по|разрядных операций опрос-запись. При этом запись осуществляется только в те строки, в которых при опросе результат сравнения всех выбранных разрядов соответствует выбранному кри5терию, например совпадению.

Если разрядность .обрабатываемых слов превышает число п разрядов регистра 13, соседние модули 2б объе0диняются а группу с числом разрядов, кратным п .. Последовательный выбор . столбцов в группе модулей 26 производится так же, как при операции опроса в отдельном модуле 26. При

5 этом сигналы логической 1 для записи 1 в разряды регистров 13 пoдaюtcя на вторые информационные входы 18 и 20 регистров 13 только крайних модулей 2б группы.Для последовательной передачи 1 из регистра 13 одного модуля 26 группы в регистр 13 другого соседнего модуля 2б той же группы служат входы 17 и 19 регистров 13-При этом тактирующим сигналом входов 17 и 19 является сигнал, представляющий собой конъюнкцию одноименных тактирующих сигналов сдвига соседних модулей 2б группы. Сдвиг записан79в регистрах 13 группы модулей 2б одновременно может быть только в одном направлении - от стар шего разряда к младшему или наоборот . Технико-экономическое преимущество предлагаемой ассоциативной запоми нающей матрицы заключается в меньшем, по сравнению с известным , коли честве, внешних йыводов .приходящихся на разряд матрицы , за счет чего достигается ее упрощение и повышается степень интеграции и технологичность изготовления. Формула изобретения Ассоциативная запоминающая мйтри ца , содержащая запоминающие ячейки и ключи, причем адресные входы и выходы запоминающих ячеек каждой строки матрицы подключены соответственно к выходу и к входу соответствующего ключа, информационные входы запоминающих ячеек каждого столбца матрицы соединены соответственно с первой и второй информационными шинами, управляющие входы ключей объединены и являются входом разрешения опроса матрицы, отличающаяся тем, что, с целью упрощения матрицы, она содержит регистры сдвига, элементы НЕ и элементы И, причем первые входы одних из элементов И соединены с входами соответствующих элементов НЕ и являются информационными входами матрицы, первые входы других элементов И подключены соответственно к выходам элементов НЕ, выходы одних из элементов И соединены соответственно с первыми, а выходы других элементов И - с вторыми информационными шинами соответствующих столбцов матрицы, вторые входы элементов И подключены к соответствующим выходам регистров сдвига, первый инверсный информационный вход и последний выход каждого регистра сдвига, кроме последнего, соединены соответственно с первым выходом и с первым поямым информационмым входом последущего регистра сдвига, вторые прямые и инверсные информационные входы и тактирующие входы регистров сдвига являются входами матрицы. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № , кл. G 11 С 15/00, 1978. 2.Каталог фирмы Tl.The Integrated Circuit Catalog, 1970 fпрототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативная запоминающая матрица | 1981 |

|

SU1005188A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1996 |

|

RU2107955C1 |

| СПОСОБ И АССОЦИАТИВНОЕ МАТРИЧНОЕ УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СТРОКОВЫХ ДАННЫХ | 2014 |

|

RU2569567C2 |

| СПОСОБ ПАРАЛЛЕЛЬНОГО ПОИСКА И ЗАМЕНЫ СТРОКИ И ОДНОРОДНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2012 |

|

RU2509383C2 |

| Накопитель для ассоциативного запоминающего устройства | 1982 |

|

SU1023396A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| Ассоциативное запоминающее устройство | 1989 |

|

SU1741175A1 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

| Ассоциативная запоминающая матрица | 1985 |

|

SU1275546A1 |

II

ic

l§

«fi

9

Фиг. 2

Авторы

Даты

1982-04-30—Публикация

1980-09-16—Подача