1

Изобретение относится к запоминаю щим устройствам и может быть использовано в качестве ассоциативного поля в ассоциативных процессорах.

Известно ассоциативная запоминающая матрица, содержащая элементы паМГ.ТИ, каждый из которых выполнен из триггера, подключенного к элементам сравнения, выходы которых соединены соответственно с шинами результата опроса, шины разрешения записи по строке и по столбцу, информационные шины опроса 1.

Недостатком этой матрицы являются большие аппаратурные затраты.

Наиболее близкой к предлагаемой по технической сущности является асогоииативная запоминающая матрипа, содержащая элементы памяти, каждый из Которых выполнен из триггера, подклк ченного к элементам сравнения, выходы которых соединены соответственно с шинами результата опроса, шины разрешения записи по строке и по столбцу,

информационные шины опроса, трехвходовые элементы И-НЕ, первые входы которых .соединены соответственно с информационными шинами опроса, вторые с шинами разрешения записи по сголбцу, третьи - с шинами разрешения записи по строке, а выходы элементов И-НЕ подключены к входам соответствующего триггера 2.

Наличие двух шин опроса на каждый

10 столбец усложняет матрицу, снижает уровень интеграции (количество ячеек памяти в корпусе) и надежность матрицы.

Цель изобретения - упрощение устройства.

15

Поставленная цель достигается тем, что в ассоциативную запоминающую матрицу, содержащую элементы памяти, каждый из которых выполнен из триггера и Элементов И-НЕ, причем входы и выход

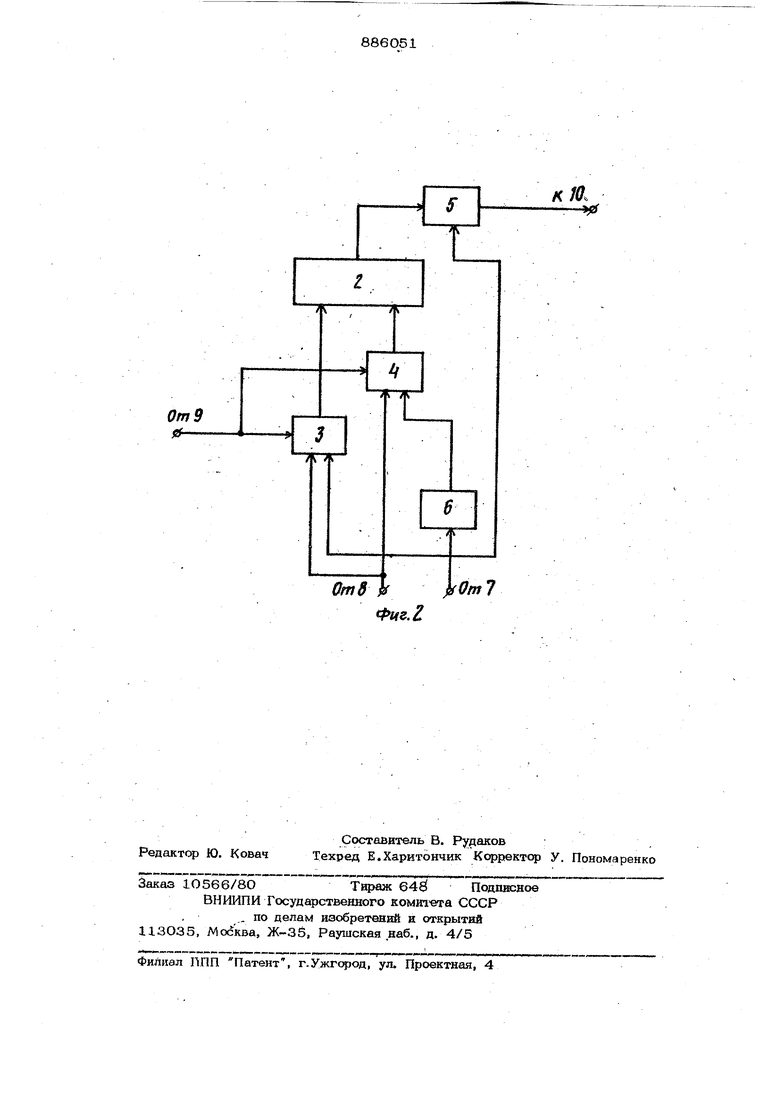

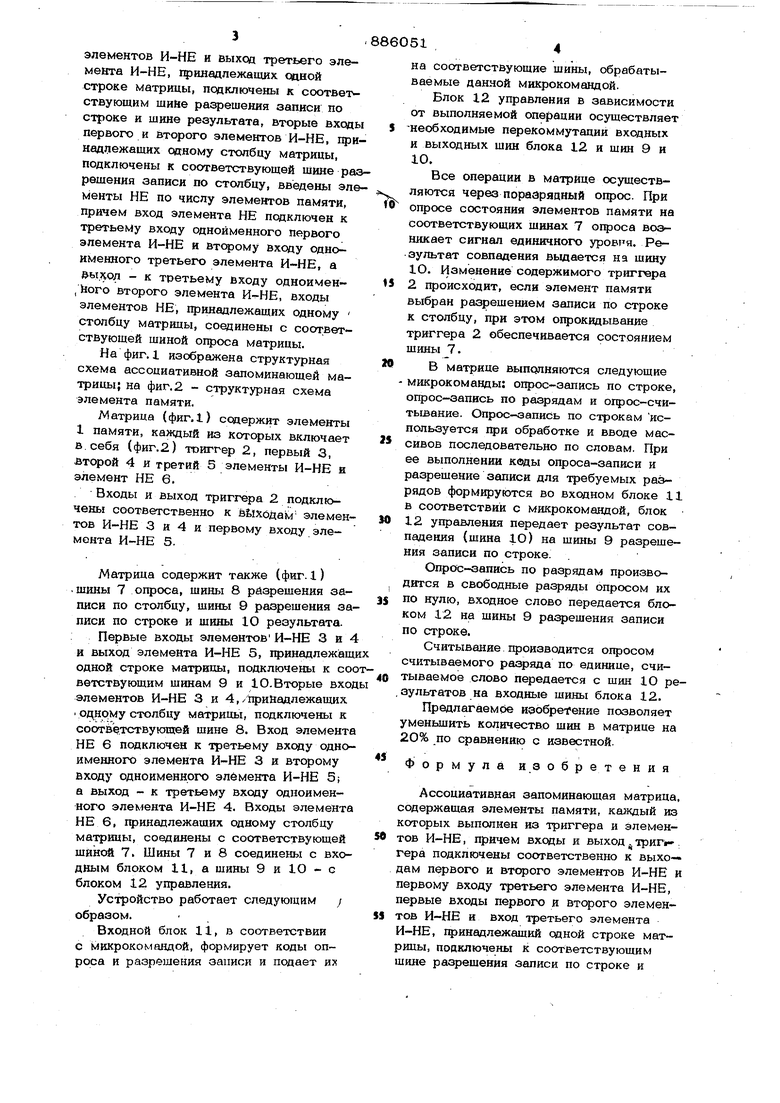

20 триггера подключены соответственно к выходам первого и второго элементов И-НЕ и первому входу третьего элемента И-НЕ, первые входы первого и второго элементов И-НЕ и выход третьего элемента И-НЕ, 15эинадлежа1цих оаной строке матрицы, подключены к соответствующим шиНе разрешения записи по строке и шине результата, вторые входы первого и второго элементов И-НЕ, при надлежащих одному столбцу матрицы, подключены к соответствующей шине раз решения записи по столбцу, введены эле менты НЕ по числу элементов памяти, причем вход элемента НЕ подключен к третьему входу одноименного первого элемента И-НЕ и входу одноименного третьего элемента И-НЕ, а эыкол - к третьему входу одноимен, horo второго элемента И-НЕ, входы элементов НЕ, принадлежащих одному столбцу матрицы, соединены с соответствующей шиной опроса матрицы. На фиг, 1 изображена структурная схема ассоциативной запоминающей матрицы; на фиг. 2 - структурная схема элемента памяти. Матрица (фиг.1) содержит элементы 1 памяти, каждый из которых включает в. себя (фиг.2) тоиггер 2, первый 3, второй 4 и третий 5 элементы И-НЕ и элемент НЕ 6. Входы и выход триггера 2 подключены соответственно к sbixoflaivf элементов И-НЕ 3 и 4 и первому входу элемента И-НЕ 5. Матрица содержит также (фиг. 1) .шины 7 опроса, шины 8 разрешения записи по столбцу, шины 9 разрешения за писи по строке и шины 10 результата. Первые входы элементов И-НЕ 3 и и выход элемента И-НЕ 5, щ инадлежаш одной строке матрицы, подключены к со ветствуюшим шинам 9 и Ю.Вторые вхо элементов И-НЕ 3 и 4,/принадлежащих одному столбцу матрицы, подключены к соотве.тствующей шине 8. Вход элемент НЕ 6 подключен к третьему входу одно именного элемента И-НЕ 3 и второму входу одноименного элемента И-НЕ 5; а выход - к третьему входу одноименного элемента И-НЕ 4. Входы элемент НЕ 6, Г5 инадлежащих одному столбцу матрицы, соединены с соответствующей шиной 7. Шины 7 и 8 соединены с вхо дным блоком 11, а шины 9 и 1О - с блоком 12 управления. Устройство работает следующим / образом. Входной блок 11, в соответствии с микрокомандой, формирует коды опроса и разрешения записи и подает их на соответствующие щины, обрабатываемые данной микрокомандой. Блок 12 управления в зависимости от выполняемой операции осуществляет необходимые перекоммутации входных и выходных щин блока 12 и шин 9 и 10. Все операции в матрице осуществляются через поразрядный опрос. При опросе состояния элементов памяти на соответствующих щинах 7 опроса возникает сигнал единичного уровня. Результат совпадения вьщается на шину 1О. Изменение содержимого триггера 2 происходит, если элемент памяти выбран разрешением записи по строке к столбцу, при этом опрокидывание триггера 2 обеспечивается состоянием шины 7. В матрице выполняются следующие микрокоманды: опрос-запись по строке, опрос-запись по разрядам и огфос-считывание. Опрос-запись по строкам используется при обработке и вводе массивов последовательно по словам. При ее выполнении кеды опроса-записи и разрешение записи для требуемых разрядов формируются во входном блоке 11 в соответствии с микрокомандой, блок 12 управления передает результат совпадения (шина 1О) на шины 9 разрешения записи по строке. Опрос-запись по разрядам производится в свободные разряды опросом их по нулю, входное слово передается блоком 12 на шины 9 разрешения записи по строке. Считывание, производится опросом считываемого разряда по единице, считываемое слово передается с шин 1О реаультатов на входные шины блока 12. Предлагаемое изобретение позволяет уменьшить количество шин в матрице на 20% по сравнению с известной. Формула изобретения Ассоциативная запоминающая матрица, содержащая элементы памяти, каждый из которых выполнен из триггера и элементов И-НЕ, причем входы и выход триг гера подключены соответственно к выходам первого и второго элементов И-НЕ и первому входу третьего элемента И-НЕ, первые входы первого и второго элементов И-НЕ и вход третьего элемента И-НЕ, 1ринадлежаший одной строке матрицы, поаключены к соответствующим шине разрешения записи по строке и 5886 шине результата, вторые входы первого и второго элементов И-НЕ, принадлежащих одному столбцу матрицы, подключены к соответствующей шине разрешения записи по столбцу, отличающаяся тем, что, с целью упрощения матрицы, она содержит элементы НЕ по числу элементов памяти, причем вход элемента НЕ подключен к третьему входу однойменного первсГго элемента И-НЕ и второму « Ьходу одноименного третьего элемента г И-НЕ, а выход - к третьему входу одно 51 именного бгорого элемента И-НЕ, входы элементов НЕ,принадлежащих одному столбцу матрицы, соединены соответствующей шиной опроса матрицы. Источники HH(} qpMaiuiH, принятые во внимание при экспертизе i. Авторское свидетельство СССР ЗЗО49О, кл, Q 11 С 11/40, 197а 2. Авторское сввдетельство СССР М 615543, кл. Q 11 С 29/ОО, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативная запоминающая матрица | 1976 |

|

SU615543A1 |

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Ассоциативная запоминающая матрица | 1981 |

|

SU1005188A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1999 |

|

RU2168216C2 |

| Накопитель для ассоциативного запоминающего устройства | 1982 |

|

SU1023396A1 |

| Ассоциативное запоминающее устройство | 1980 |

|

SU881861A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| Ассоциативный запоминающийэлЕМЕНТ | 1979 |

|

SU809376A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU924754A1 |

| Ассоциативная запоминающая матрица | 1985 |

|

SU1275546A1 |

:з)Z

;zi

zr

От 9

От8 jc

/С Ж

Фцг.1

Авторы

Даты

1981-11-30—Публикация

1979-11-29—Подача