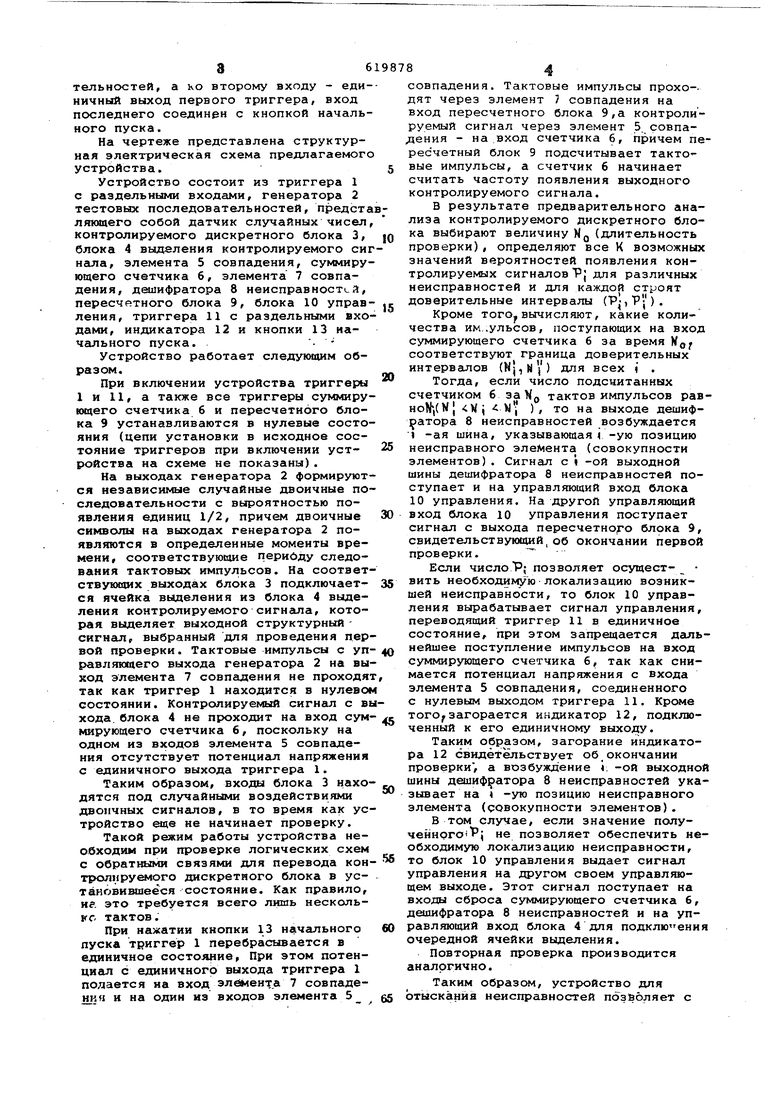

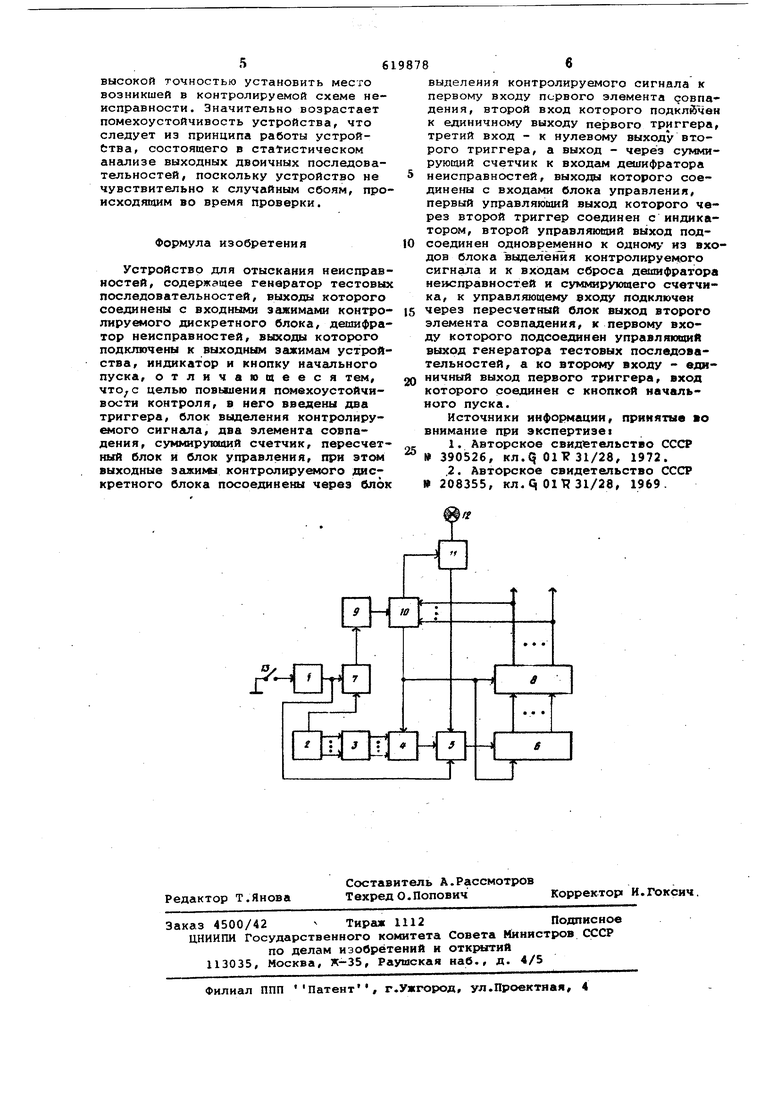

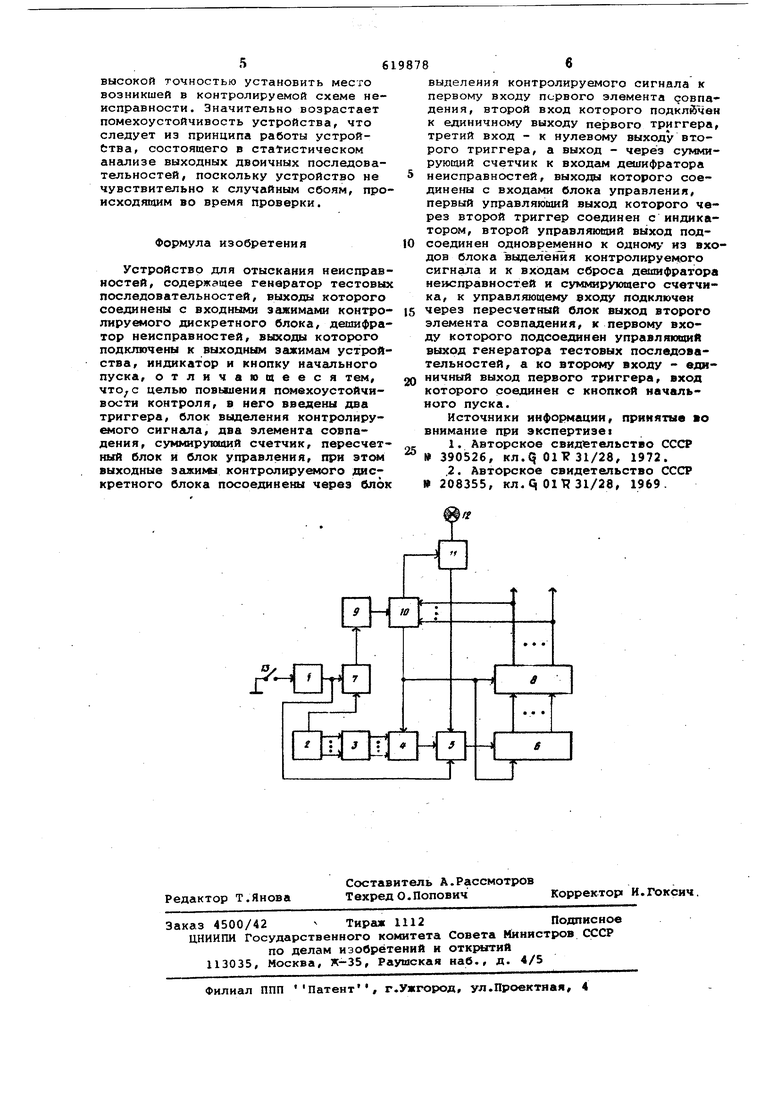

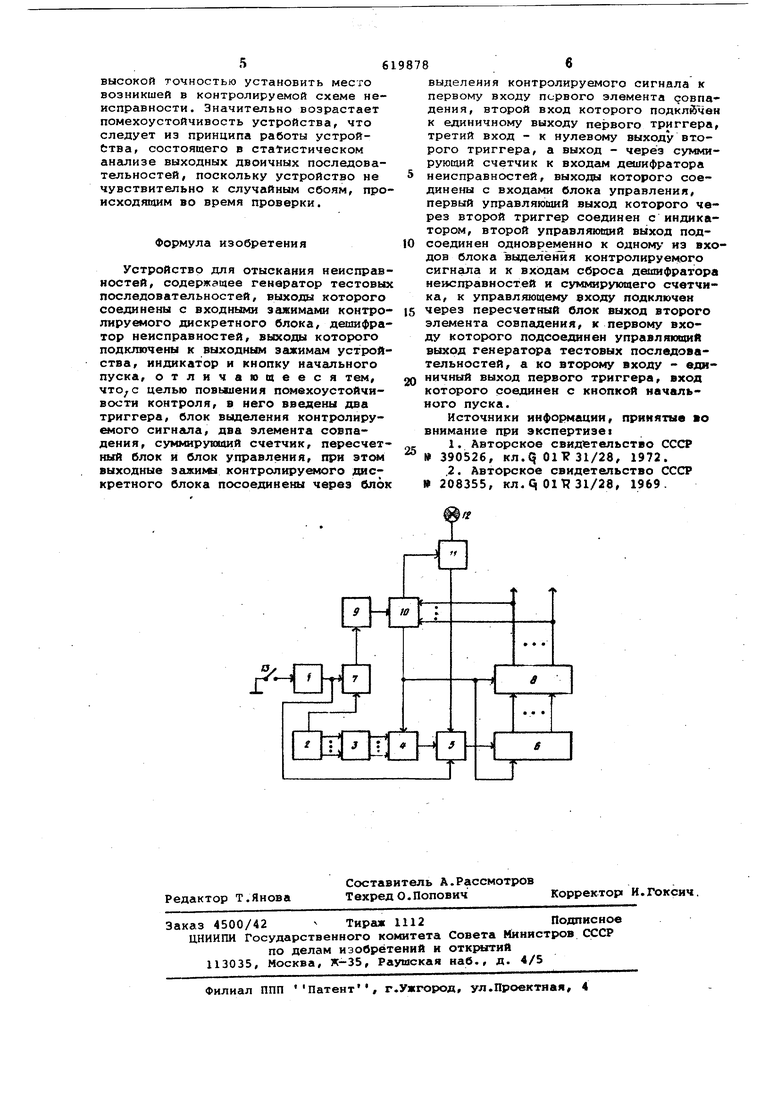

(54) УСТРОЙСТВО ДЛЯ ОТЫСКАНИЯ НЕИСПРАВНОСТЕЙ тельностей, а ко второму входу - едияичный выход первого триггера, вход последнего соединэн с кнопкой начального пуска. На чертеже представлена структурная электрическая схема предлагаемого устройства. Устройство состоит из триггера 1 с раздельными входами, генератора 2 тестовых последовательностей, предста ляющего собой датчик случайных чисел контролируемого дискретного блока 3, блока 4 выделения контролируемого сиг нала, элемента 5 совпадения, суммиру ющего счетчика 6, элемента 7 совпадения, даиифратора 8 неисправностей, пересчетного блока 9, блока 10 управ ления, триггера 11 с раздельными вхо дами, индикатора 12 и кнопки 13 начального пуска. Устройство работает следующим образом. При включении устройства триггеры 1 и 11, а также все триггеры суммиру ющего счетчика 6 и пересчетиого блока 9 устанавливаются в нулевые состо яния (цепи установки в исходное состояние триггеров при включении устройства на схеме не показаны). На выходах генератора 2 формируют ся независимые случайные двоичные по следовательности с выроятностью появления единиц 1/2, причем двоичные символы на выходах генератора 2 появляются в определенные моменты времени, соответствующее периоду следования тактовых импульсов. На соответ ствующих выходах блока 3 подключается ячейка выделения из блока 4 выделения контролируемого сигнала, которая выделяет выходной структурный сигнал, выбранный для проведения пер вой проверки. Тактовые импульсы с уп равляющего выхода генератора 2 на вы ход элемента 7 совпадения не проходя так как триггер 1 находится в нулево состоянии. КонтролируемьЛ сигнал с в хода, блока 4 не прюходит на вход сум мирующего счетчика 6, поскольку на одном из входой элемента 5 совпадения отсутствует потенциал напряжения с единичного выхода триггера 1. Таким образом, входы блока 3 нахо дятся под случайными воздействиями двоичных сигналов, в то время как ус тройство еще не начинает проверку. Такой режим работы устройства необходим при проверке логических схем с обратшлми связями для перевода кон тролнруемого дискретного блока в установившееся состояние. Как правило, ие. это требуется всего лишь несколькс тактов. При нажатии кнопки 13 начального пуска триггер 1 перебрасывается в единичное состояние, При этом потенциал с единичного выхода триггера 1 полается иа вход элемента 7 совпадения и на один из входов элемента 5 совпадения. Тактовые импульсы прохо-дят через элемент 7 совпадения на вход пересчетного блока 9,а контролируемый сигнал через элемент 5. совпадения - на вход счетчика б, причем пересчетный блок 9 подсчитывает тактовые импульсы, а счетчик 6 начинает считать частоту появления выходного контролируемого сигнала. В результате предварительного анализа контролируемого дискретного блока выбирают величину HQ (длительность проверки), определяют все К возможных значений вероятностей появления контролируемых сигналов Pj для различных неисправностей и для каждой строят доверительные интервалы (). Кроме тогОувычисляют, какие количества им..ульсов, поступающих на вход суммирующего счетчика 6 за время WQ соответствуют граница доверительных интервалов (Nj,|i() для всех t . Тогда, если число подсиитанных счетчиком 6 заХд тактов импульсов равHoN,(Nj Wj N ), то на выходе дешиф ратора 8 неисправностей возбуждается 1 -ая шина, указывающаяi -ую позицию неисправного элемента (совокупности элементов). Сигнал с I -ой выходной шины дешифратора 8 неисправностей поступает и на управляющий вход блока 10 управления. На другой управляющий вход блока 10 управления поступает сигнал с выхода пересчетно -о блока 9, свидетельствующий, об окончании первой проверки. Если числоР; позволяет осущест- вить необходимуюлокализацию возникшей неисправности, то блок 10 управления вырабатывает сигнал управления, переводящий триггер 11 в единичное состояние, при этом запрещается даль йшее поступление импульсов на вход суммирующего счетчика б, так как снимается потенциал напряжения с входа элемента 5 совпадения, соединенного с нулевым выходом триггера 11. Кроме того загорается индикатор 12, подключенный к его единичному выходу. Таким образом, загорание индикатора 12 свидетельствует об окончании проверки , а возбуждение ii -ой выходной шины дешифратора 8 неисправностей указывает на -ую позицию неисправного элемента (совокупности элементов). В том случае, если значение полученного ; не позволяет обеспечить необходимую локализацию неисправности, то блок 10 управления выдает сигнал управления на другом своем управляющем выходе. Этот сигнал поступает на входы сброса суммирующего счетчика б, дешифратора 8 неисправностей и на управляющий вход блока 4 для подклю ения очередной ячейки выделения. Повторная проверка производится ангшргично. Таким образом, устройство для отыскания неисправностей позйоляет с 56 высокой точностью установить место возникшей в контролируемой схеме неисправности. Значительно возрастает помехоустойчивость устройства, что следует из принципа работы устройства, состоящего в статистическом анализе выходных двоичных последовательностей, поскольку устройство не чувствительно к случайным сбоям, про исходящим во время проверки. Формула изобретения Устройство для отыскания неисправ ностей, содержащее генератор тестовы последовательностей, выходы которого соединены с входными зажимами контро лируемого дискретного блока, дешифра тор неисправностей, выходы которого подключены к выходным зажимам устрой ства, индикатор и кнопку начального пуска, отличающееся тем, что,с целью повышения помехоустойчивости контроля, в него введены два триггера, блок выделения контролируемого сигнгша, два элемента совпадения, суммирующий счетчик, пересчет ный блок и блок управления, при этом выходные эгикимы контролируемого дискретного блока посоединены через бло выделения контролируемого сигнала к первому входу первого элемента совпадения, второй вход которого подклйчен к единичному выходу первого триггера, третий вход - к нулевому выходу второго триггера, а выход - через суммирующий счетчик к входг1М дешифратора неисправностей, выходы которого соединены с входами блока управления, первый управляющий выход которого через второй триггер соединен с индикатором, второй управляющий выход подсоединен одновременно к одному из входов блока вьаделёния контролируемого сигнала и к входам сброса дешифратора неисправностей и суммирующего счетчика, к управляющему входу подключен через пересчетный блок выход второго элемента совпадения, к первому входу которого подсоединеи управляющий выход генератора тестовых последовательностей, а ко второму входу - единичный выход первого триггера, вход которого соединен с кнопкой начального пуска. Источники информации, принятые о внимание при экспертизе 1.Авторское свидетельство СССР 390526, кл.q OIT 31/28, 1972. 2.Авторское свидетельство СССР 208355, кл.Ч 01Т 31/28, 1969.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1984 |

|

SU1234841A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для контроля субблока логического блока | 1986 |

|

SU1327111A1 |

| Устройство для поиска неисправностей в логических узлах | 1981 |

|

SU970283A1 |

| Устройство для имитации отказов дискретной аппаратуры | 1990 |

|

SU1815642A1 |

| Устройство для нахождения кратных неисправностей в схемах цвм | 1974 |

|

SU533894A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1983 |

|

SU1168952A1 |

| Устройство для комплексной проверки автоматизированных систем ультразвукового контроля | 1987 |

|

SU1580248A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1196692A1 |

| Устройство для проверки целостности цепей | 1980 |

|

SU972420A1 |

Авторы

Даты

1978-08-15—Публикация

1976-10-25—Подача