(54) УСТРОЙСТВО для ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Устройство для коррекции ошибок внешней памяти | 1987 |

|

SU1501173A1 |

| Устройство для передачи дискретной информации | 1974 |

|

SU608148A1 |

| Устройство для сопряжения между абонентами | 1988 |

|

SU1594550A1 |

| Устройство для регистрации информации | 1978 |

|

SU857969A1 |

| Система коммутации вычислительных устройств,устройство коммутации связи и устройство сопряжения | 1984 |

|

SU1180915A1 |

| УСТРОЙСТВО МОНИТОРИНГА БЕЗОПАСНОСТИ АВТОМАТИЗИРОВАННЫХ СИСТЕМ | 2004 |

|

RU2270478C1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Система передачи сообщений | 1986 |

|

SU1356268A1 |

| Устройство для обработки статистических данных о работе аппаратуры вычислительных машин и систем | 1982 |

|

SU1086439A1 |

Изобретение относится к системам передачи информации по проводным каналам связи . Известно устройство для передачи дискретной информации, содержащее последовательно соединенные блок памяти, блок защиты от ошибок, второй выход которого подключен к входу блока памяти, и блок преобразования сигналов, а также индикатор передачи, подключенный к второму входу блока зашиты от ошибок, третий выход которого подключен к индикатору приема ij Цель изобретения - обеспечение передачи разнородных информационных сообщений . Для этого в устройство для передачи дискретной информации, содержащее последовательно соединенные блок памити, блок защиты от сяиибок, второй выход которого подключен к входу блока памяти, и блок преобразования сигналов, а также индикатор передачи подключенный к второму входу блока защиты от ошибок, третий выход которого, подключен к индикатору приема, введены последовательно соединенные счетчик числа переданных байтов, вход которого объединен со вторым входом блока памяти, первый элемент совпадения, шифратор числа переданных байтов, регистр числа байтов, второй элемент совпадения, дешифратор числа принятых байтов, счетчик числа принятых байтов и дешифратор нулевого состояния, выход которого подключен к второму входу индикатора приема, а также введены последовательно соединенные инвертор, вход которого соединен с выходом индикатора передачи, шифратор признака конца сообщения, регистр признака конца сообщения и дешифратор признака конца сообщения, выход которого подключен к второму входу -второго элемента совпадения, к третьему входу которого подключен четвертый выход блока защиты от ошибок, пятый выход которого соединен с его первым входом через третий элемент совпадения, ко второму входу которого подключен второй выход регистра числа байтов, второй вход которого подключен к второму выходу регистра признака конца сообщения, второй вход которого соединен со вторым выходом блока защиты от ошибок, при этом выход инвертора соединен со вторым входом первого элемента совпадения, а второй выход блока памяти

подключен к второму входу счетчика числа принятых байтов.

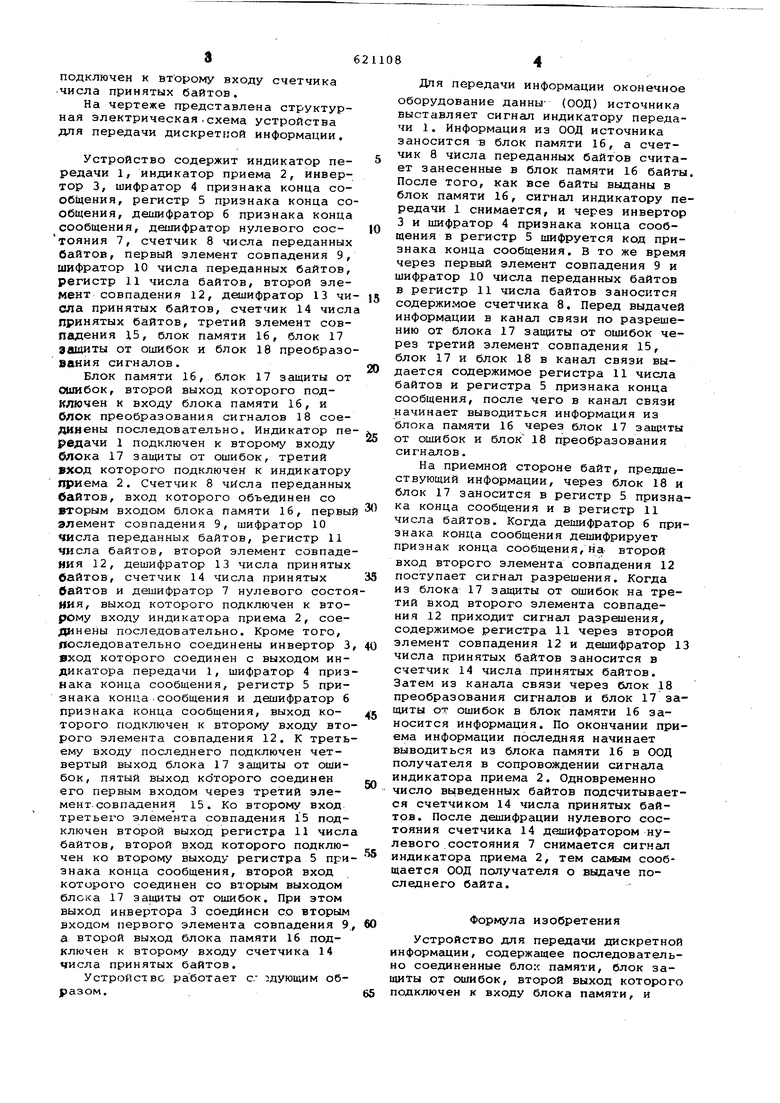

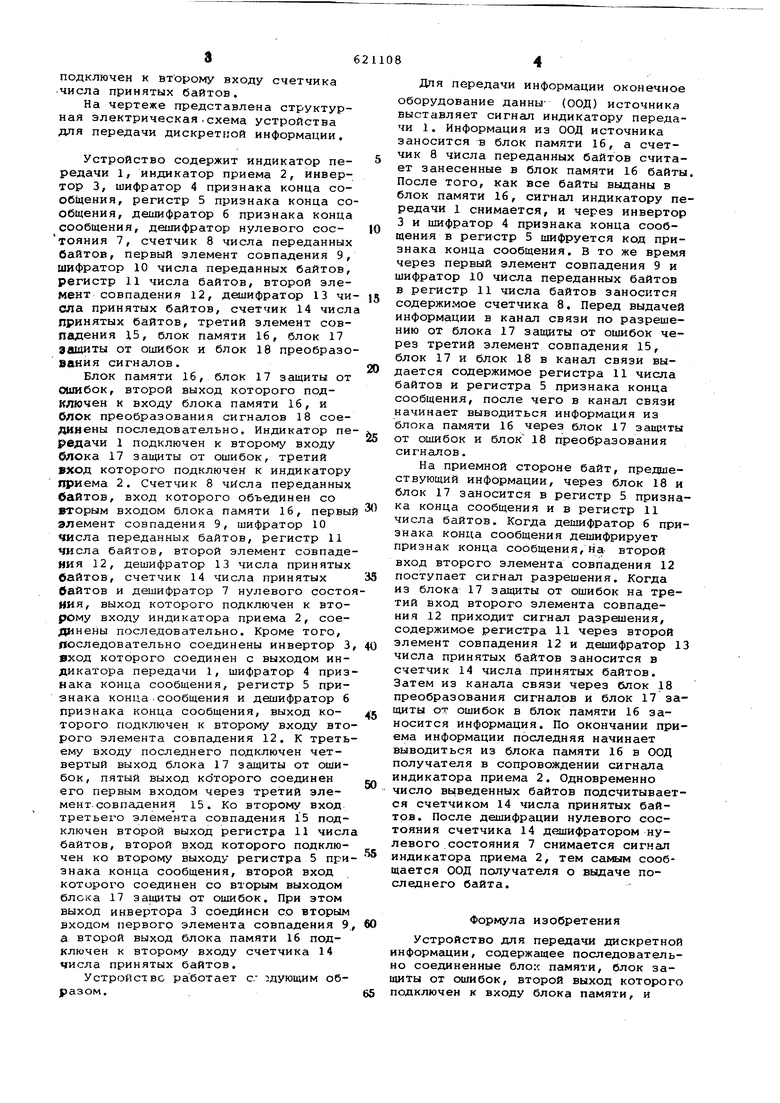

На чертеже представлена структурная электрическая.схема устройства для передачи дискретной информации.

Устройство содержит индикатор передачи 1, индикатор приема 2, инвертор 3, шифратор 4 признака конца сообщения, регистр 5 признака конца сообщения, дешифратор 6 признака конца сообщения, деишфратор нулевого соетояния 7, счетчик 8 числа переданных байтов, первый элемент совпадения 9, шифратор 10 числа переданных байтов, регистр 11 числа байтов, второй элемент совпадения 12, дешифратор 13 чи ела принятых байтов, счетчик 14 числ принятых байтов, третий элемент совпадения 15, блок памяти 16, блок 17 защиты от ошибок и блок 18 преобразования сигналов.

Блок памяти 16, блок 17 защиты от ошибок, второй выход которого подключен к входу блока памяти 16, и блок преобразования сигналов 18 соединены последовательно. Индикатор пе редачи 1 подключен к второму входу блока 17 защиты от ошибок, третий вход которого подключен к индикатору Приема 2. Счетчик 8 числа переданных байтов, вход которого объединен со вторым входом блока памяти 16, первы элемент совпадения 9, шифратор 10 числа переданных байтов, регистр 11 числа байтов, второй элемент совпадения 12, дешифратор 13 числа принятых байтов, счетчик 14 числа принятых байтов и дешифратор 7 нулевого состония, выход которого подключен к второму входу индикатора приема 2, соединены последовательно. Кроме того, последовательно соединены инвертор 3 вход которого соединен с выходом индикатора передачи 1, шифратор 4 признака конца сообщения, регистр 5 признака конца сообщения и дешифратор 6 признака конца сообщения, выход которого подключен к второму входу второго элемента совпадения 12. К третьему входу последнего подключен четвертый выход блока 17 защиты от ошибок, пятый выход которого соединен его первым входом через третий элемент, совпадения 15. Ко второму вход третьего элемента совпадения 15 подключен второй выход регистра 11 числ байтов, второй вход которого подключен ко второму выходу регистра 5 признака конца сообщения, второй вход которого соединен со вторым выходом блока 17 защиты от ошибок. При этом выход инвертора 3 соединен со вторым входом первого элемента совпадения 9 а второй выход блока памяти 16 подключен к второму входу счетчика 14 числа принятых байтов.

Устройстве работает с.- : дующим образом. .

Для передачи информации оконечное оборудование данны- (ООД) источника выставляет сигнал индикатору передачи 1. Информация из ООД источника заносится -в блок памяти 16, а счетчик 8 числа переданных байтов считает занесенные в блок памяти 16 байты После того, как все байты выданы в блок памяти 16, сигнал индикатору передачи 1 снимается, и через инвертор 3 и шифратор 4 признака конца сообщения в регистр 5 шифруется код признака конца сообщения. В то же время через первый элемент совпадения 9 и шифратор 10 числа переданных байтов в регистр 11 числа байтов заносится содержимое счетчика 8, Перед выдачей информации в канал связи по разрешению от блока 17 защиты от ошибок через третий элемент совпадения 15, блок 17 и блок 18 в Канал связи выдается содержимое регистра 11 числа байтов и регистра 5 признака конца сообщения, после чего в канал связи начинает выводиться информация из блока памяти 16 через блок 17 защиты от ошибок и блок 18 преобразования сигналов.

На приемной стороне байт, предшествующий информации, через блок 18 и блок 17 заносится в регистр 5 признака конца сообщения и в регистр 11 числа байтов. Когда дешифратор 6 признака, конца сообщения дешифрирует признак конца сообщения, на. второй вход второго элемента совпадения 12 поступает сигнал разрешения. Когда из блока 17 защиты от ошибок на третий вход второго элемента совпадения 12 приходит сигнал разрешения, содержимое регистра 11 через второй элемент совпадения 12 и дешифратор 1 числа принятых байтов заносится в счетчик 14 числа принятых байтов. Затем из канала связи через блок 18 преобразования сигналов и блок 17 защиты от ошибок в блок памяти 16 заносится информация. По окончании приема информации последняя начинает выводиться из блока памяти 16 в ООД получателя в сопровождении сигнала индикатора приема 2. Одновременно число выведенных байтов подсчитывается счетчиком 14 числа принятых байтов. После дешифрации нулевого состояния счетчика 14 дешифратором нулевого состояния 7 снимается сигнал индикатора приема 2, тем самым сообщается ООД получателя о выдаче последнего байта.

Формула изобретения

Устройство для передачи дискретной информации, содержащее последовательно соединенные блох памяти, блок защиты от ошибок, второй выход которого подключен к входу блока памяти, и S блок преобразования сигналов, а такж индикатор передачи, подключенный к второму входу блока защиты от ошибок третий выход которого подключен к ин дикатору приема, отличающе с я тем, что, с целью обеспечения передачи разнородных информационных сообщений, введены последовательно соединенные счетчик числа переданных байтов, вход которого объединен со вторым входом блока памяти, первый элемент совпадения, шифратор числа переданных байтов, регистр числа байтов, второй элемент совпгщения, дешифратор числа принятых байтов, счетчик числа принятых байтов и детаифратор нулевого состояния, выход которого подключен к второму входу индикатора приема, а также введены последовательно соединенные инвертор, вход которого соединен с выходом индикатора.. передачи, шифратор признака конца сообщения, регистр признака конца сообщения и даиифратор признака конца 8 сообщения, выход которого подключен к второму входу второго элеме; та совпадения, к третьему входу которого подключен четвертый выход блока защиты от ошибок, пятый выход которого соединен с его первым входом через третий элемент совпадения, ко второму входу которого подключен второй выход регистра числа байтов, второй вход которого подключен к второму выходу регистра признака конца сообщения, второй вход которого соединен со вторым выходом блока защиты от ошибок, при этом выход инвертора соединен со вторым входом первого элемента совпадения, а второй выход блока памяти подключен к второму входу счетчика числа принятых байтов. Источники информации, принятые во внимание при экспертизе: 1. Копничев Л.Н. и др. Телеграфные аппараты и аппаратура передачи данных, М., Связь , 1975, с.353-381,

Авторы

Даты

1978-08-25—Публикация

1976-07-12—Подача