1

Изобретение относится к области запоминающих устройств.

Известны устройства для контроля блоков памяти 1, 2.

Одно из известных устройств содержит преобразователь, который состоит из коммутатора и преобразователя параллельного кода в последовательный, счетчик контрольного кода, счетчик адресов, блок останова по заданному адресу, блок останова по контрольному коду, блок управления, выходной регистр параллельного действия и схему сравнения 1. Это устройство громоздко и в нем отсутствует контроль взаимного влияния информании, записанной в соседних ячейках элементов памяти.

Из известных устройств наиболее близким к изобретению техническим решением является устройство для контроля блоков оперативной памяти, содержащее блок контроля адреса, входы которого подключены к одним выходам устройства и выходам регистра адреса, блок сравнения, одни входы которого соединены с выходами регистра числа и другими выходами устройства, другие входы - со входами устройства, а выход - с первым входом блока пуска-останова, и блок управления 2.

Недостатком этого устройства является его сложность, что требует для его реализации больщого количества элементов и. вносит дополнительную вероятность отказа самого устройства контроля. Для контроля больших объемов памяти устройство требует длительного времени проверки.

Целью изобретения является упрощение и повышение быстродействия устройства.

Поставленная цель достигается тем, что устройство содержит блок формирования

сигнала «конец контроля и блок формирования сигнала «реверс, первые входы которых подключены к выходу блока контроля адреса, второй вход блока формирования сигнала «реверс соединен с одним из

выходом блока управления, а выход - со вторым входом блока формирования сигнала «конец контроля и одним из входов регистра числа, который выполнен в виде реверсивного двоичного счетчика, выход блока формирования сигнала «конец контроля подключен ко второму входу блока пускаостанова.

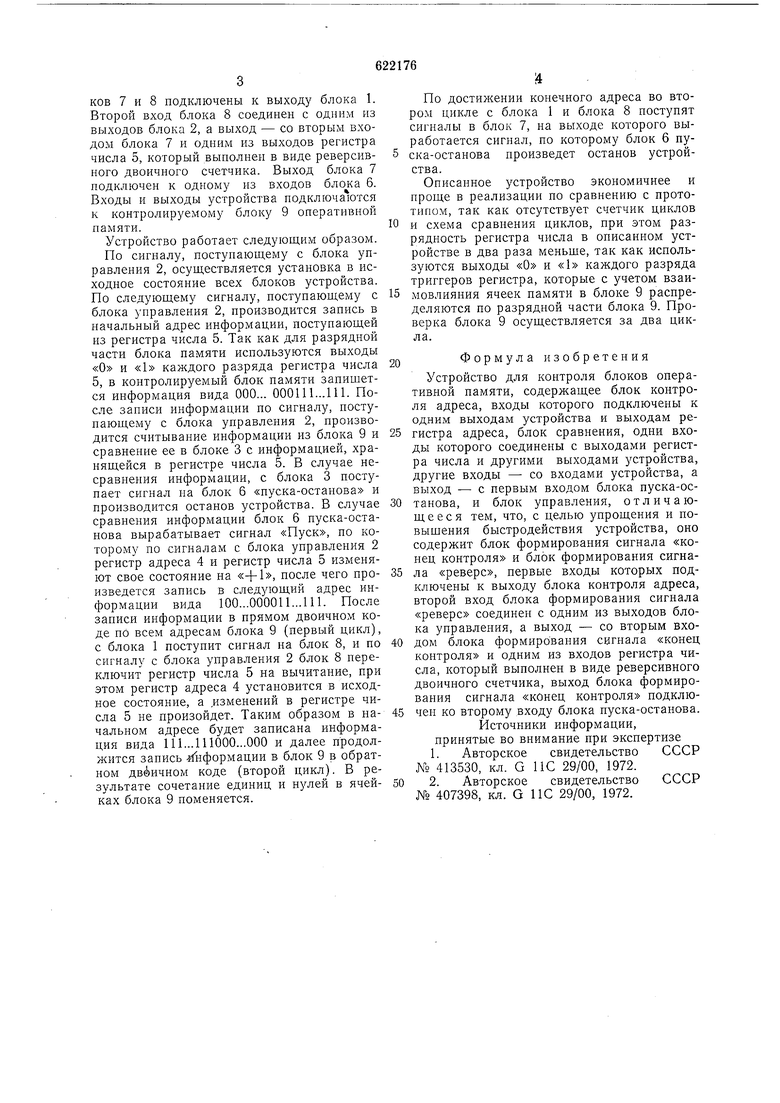

На чертеже изображена блок-схема устройства.

Устройство содержит блок 1 контроля адреса, блок управления 2, блок 3 сравнения, регистр адреса 4, регистр числа 5, блок 6 пуска-останова, блок 7 формирования сигнала «конец контроля, блок 8 формирования сигнала «реверс. Первые входы блоков 7 и 8 подключены к выходу блока 1. Второй вход блока 8 соединен с одним из выходов блока 2, а выход - со вторым входом блока 7 н одним из выходов регистра числа 5, который выполнен в виде реверсивного двоичного счетчика. Выход блока 7 подключен к одному из входов блока 6. Входы и выходы устройства гюдключа отся к контролируемому блоку 9 онеративной памяти.

Устройство работает следующим образом.

По сигналу, ностуиающему с блока управления 2, осуществляется установка в исходное состояние всех блоков устройства. По следующему сигналу, ноступающему с блока управления 2, производится запись в начальный адрес информации, поступающей из регистра числа 5. Так как для разрядной части блока памяти используются выходы «О и «1 каждого разряда регистра числа 5, в контролируемый блок памяти запишется информация вида 000... 000111...111. После записи информации по сигналу, поступающему с блока управления 2, производится считывание информации из блока 9 и сравнение ее в блоке 3 с информацией, хранящейся в регистре числа 5. В случае несравнения информации, с блока 3 поступает сигнал на блок 6 «пуска-остапова и производится останов устройства. В случае сравнения информации блок 6 пуска-остапова вырабатывает сигнал «Пуск, по которому по сигналам с блока управления 2 регистр адреса 4 и регистр числа 5 изменяют свое состояние на «+Ь, после чего произведется запись в следующий адрес информации вида 100...000011...111. После записи информации в прямом двоичном коде по всем адресам блока 9 {первый цикл), с блока 1 поступит сигнал на блок 8, и по сигналу с блока управления 2 блок 8 переключит регистр числа 5 на вычитание, при этом регистр адреса 4 установится в исходное состояние, а изменений в регистре числа 5 не произойдет. Таким образом в начальном адресе будет записана информация вида 111... 111000...000 и далее продолжится занись йнформации в блок 9 в обратном дв(1ичном коде (второй цикл). В результате сочетание единиц и нулей в ячейках блока 9 поменяется.

По достижении конечного адреса во второ.м цикле с блока 1 и блока 8 поступят сигналы в блок 7, на выходе которого выработается сигнал, по которому блок 6 пуска-останова произведет останов устройства.

Описанное устройство экономичнее и проще в реализации но сравнению с прототипом, так как отсутствует счетчик циклов

и схема сравнения циклов, при этом разрядность регистра числа в описанном устройстве в два раза меньше, так как используются выходы «О и «1 каждого разряда триггеров регистра, которые с учетом взаимовлияния ячеек памяти в блоке 9 распределяются по разрядпой части блока 9. Проверка блока 9 осуществляется за два цикла.

Формула изобретения

Устройство для контроля блоков оперативной памяти, содержащее блок контроля адреса, входы которого подключены к одним выходам устройства и выходам регистра адреса, блок сравнения, одни входы которого соединены с выходами регистра числа и другими выходами устройства, другие входы - со входами устройства, а выход - с первым входом блока пуска-останова, и блок управления, отличающееся тем, что, с целью упрощения и повышения быстродействия устройства, оно содержит блок формирования сигнала «конец контроля н блок формирования сигнала «реверс, первые входы которых подключепы к выходу блока контроля адреса, второй вход блока формирования сигнала «реверс соединен с одним из выходов блока управления, а выход - со вторым входом блока формирования сигнала «конец коптроля и одним из входов регистра числа, который выполнен в виде реверсивного двоичного счетчика, выход блока формирования сигнала «конец контроля подключен ко второму входу блока нуска-останова.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 413530, кл. G ПС 29/00, 1972.

2. Авторское свидетельство СССР № 407398, кл. G ПС 29/00, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля схем сравнения | 1984 |

|

SU1228107A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство программного адресования транспортного средства | 1983 |

|

SU1113337A1 |

| Устройство для контроля памяти | 1979 |

|

SU783855A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1104515A1 |

| Многоканальное устройство для формирования последовательностей импульсов переменной длительности | 1979 |

|

SU788358A1 |

| Устройство для приема и передачи информации | 1988 |

|

SU1536422A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОВЕДЕНИЯ ПОЛЬЗОВАТЕЛЯ | 2018 |

|

RU2675896C1 |

| Устройство для контроля накопителя | 1973 |

|

SU470867A1 |

| Устройство для задания программы | 1979 |

|

SU862118A1 |

Авторы

Даты

1978-08-30—Публикация

1977-03-01—Подача