записи счетчика, нулевой выход пярвого триггера - с входом останова блока формирования микроопераций и входом запрета блока сравнения и входом останова блока синхронизации, третий выход которого соединен с входом разрешения блока сравнения, выход блока сравнения - с первыми входами второго и третьего элемен- , тон КПИ, вторые входы которых соединены соответственно с выходами разрешения записи и начала ожидания блока формирования микроопераций, выход второго элемента ИЛИ через второй элемент задержки соединен с входом первого блока элементов И, выход третьего элемента ИЛИ через третий элемент задержки - с единичным входом первого триггера, единичный выход первого триггера - с вторыми входами, третьего блока элементов И, с вторым входом первого элемента И, с входами разрешения блока контроля и блока синхронизации, вход пуска которого является входом пуска устройства, выход блока контроля подключен к первому входу четвертого элемента ИЛИ, второй вход которого соединен с выходом конца микропрограммы блока формирования микроопераций, выход четвертого элемента ИЛИ соединен с входом останова блока синхронизации, выход конца участка блока формирования микроопераций подключен

к третьему входу первого .utnw.frro if, вь1ход которого соединен f; пхолом пятого элемента ИПИ, второй тт третий входы пятого элемента ИЛИ соединены с входами пуска и конца ожидания устройства, выход пятого элемента ИЛИ соединен с нулевыми входами первого и второго триггеров, единичный вход второго триггера соединен с выходом начала ожидания блока формирования микроопераций.

2. Устройство по п. 1, о т л и чающееся тем, что блок формирования микроопераций содержит четыре элемента И и один элемент ИЛИ причем вход останова блока соединен с первыми входами первого, второго, третьего и четвертого элементов И, входы блока конца микропрограммы, заключения цикла, микроопераций и конец участка соединены с вторыми входами соответственно первого, второго, третьего элементов И и первым входом элемента ИЛИ, вход начала ожидания блока соединен с вторым 1 входами четвертого элемента И и элемента ИЛИ, выходы первого, второго, третьего, четвертого элементов И и элемента ИЛИ являются соответственно вькодами конца микропрограммы, заключения цикла, микроопераций, начала ожидания и конца микропрограммы блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

| Микропрограммное устройство управ-лЕНия C КОНТРОлЕМ | 1979 |

|

SU842813A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Устройство для контроля и управления технологическими процессами | 1984 |

|

SU1193641A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100625A1 |

| Программный управляющий модуль с контролем | 1990 |

|

SU1758634A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

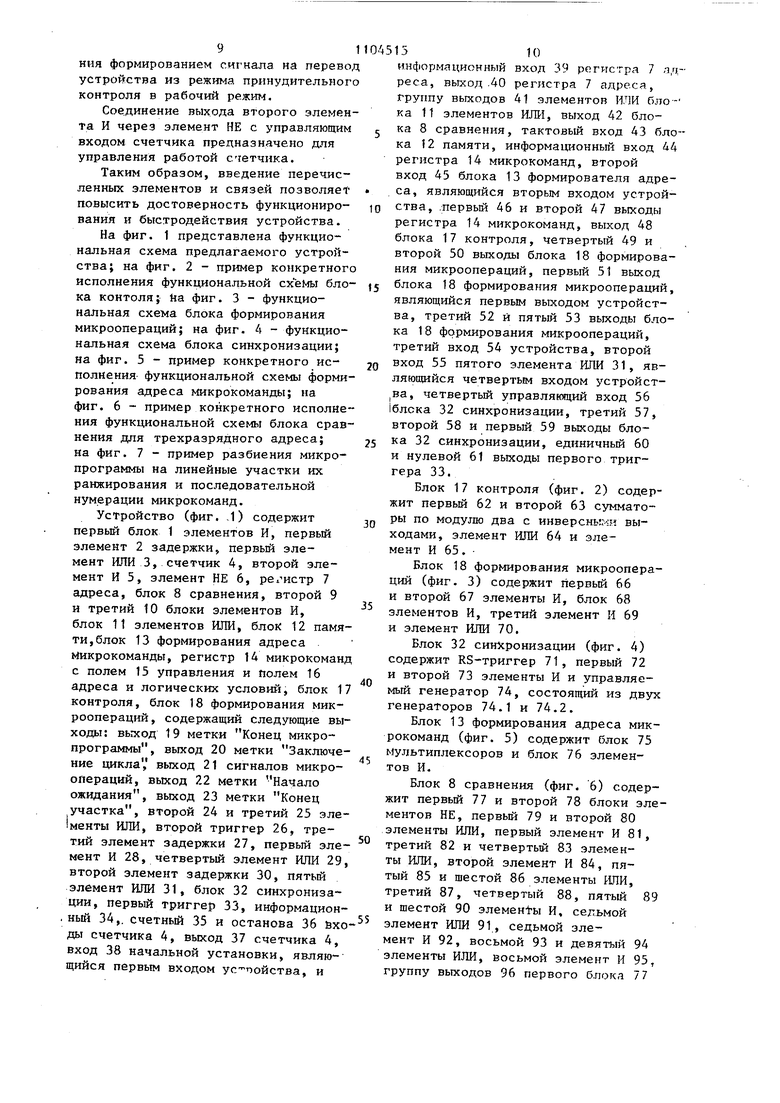

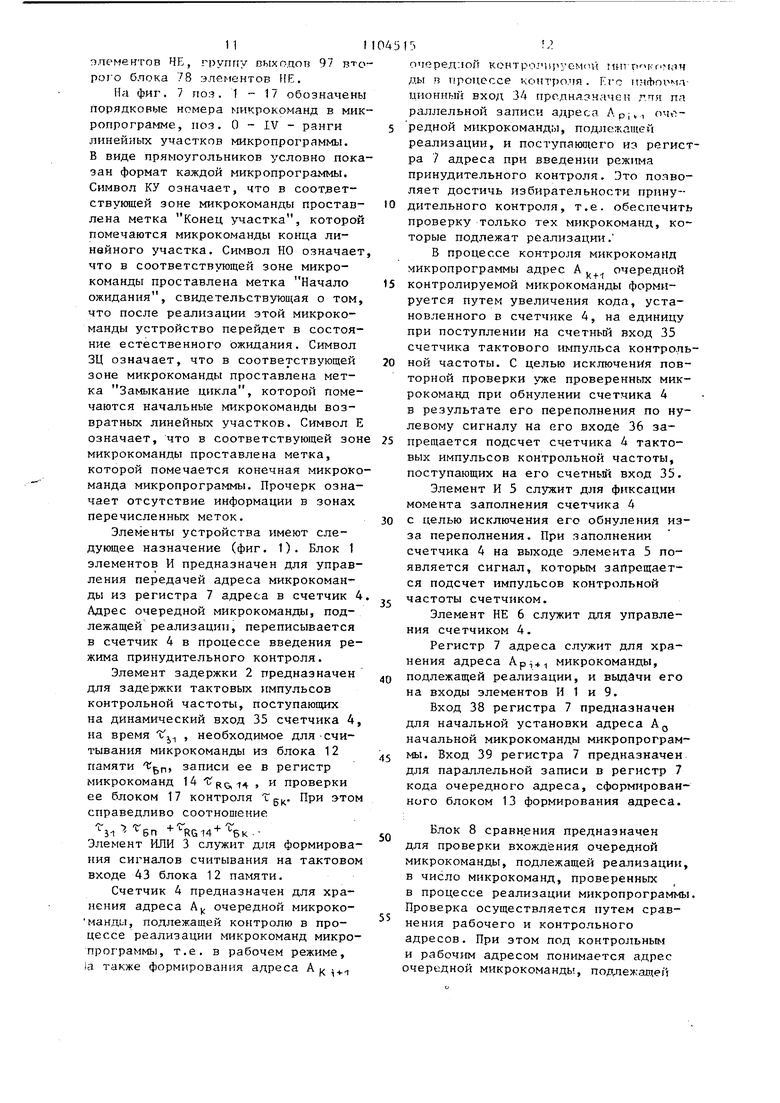

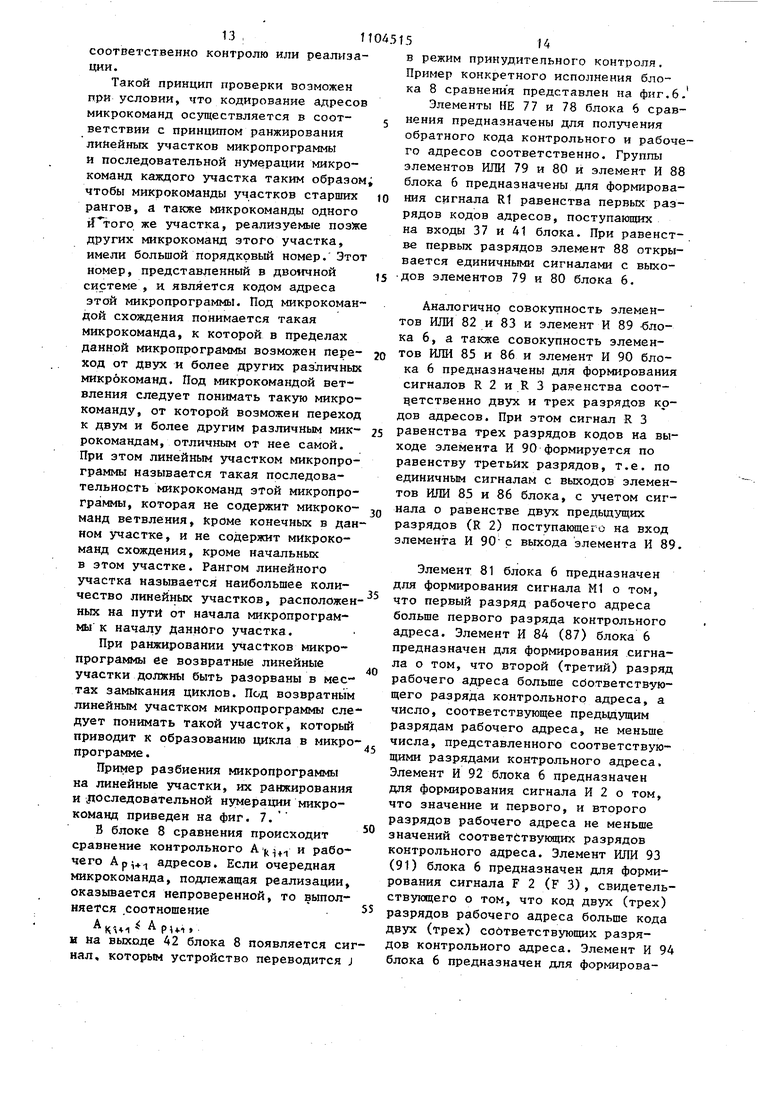

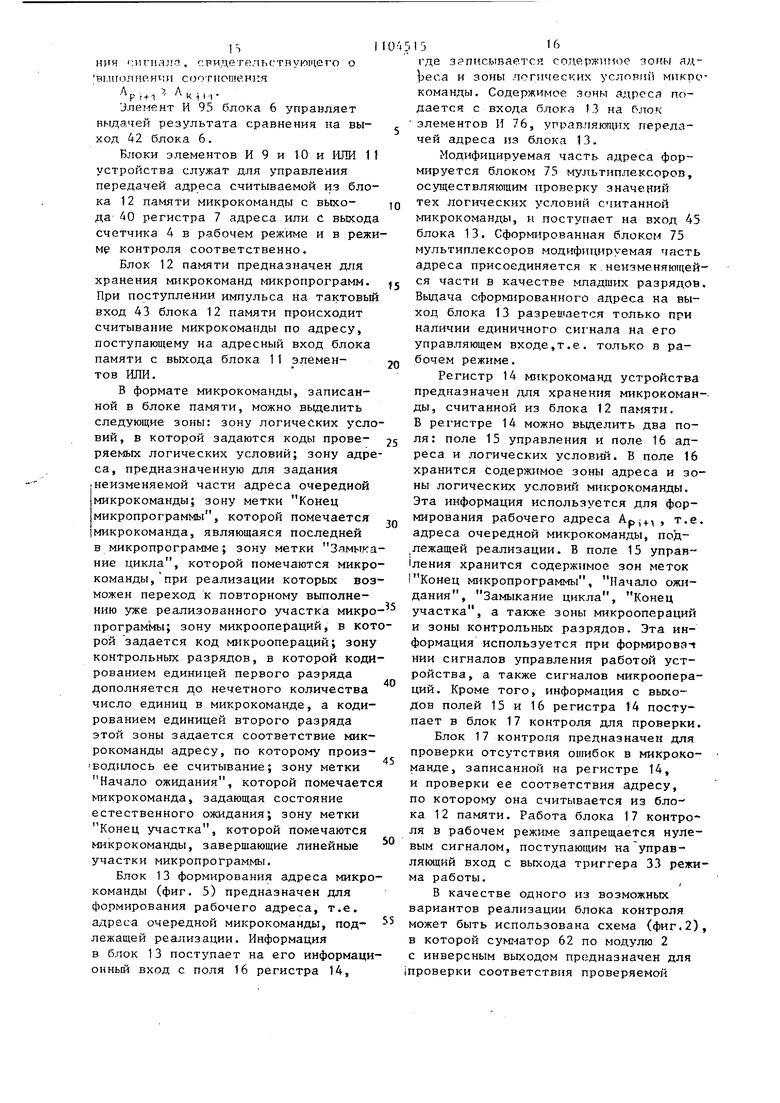

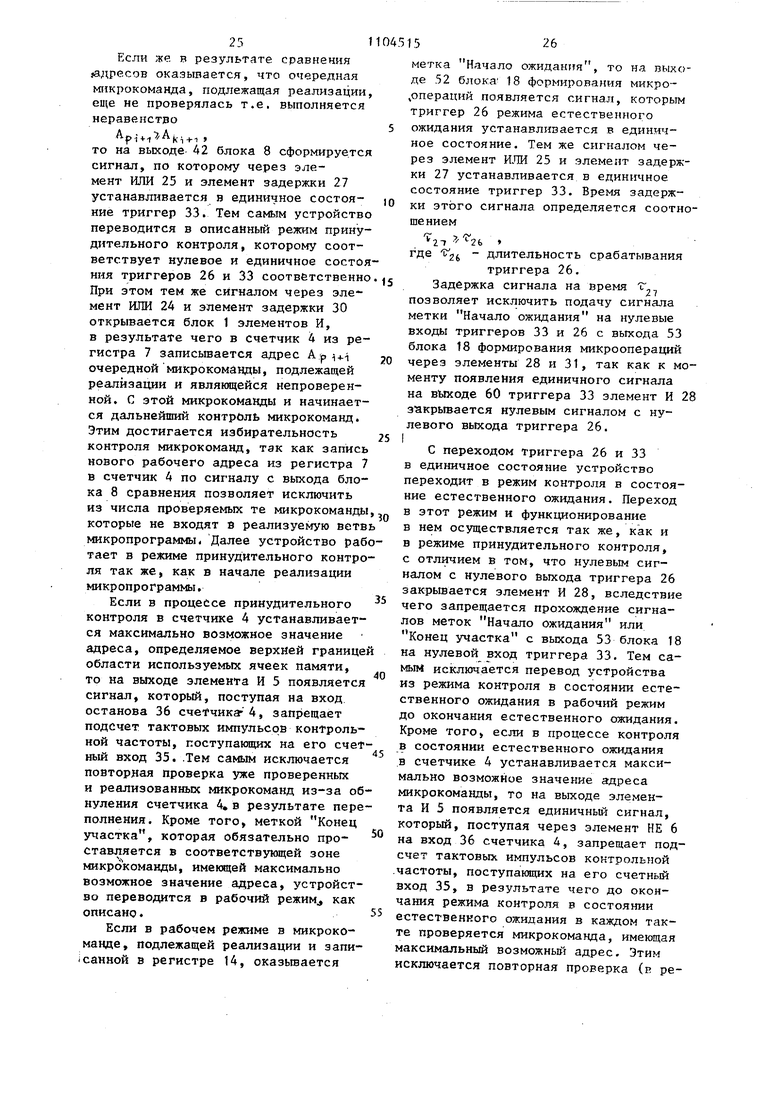

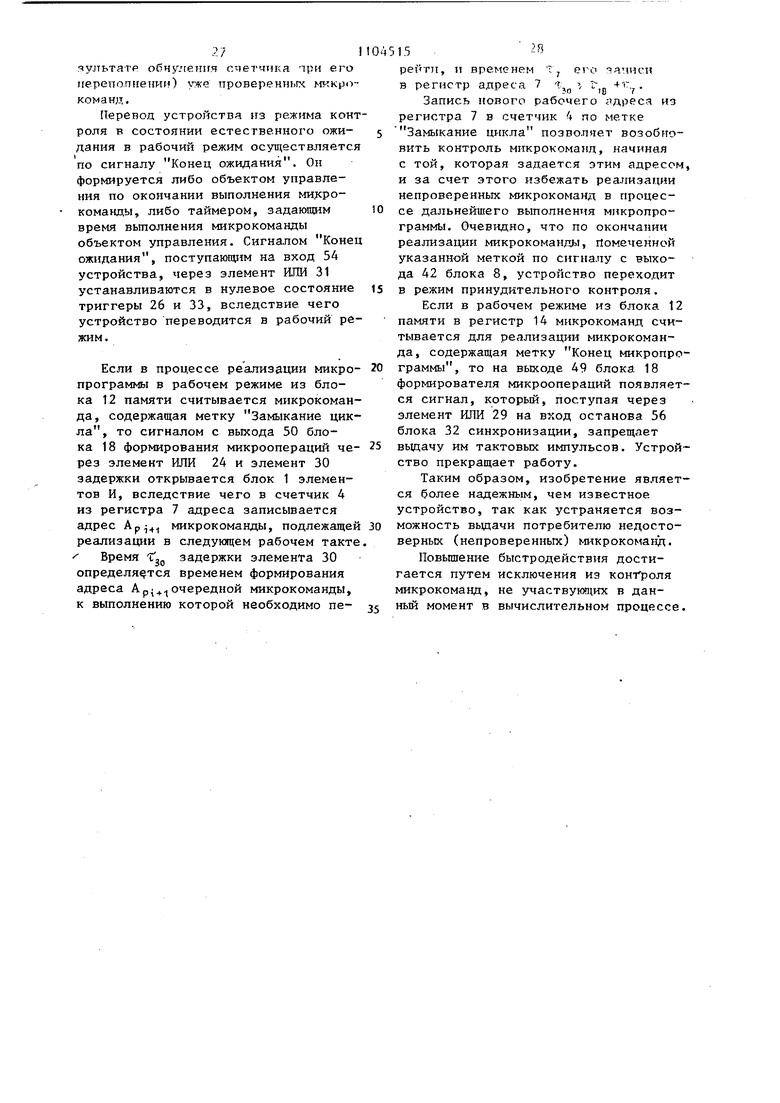

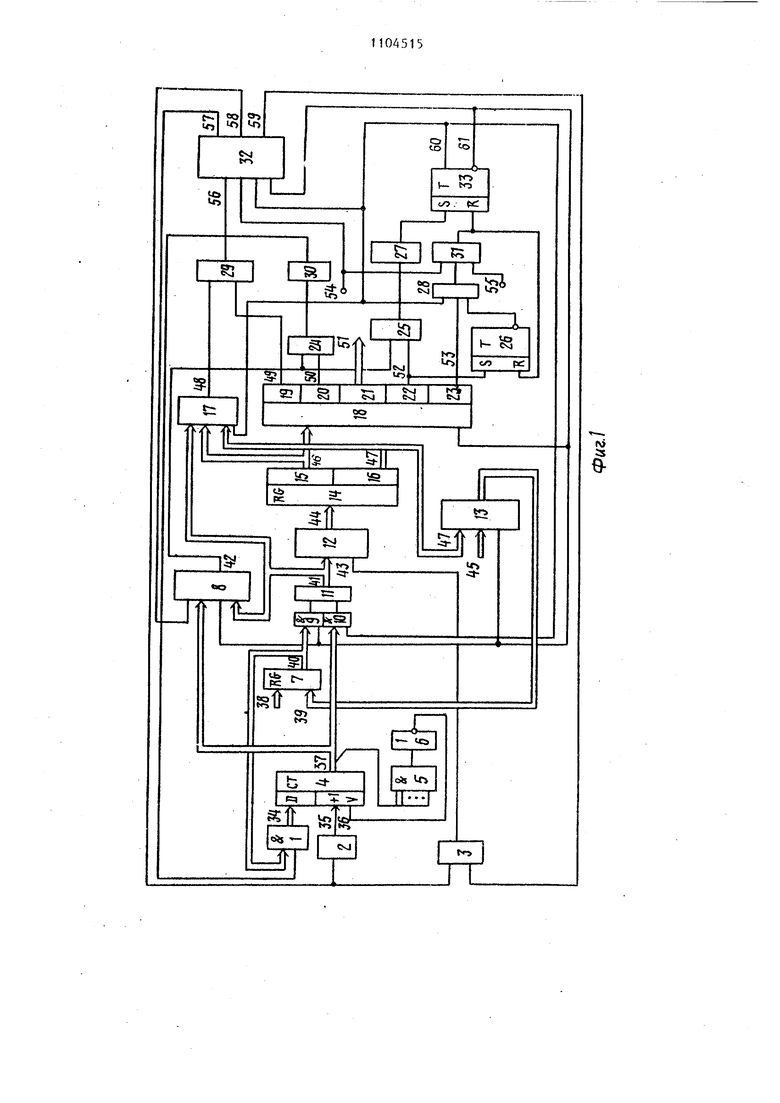

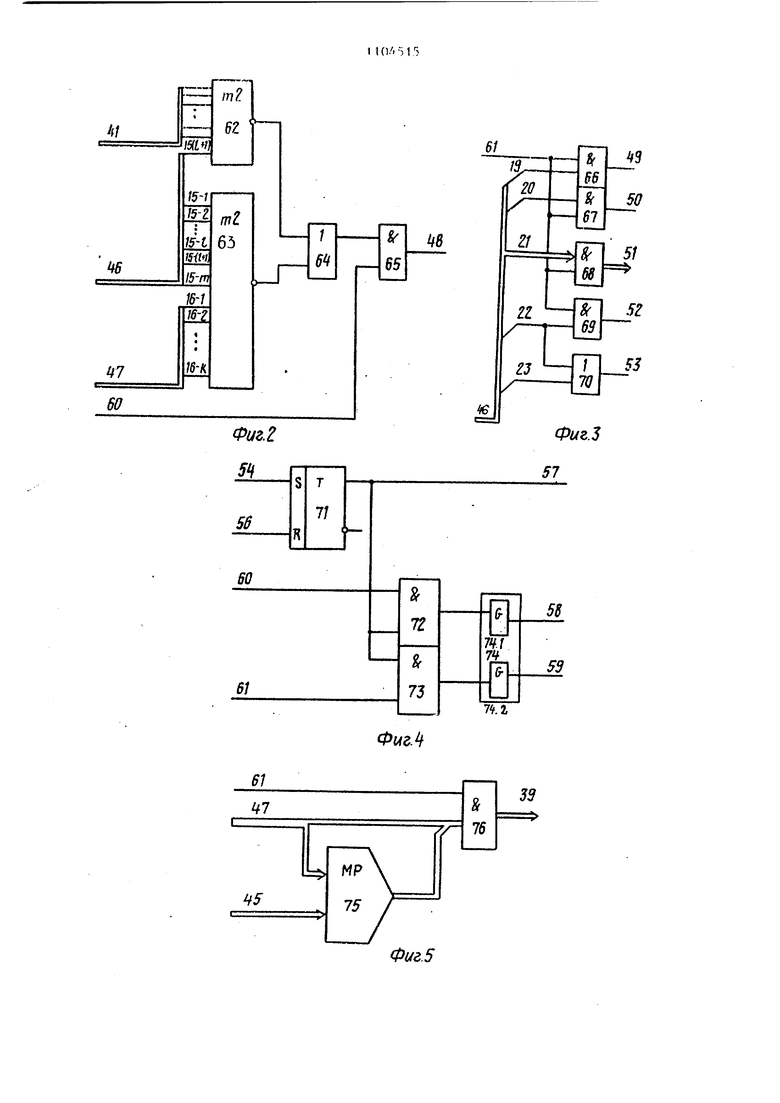

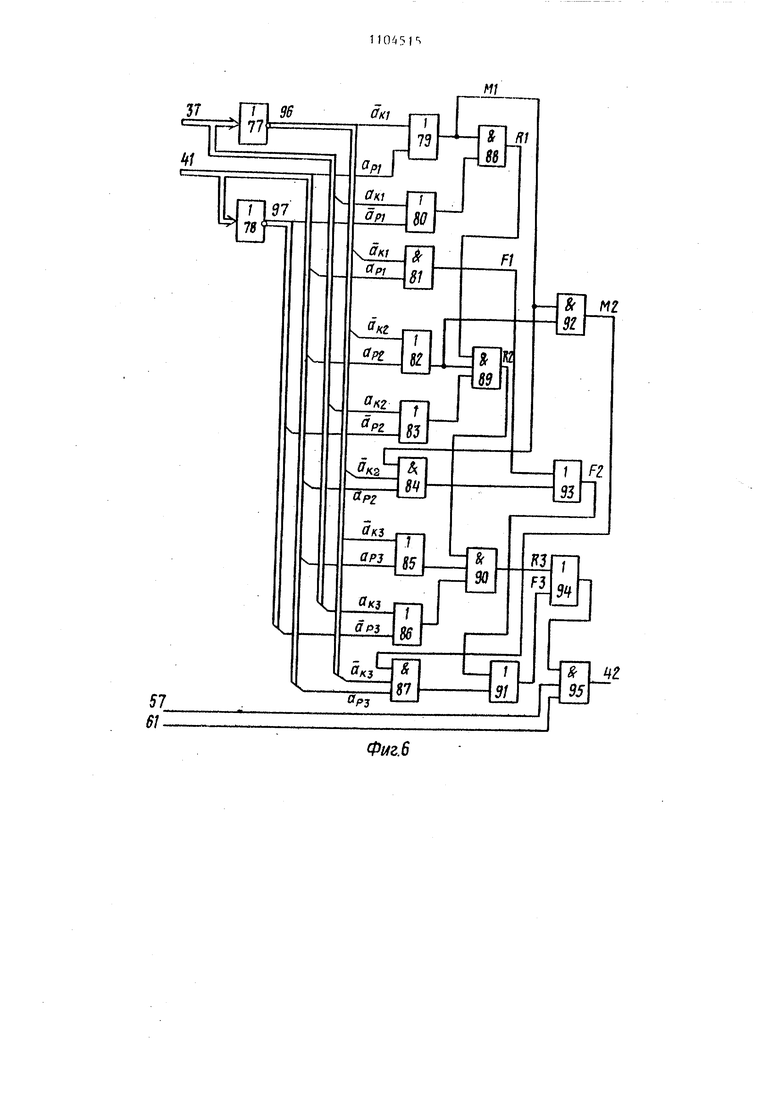

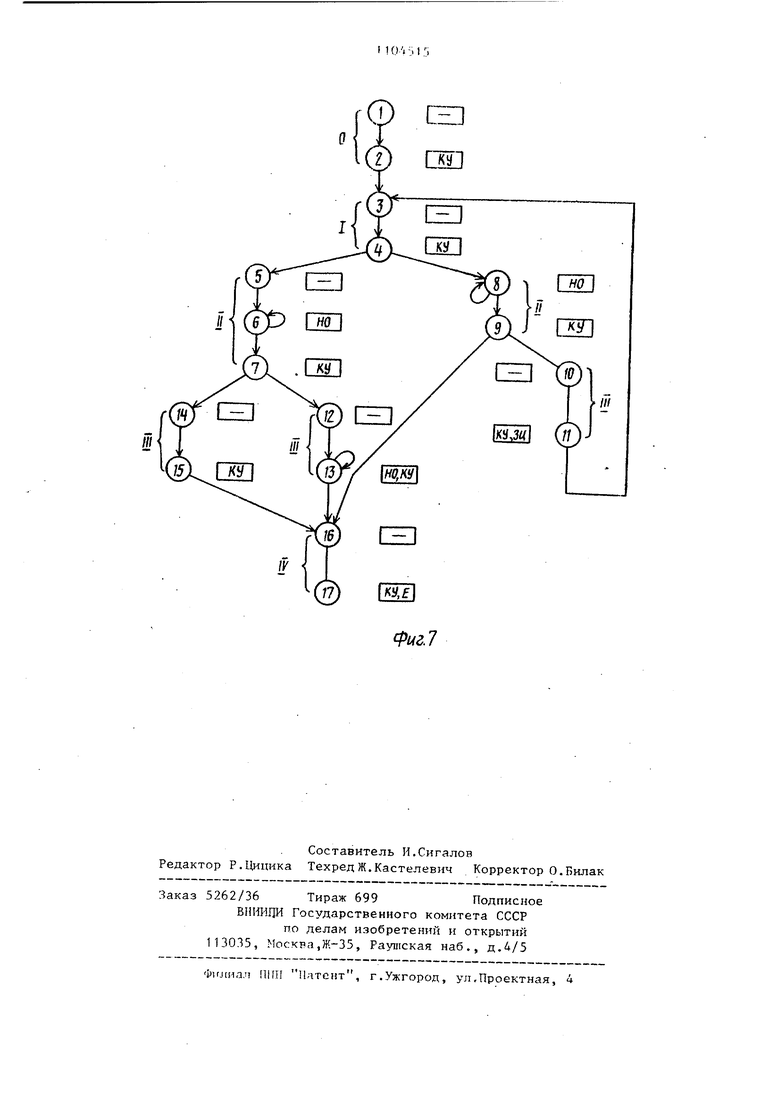

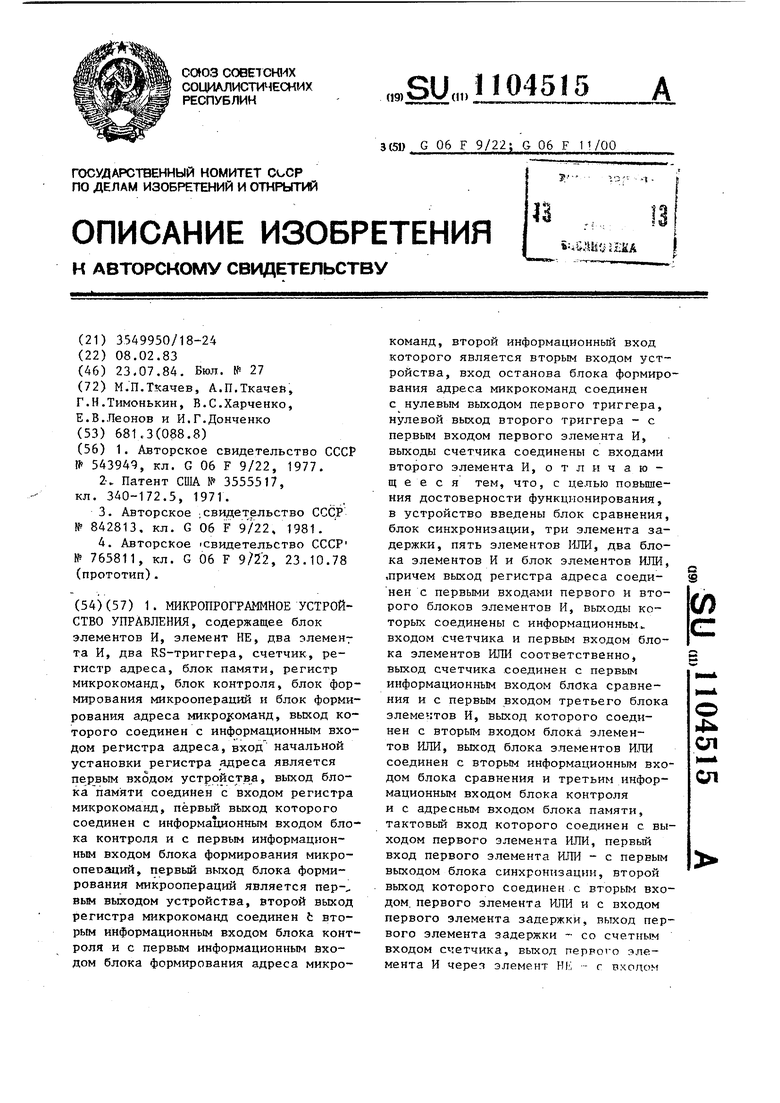

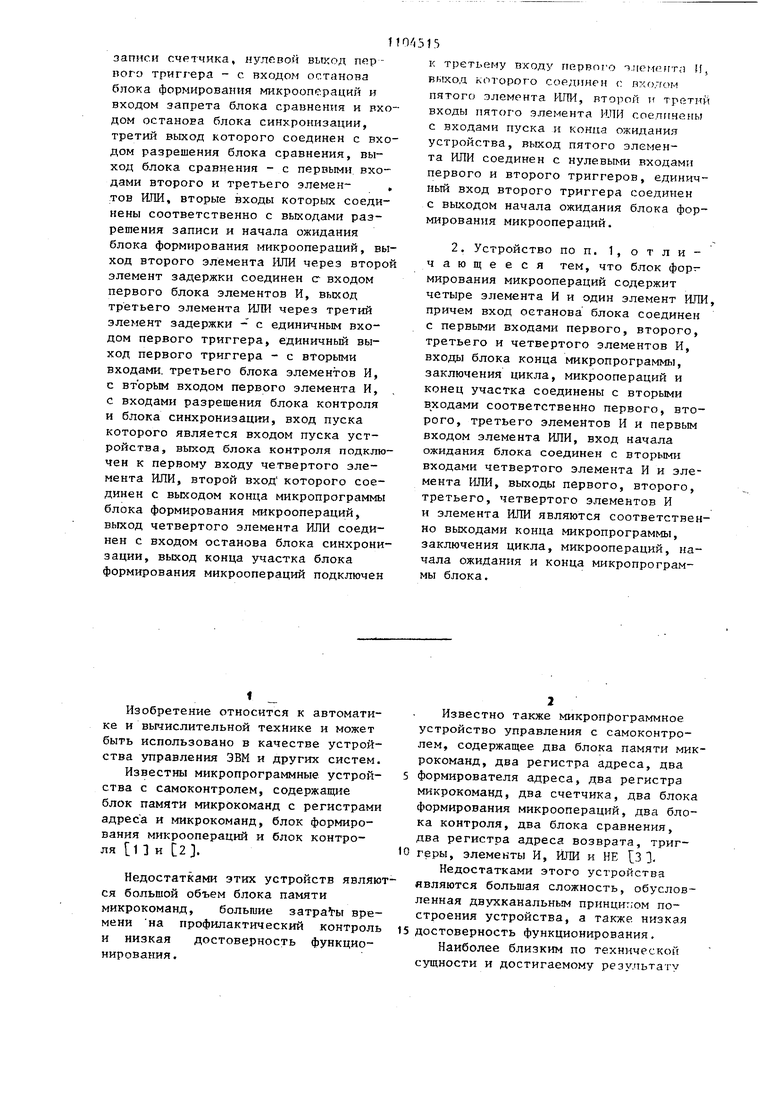

1. МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок элементов И, элемент НЕ, два элемент та И, два RS-триггера, счетчик, регистр адреса, блок памяти, регистр микрокоманд, блок контроля, блок формирования микроопераций и блок формирования адреса микро соманд, выход которого соединен с информационным входом регистра адреса, вход начальной установки регистра адреса является первьт входом устройства, выход блока пам:яти соединен с входом регистра микрокоманд, первый выход которого соединен с информационным входом блока контроля и с первым информационным входом блока формирования микроопетэаций, первый выход блока формирования микроопераций является первым выходом устройства, второй выход регистра микрокоманд соединен t вторым информационным входом блока контроля и с первым информационным входом блока формирования адреса микрокоманд, второй информационньвЧ вход которого является вторым входом устройства, вход останова блока формирования адреса микрокоманд соединен с нулевым выходом первого триггера, нулевой выход второго триггера - с первым входом первого элемента И, выходы счетчика соединены с входами второго элемента И, отличающееся тем, что, с целью повьпления достоверности функционирования, в устройство введены блок сравнения, блок синхронизации, три элемента задержки, пять элементов ИЛИ, два блока элементов И и блок элементов ИЛИ, i .причем выход регистра адреса соединен с первыми входами первого и вто(Л рого блоков элементов И, вькоды коС торых соединены с информационным входом счетчика и первым входом блока элементов ИЛИ соответственно, выход счетчика соединен с первым информационным входом блбка сравнения и с первым входом третьего блока элементов И, выход которого соеди4 нен с вторым входом блока элеменсл тов ИЛИ, выход блока элементов ИЛИ соединен с вторым информационным вхоел дом блока сравнения и третьим информационным входом блока контроля и с адресным входом блока памяти, тактовый вход которого соединен с выходом первого элемента ИЛИ, первый вход первого элемента ИЛИ - с первым выходом блока синхронизации, второй выход которого соединен с вторым входом, первого элемента ИЛИ и с входом первого элемента задержки, выход первого элемента задержки - со счетным входом счетчика, выход перрого элемента И через элемент НЕ - с входом

I

Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве устройства управления ЭВМ и других систем.

Известны микропрограммные устройства с самоконтролем, содержащие блок памяти микрокоманд с регистрами адреса и микрокоманд, блок формирования микроопераций и блок контроля П и 2.

Недостатками этих устройств являю ся большой объем блока памяти микрокоманд, большие затраНг времени на профилактический контроль и низкая достоверность функционирования.

Известно также микропрограммное устройство управления с самоконтролем, содержащее два блока памяти микрокоманд, два регистра адреса, два 5 формирователя адреса, два регистра микрокоманд, два счетчика, два блока формирования микроопераций, два блока контроля, два блока сравнения, два регистра адреса возврата, триг10 геры, элементы И, ИЛИ и НЕ 3 3Недостатками этого устройства являются большая сложность, обусловленная двухканальным принцитюм построения устройства, а также, низкая 15 достоверность функционирования.

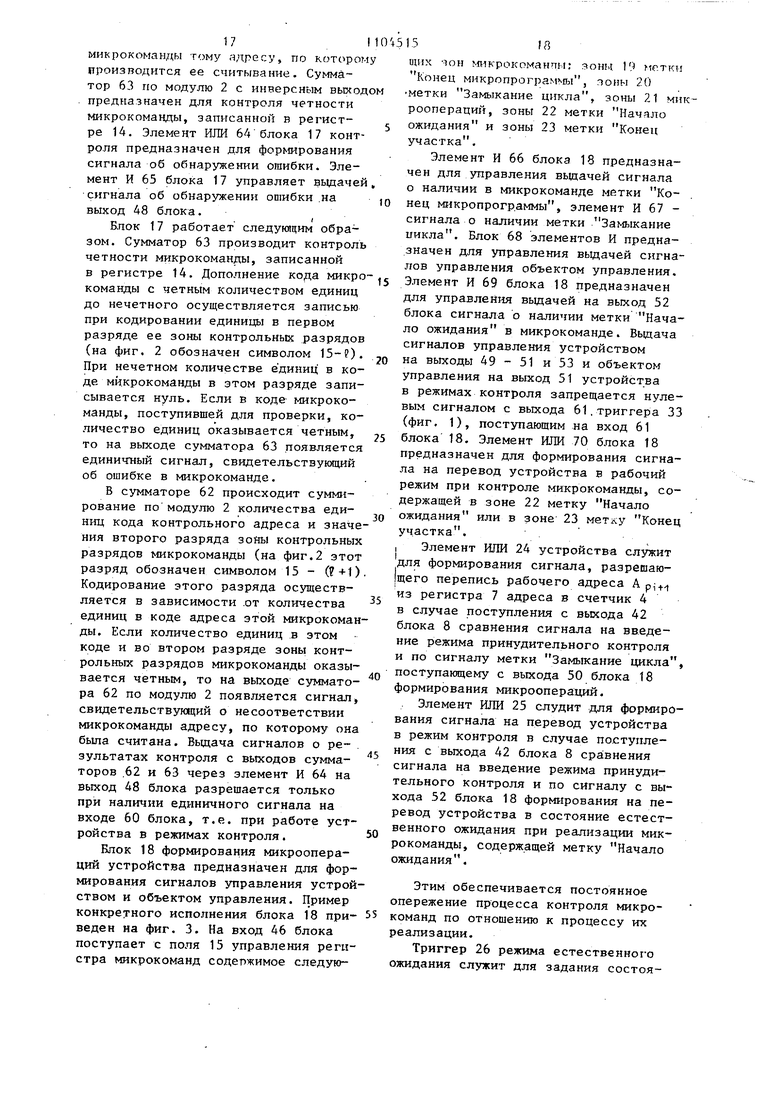

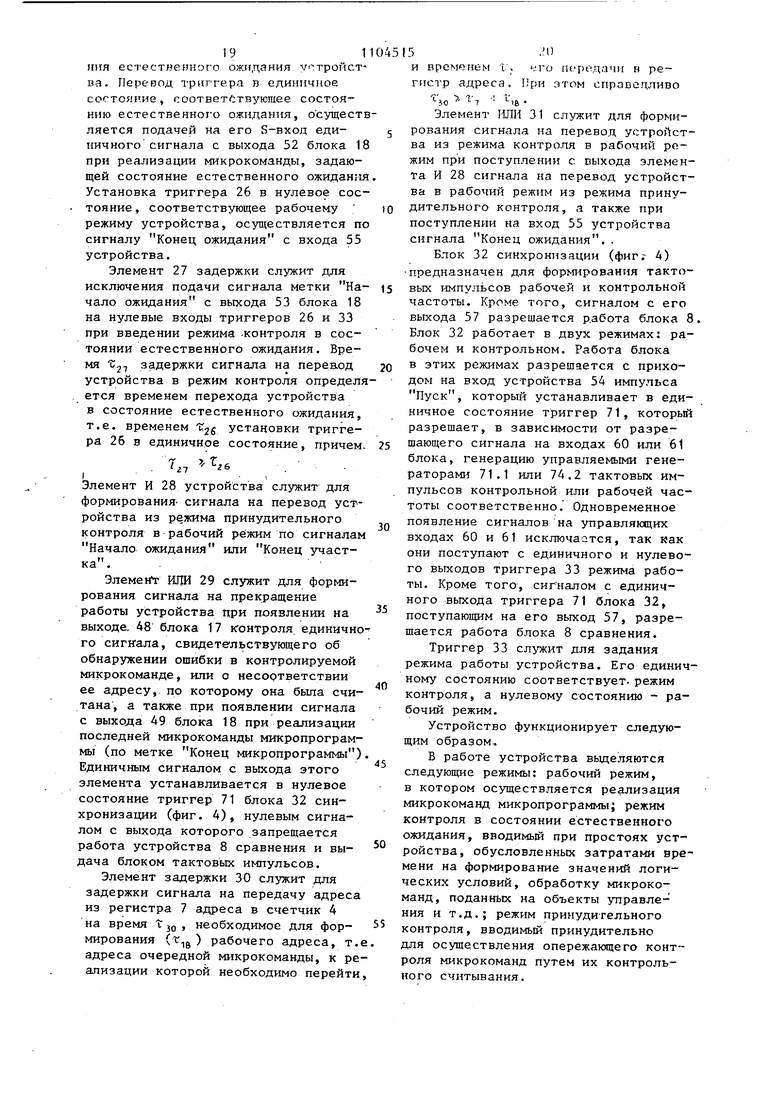

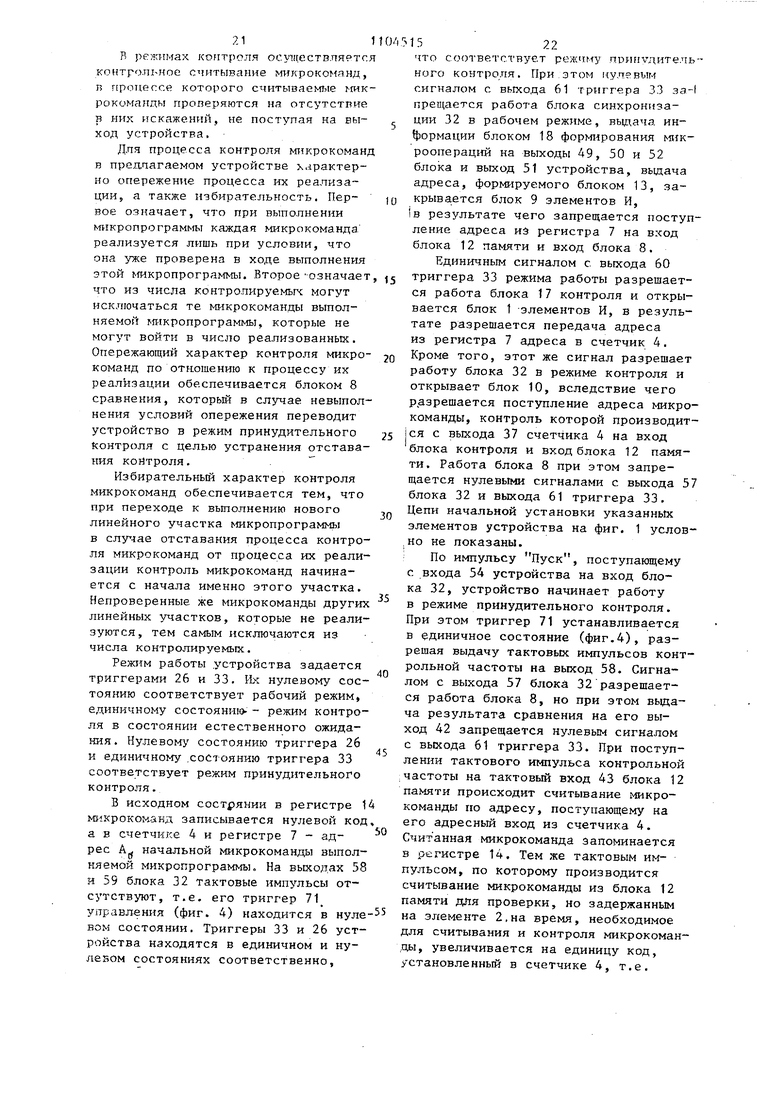

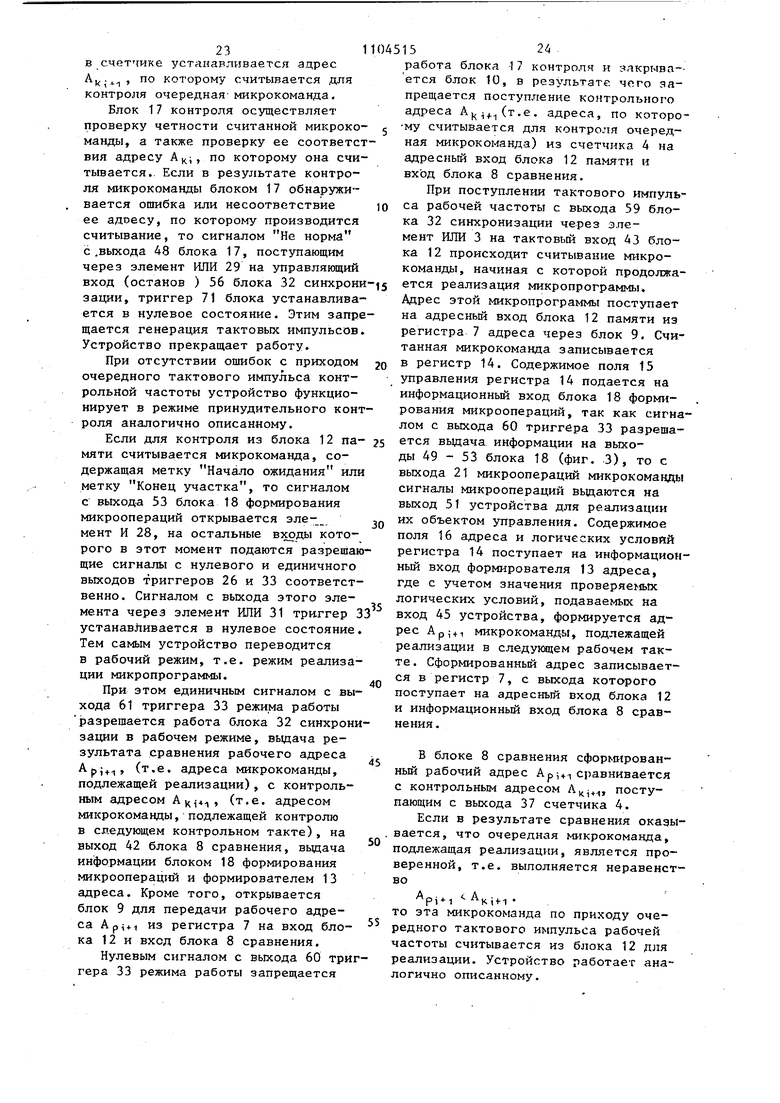

Наиболее близким по технической сущности и достигаемому резу.чьтату 3 к и;б1 0Г :;гп10 ян1 Я1тсч миг.ропрсг1аммноо. устро1 к тво V т травления с сгямоконтролем, содержагаее блок элементен И, элемент НЕ, два элемента И, два RS-трнгтера., счетчик, регистр адреса, блок памяти, регистр микрокоманд, блок контроля, блок формирования микроопераций и блок формирования адреса микрокоманд, выход которого соединен с информационным BXO дом регистра адреса, вход начальнор установки регистра адреса является первым входом устройства, выход блока памяти соединен с входом регистра микрокоманд, первый выход которого соединен с первым информационным вхо дом блока контроля, а также с первым информационным входом блока формирования микроопераций, первьй выход блока формирования микроопераций является первым выходом устройства, .второй выход регистра микрокоманд соединен с вторым информационным вхо дом блока контроля, а также с первым информационным входом блока формирования адреса микрокоманд, второй информационньй вход которого является вторым входом устройства, управляющий вход блока формирования адреса микрокоманд соединен с нулевым выходом первого триггера, нулевой выход второго триггера соединен с первым входом первого элемента И, выходы счетчика соединены с группой входов второго элемента И, Основным режимом работы известног устройства является рабочш режим, в котором осуществляется считывание микрокоманд из блока памяти и выдача их через блок формирования микроопер ций на объект управления. В моменты простоя устройства, вызванные ожиданием окончания формирования лог 1ческих условий или окончания выполнения микрокоманд объектом управления, устройство работает в режиме естественного ожидания и при этом осуществ ляет контрольное считывание микрокоманд из блока памяти в порядке возрастания нойеров ячеек памяти, начиная с той, на которой было прекращено контрольное считывание в предыдущем режиме ожидания. Причем выдача микроопераций на объект управления блокируется, а блоком контроля осуществляется контроль отсутствия иска жений в считанной микрокоманде. По окончании реализации микропрограммы режим ожидания вводится принудитель13лно .Ulf ОСЛЦСГТВ.ЧйНИЯ V-OHTpO.ibtfOlt; считывания тех гикрокома1 1 микр мтрограммы, которые oc.T;i.n)-irь попроверенными за время пребывания в режимах . естественного ожидания. При лыполнении очередной микропрограммы процесс контроля микрокоманд осуществляется, начиная с начальной микрокоманды этой микропрограммы 4 J. Однако устройство имеет низкую достоверность функционирования, обусловленную отсутствием в нем оборудования, которое устанавливяло бы взаимосвязь между процессом контрольного считывания и процессом реализации микрокоманд. Вследствие этого в устройстве возможно отставаниеПроцесса контроля микрокоманд от процесса их реализации при выполнении микропрограммы, что приводит к выда1 е их непроверенными для исполнения, а значит к снижению достоверности функционирования . Кроме того, устройство обладает низким быстродействием, которое обусловлено отсутствием избирательности при контроле микрокоманд, т.е. тем, что проверке подвергаются не только те микрокоманды, которые будут реализованы, но и те, которые вследствие разветвленности микропрограммы не войдут в реализуемую ею ветвь. Цель изобретения - повьпцение надежности, достоверности функционирования и быстродействия устройства. Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее блок элементов И, элемент НЕ, два элемента И, два RS-триггера, счетчик, регистр адреса, блок памяти, регистр микрокоманд, блок контроля, блок формирования микрооперац1ш и блок формирования адреса микрокоманд, выход которого соединен с информационным входом регистра адреса, вход начальной установки регистра адреса является первым входом устройства, выход блока памяти соединен с входом регистра микрокоманд, первый выход которого соединен с первым информационным входом блока контроля, и с первым информационным входом блока формирования микроопераций, первый выход блока формирования микроопераций является первым выходом устройства, второй выход регистра микрокоманд соединен с вторым информационным входом блока контроля и с первым ь информяциоиным входом блока формиро вания адреса микроксжанд, второй информационный вход которого являет ся вторым входом устройства, вход останова блока формирования адреса микрокоманд соединен с нулевым выхо дом первого триггера, нулевой выход второго триггера - с первым входом первого элемента И, выходы счетчика соединены с входами второго элемента И, введены блок сравнения, блок синхронизации, три элемента задержк пять элементов ИЛИ, два блока элеме тов И и блок элементов ИЛИ, прш1ем выход регистра адреса соединен с пе выми входами первого и второго блоков элементов И, выходы которых сое динены с информационным входом счет чика и первым входом блока элементов ИЛИ соответственно, выход счетчика соединен с первым информационным Ьходом блока сравнения и с первым входом третьего блока элементов И, выход которого соединен с вторым входом блока элементов ИЛИ, выход блока элементов ИЛИ соединен с вторым информационным входом блок сравнения и третьим информационным входом блока контроля и с адресным входом блока памяти, тактовый вход которого соединен с выходом первого элемента ИЛИ, первый вход первого элемента ИЛИ - с первым выходом бло ка синхронизации, второй выход кото рого соединен с вторым входом перво го элемента ИЛИ и и входом первого элемента задержки, выход первого элемента задержки - со счетным входом счетчика, выход первого элемента И через элемент НЕ - с входом записи счетчика, нулевой вькод первого триггера - с входом останова блока формирования микроопераций и с входом запрета блока сравнения входом останова блока синхронизации , третий выход которого соединен с входом разрешения блока сравнения, выход блока сравнения - с первыми входами второго и третьего элементов ИЛИ, вторые входы которых сое динены соответственно с выходами разрешения записи и начала ожидания блока формирования микроопераций, выход второго элемента ИЛИ через вт рой элемент задержки соединен с вто рым входом первого блока элементов выход третьего элемента ИЛИ через третий элемент задержки - с единичным входом первого триггера, единич ный выход первого триггера - с вторыми входами третьего блока г ле 1ентон И, с вторым ВХОДОГ4 гервого элемента И, с входами раэрешения блока контроля и блока синхронизации, вход пуска которого является входом пуска устройства, выход блока контроля подключен к первому входу четвертого элемента ИЛИ, второй вход которого соединен с выходом конца микропрограммы блока формирования микроопераций, выход четвертого элемента ИЛИ соединен С; входом останова блока синхронизации, выход конца участка блока формирования микроопераций подключен к третьему входу первого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, второй и третий входы пятого элемента ИЛИ соединены соответственно с входами пуска и конца ожидания устройства, выход пятого элемента ИЛИ соединен с нулевыми входами первого и второго триггеров, единичный вход второго триггера соединен с выходом начала ожидания блока,формирования микроопераций. Блок формирования микроопераций содержит четыре элемента И и один элемент ИЛИ, причем вход останова блока соединен с первыми входами первого, второго, третьего и четвертого элементов И, входы блока конца микропрограммы, заключения цикла, микроопераций и конец участка соединены с вторыми входами соответственно первого, второго и третьего элементов И и первым входом элемента ИЛИ, вход начала ожидания блока соединен с вторыми входами четвертого элемента И и элемента ИЛИ, вькоды первого, второго, третьего, четвертого элементов И и элемента ИЛИ являются соответственно выходами конца микропрограммы, заключения цикла, микроопераций, начала ожидания и конца микропрограммы блока. Сущность изобретения состоит в повышении достоверности функционирования устройства за счет опережения контроля микрокоманд по отношению к процессу их реализации, а также в повышении быстродействия устройства за счет обеспечения избирательности процесса контроля микрокоманд, т,е, исключения из числа проверяемых тех микрокоманд, которые не входят в реализуемую ветвь микропрограммы. 7r Введение j ropoio я трыьего б.чоКОБ элементов И и бпока элементов ИЛР1 и обусловленных и№1 связей позволяет по сигналам с кулевого и единичного выходов первого триггера управлять подачей адреса миkpoкоманды из регистра адреса или из счетчика на адресньй вход блока памяти, а также соответственно на второй и третий информационные входы блока сравнения и блокаконтроля. Введение первого элемента ИЛИ, и обусловленных им связей необходимо для формирования сигналов считывания на тактовом входе блока памяти. Введение блока сравнения и обусловленных им связей необходимо для проверки принадлежности очередной микрокоманды, подлежащей реализации, к множеству микрокоманд,проверенных в процессе выполнения микропрограммы. Введение второго элемента ИЛИ и обусловленных им связей предназначено для формирования сигнала управления передачей гадреса с выхода регистра адреса на информационный вход счетчика в момент перехода устройства в режим принудительного контроля или в момент выполнения микрокоманды которая замыкает какой-либо цикл в микропрограмме. Соединение выхода регистра адреса с группой информационных входов счетчика через первьй блок элементов И предназначено для управления передачей кода адреса из регистра адреса в счетчик. Введение второго элемента задержки необходимо для обеспечения задерж ки сигнала передачи адреса с регистра на счетчик на время, необходимое для формирования адреса очередной микрокоманды, к выполнению которой необходимо перейти, и время записи этого адреса в регистр адреса. Введение первого элемента задержки и обусловленных им связей необходимо для задержки пpoдв жeния счетчи ка в режиме контроля на время, необходимое для считывания микрокоманды из блока памяти, записи ее в регистр микрокоманд и проверки ее блоком контроля. Введение третьего элемента ИЛИ и обусловленных им связей необходимо для формирования сигнала на единичном входе первого триггера для перепода устройства в режим контроля лиfo л случае отставания процесса конт роля микрокоманд от г:р|ПО-,. реализации, либо в случаю . Пмп;) микрокоманды, иь)екмлеГт мотку ожидания. Введение третьего элемента зад ржки и обусловленных им связе1 г предназначено для обеспечения задержки переключения первого триггера в единичное состояние на время, необходимое для переключения п единичное состояние второго триггера при введении режима контроля р состоянии естественного ожидания. Введение четвертого элемента ИЛИ и обусловленных им связей предназначено для формирования и выдачи на четвертый управляющий вход блока синхронизации сигнала на прекращение работы устройства либо при о.бнаружении ошибки в контролируемой микрокоманде, либо при выполнении конечной микрокоманды микропрограммы. Введение пятого элемента ШШ и обусловленных им связей предназначено для формирования сигнала на перевод устройства в рабочгоЧ режим в момент либо запуска микропрограммы на выполнение, либо окончания ожидания выполнения микрокоманды, либо достижения такой микрокоманды (в режиме контроля в состоянии естественного ожидания), которая имеет метку начала ожидания, либо конца линейного участка. Соединение пятого выхода блока формирования микроопераций с третьим входом первого элемента И предназначено для передачи сигнала на перевод устройства из режима принудительного контроля в рабочий режим при считывании микрокоманды, имеющей метку начала ожидания нпи конца линейного участка. Введение блока синхронизации и обусловленных им связей предназначено для формирования тактовых импульсов рабочей или контрольной частоты в зависимости от режима работы устройства, а также управления работой блока сравнения. Соединение нулевого выхода первого триггера с управляющим входом блока Формирования микроопераций предназначено для управления выдйчей сигналов на первый, второй, третий и четвертый выходы этого блока. Соединение единичного выхода первого триггера с вторым входом первого элемента И предназначено для упранле9ния формированием сигнала на перево устройства из режима принудительног контроля в рабочий режим. Соединение выхода второго элемен та И через элемент НЕ с управляющим входом счетчика предназначено для управления работой счетчика. Таким образом, введение перечисленных элементов и связей позволяет повысить достоверность фуНКЦИОНИрОвания и быстродействия устройства. На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - пример конкретног исполнения функциональной схемы бло ка контоля; йа фиг. 3 - функциональная схема блока формирования микроопераций; на фиг. А - функциональная схема блока синхронизации; на фиг. 5 - пример конкретного исполнения функциональной схемы форми рования адреса микрокоманды; на фиг. 6 - пример конкретного исполне ния функциональной схемы блока срав нения для трехразрядного адреса; на фиг. 7 - пример разбиения микропрограммы на линейные участки их ранжирования и последовательной нумерации микрокоманд. Устройство (фиг. ,1) содержит первый блок 1 элементов И, первый элемент 2 задержки, первый элемент ИЛИ 3, счетчик 4, второй элемент И 5, элемент НЕ 6, 7 адреса, блок 8 сравнения, второй 9 и третий 10 блоки элементов И, блок 11 элементов ИЛИ, блок 12 памя ти, блок 13 формирования адреса микрокоманды, регистр 14 микрокоман с полем 15 управления и Полем 16 адреса и логических условий, блок 1 контроля, блок 18 формирования микроопераций, содержащий следующие вы ходы: вьпсод 19 метки Конец микропрограммы , выход 20 метки Заключе ние цикла, выход 21 сигналов микроопераций, выход 22 метки Начало ожидания, выход 23 метки Конец участка, второй 24 и третий 25 эле 1менты ИЛИ, второй триггер 26, третий элемент задержки 27, первьй эле мент И 28, четвертый элемент ИЛИ 29 второй элемент задержки 30, пятый элемент ИЛИ 31, блок 32 синхронизации, первый триггер 33, информацион ный 34,. счетный 35 и останова 36 йх ды счетчика 4, выход 37 счетчика 4, вход 38 начальной установки, являющийся первым входом ус- пойства, и 1510 информационный вход 39 регистра 7 адреса, выход .40 регистра 7 адреса, группу выходов 41 элементов ИЛИ блока 11 элементов ИЛИ, выход 42 блока 8 сравнения, тактовый вход 43 блока 12 памяти, информационный вход 44 регистра 14 микрокоманд, второй вход 45 блока 13 формирователя адреса, являющийся вторым входом устройства, .первый 46 и второй 47 выходы регистра 14 микрокоманд, выход 48 блока 17 контроля, четвертый 49 и второй 50 выходы блока 18 формирования микроопераций, первый 51 выход блока 18 формирования микроопераций, являющийся первым выходом устройства, третий 52 и пятый 53 выходы блока 18 формирования микроопераций, третий вход 54 устройства, второй вход 55 пятого элемента ИЛИ 31, являющийся четвертым входом устройст|Ва, четвертый управляющий вход 56 1блска 32 синхронизации, третий 57, второй 58 и первый 59 выходы блока 32 синхронизации, единичный 60 и нулевой 61 выходы первого триггера 33. Блок 17 контроля (фиг. 2) содержит первый 62 и второй 63 сумматоры по модулю два с инверсньгмн выходами, элемент ИЛИ 64 и элемент И 65. Блок 18 формирования микроопераций (фиг. 3) содержит первый 66 и второй 67 элементы И, блок 68 элементов И, третий элемент И 69 и элемент ИЛИ 70. Блок 32 синхронизации (фиг. 4) содержит RS-триггер 71, первый 72 и второй 73 элементы И и управляемый генератор 74, состоящий из двух генераторов 74.1 и 74.2. Блок 13 формирования адреса микрокоманд (фиг. 5) содержит блок 75 мультиплексоров и блок 76 элементов И. Блок 8 сравнения (фиг. 6) содержит первый 77 и второй 78 блоки элементов НЕ, первый 79 и второй 80 элементы ИЛИ, первый элемент И 81, третий 82 и четвертый 83 элементы ИЛИ, второй элемент И 84, пятый 85 и шестой 86 элементы ИЛИ, третий 87, четвертый 88, пятый 89 и шестой 90 элеменфы И, седьмой элемент ИЛИ 91, седьмой элемент И 92, восьмой 93 и девятый 94 элементы ИЛИ, восьмой элемент И 95, группу выходов 96 первого б.пока 77 11 элементов ЧЕ, группу выходотз 97 BTQ poio блока 78 элементов НЕ. На фиг. 7 поз. 1-17 обозначены порядковые номера м1-1крокоманд в мик ропрограмме, поз. О - IV - ранги линейных участков микропрограммы. В виде прямоугольников условно пока зан формат каждой микропрограммы. Символ КУ означает, что в соотзетствующей зоне микрокоманды преставлена метка Конец участка, которой помечаются микрокоманды конца линейного участка. Символ НО означает что в соответствующей зоне микрокоманды проставлена метка Начало ожидания, свидетельствующая о том что после реализации этой микрокоманды устройство перейдет в состояние естественного ожидания. Символ ЗЦ означает, что в соответствующей зоне микрокоманды проставлена метка Замыкание цикла, которой помечаются начальные микрокоманды возвратных линейных участков. Символ Е означает, что в соответствующей зон микрокоманды проставлена метка, которой помечается конечная микроко манда микропрограммы. Прочерк означает отсутствие информации в зонах перечисленных меток. Элементы устройства имеют следующее назначение (фиг. 1). Блок 1 элементов И предназначен для управления передачей адреса микрокоманды из регистра 7 адреса в счетчик 4 Адрес очередной микрокоманды, подлежащей реализации, переписывается в счетчик 4 в процессе введения режима принудительного контроля. Элемент задержки 2 предназначен для задержки тактовых импульсов контрольной частоты, поступающих на динамический вход 35 счетчика 4 на время f , необходимое для-считывания микрокоманды из блока 12 памяти записи ее в регистр микрокоманд , и проверки ее блоком 17 контроля Tg,. При этом справедливо соотношение + RG14+ 6K.Элемент ИЛИ 3 служит для формирова ния сигналов считывания на тактовом входе 43 блока 12 памяти. Счетчик 4 предназначен для хранения адреса А, очередной микроко манды, подлежащей контролю в процессе реализации микрокоманд микропрограммы, т.е. в рабочем режиме, ia также формрфования адреса А очередлой кентро;ч1русм(П( пнт г ч -гМгчн ды в процессе контроля. Глс илгЬоолмционный вход 34 предназначен лпя па раллельной записи адреса А pit, очоредной микрокоманды, подлежащей реализации, и поступаюп1его из регистра 7 адреса при введении режима принудительного контроля. Это позволяет достичь избирательности принудительного контроля, т.е. обеспечить проверку только тех микрокоманд, которые подлежат реализации. В процессе контроля микрокоманд микропрограммы адрес А очередной контролируемой микрокоманды формируется путем увеличения кода, установленного в счетчике 4, на единицу при поступлении на счетньй вход 35 счетчика тактового импульса контрольной частоты. С целью исключения повторной проверки уже проверенных микрокоманд при обнулении счетчика 4 в результате его переполнения по нулевому сигналу на его входе 36 запрещается подсчет счетчика 4 тактовых импульсов контрольной частоты, поступающих на его счетньпЧ вход 35. Элемент И 5 служит для фиксации момента заполнения счетчика 4 с целью исключения его обнуления изза переполнения. При заполнении счетчика 4 на выходе элемента 5 появляется сигнал, которым запрещается подсчет импульсов контрольной частоты счетчиком. Элемент НЕ 6 служит д.пя управления счетчиком 4, Регистр 7 адреса служит для хранения адреса Ар микрокоманды, подлежащей реализации, и выдачи его на входы элементов И 1 и 9. Вход 38 регистра 7 предназначен для начальной установки адреса AQ начальной микрокоманды микропрограммы. Вход 39 регистра 7 предназначен для параллельной записи в регистр 7 кода очередного адреса, сформированного блоком 13 формирования адреса. Блок 8 сравнения предназначен для проверки вхождения очередной микрокоманды, подлежащей реализации, в число микрокоманд, проверенных в процессе реализации микропрограммы, Проверка осуществляется путем сравнения рабочего и контрольного адресов. При этом под контрольным и рабочим адресом понимается адрес очередной микрокоманды, подлежащей 13 .t соответственно контролю или реализации. Такой принцип проверки возможен при условии, что кодирование адресов микрокоманд осзпцествляется в соответствии с принципом ранжирования линейных участков микропрограммы и последовательной нумерации микрокоманд каждого участка таким образом чтобы микрокоманды участков старших рангов, а также микрокоманды одного же участка, реализуемые позже других микрокоманд этого участка, имели большой порядковый номер. Этот номер, представленный в двоичной системе , и является кодом адреса этой микропрограммы. Под микрокомандой схождения понимается такая микрокоманда, к которой в пределах данной микропрограммы возможен переход от двух и более других различных микрокоманд. Под микрокомандой ветвления следует понимать такую микрокоманду, от которой возможен переход к двум и более другим различным микрокомандам, отличным от нее самой. При этом линейным участком ьшкропрограммы называется такая последовательность микрокоманд этой микропрограммы, которая не содержит микрокоманд ветвления, кроме конечных в дан ном участке, и не содержит микрокоманд схождения, кроме начальных в этом участке. Рангом линейного участка называется наибольшее количество линейных участков, расположен ных на пути от начала микропрограммы к началу данного участка. При ранжировании участков микропрограммы ее возвратные линейные участки должны быть разорваны в местах замыкания циклов. Под возвратным линейным участком микропрограммы сле дует понимать такой участок, который приводит к образованию цикла в микро программе . Пример разбиения микропрограммы на линейные участки, их ранжирования и последовательной нумерации микрокоманд приведен на фиг. 7. В блоке 8 сравнения происходит сравнение контрольного А( и рабочего , адресов. Если очередная микрокоманда, подлежащая реализации, оказывается непроверенной, то выполняется .соотношение Кл+1 PU н на выходе 42 блока 8 появляется си нал, которым устройство переводится j 5 В режим принудительного контроля. Пример конкретного исполнения блока 8 сравнения представлен на фиг.6. Элементы НЕ 77 и 78 блока 6 сравнения предназначены для получения обратного кода контрольного и рабочего адресов соответственно. Группы элементов ШШ 79 и 80 и элемент И 88 блока б предназначены д.пя формирования сигнала R1 равенства первых разрядов кодов адресов, поступающих на входы 37 и 41 блока. При равенстве первых разрядов элемент 88 открывается единичными сигналами с выходов элементов 79 и 80 блока 6. Аналогично совокупность элементов ИЛИ 82 и 83 и элемент И 89 -блока 6, а также совокупность элементов ИЛИ 85 и 86 и элемент И 90 блока 6 предназначены для формирования сигналов R 2 и R 3 равенства соотцетственно двух и трех разрядов кодов адресов. При этом сигнал R 3 равенства трех разрядов кодов на выходе элемента И 90 формируется по равенству третьих разрядов, т.е. по единичным сигналам с выходов элементов ИЛИ 85 и 86 блока, с учетом сигнала о равенстве двух предыдущих разрядов (R 2) поступающего на вход элемента И 90с выхода элемента И 89. Элемент 81 блока 6 предназначен для формирования сигнала Ml о том, что первый разряд рабочего адреса больше первого разряда контрольного адреса. Элемент И 84 (87) блока 6 предназначен для формирования сигнала о том, что второй (третий) разряд рабочего адреса больше сбответствующего разряда контрольного адреса, а число, соответствующее предьщущим разрядам рабочего адреса, не меньше числа, представленного соответствующими разрядами контрольного адреса. Элемент И 92 блока 6 предназначен для формирования сигнала И 2 о том, что значение и первого, и второго разрядов рабочего адреса не меньше значений соответСтвукнцих разрядов контрольного адреса. Элемент ИЛИ 93 (91) блока 6 предназначен для формирования сигнала F 2 (F 3), свидетельствующего о том, что код двух (трех) разрядов рабочего адреса больше кода двух (трех) собтветствующих разрядов контрольного адреса. Элемент И 94 блока 6 предназначен для формироваНИН nn-Hajbri, с;ридетель(;тную1цего о Bi;uri;inHP-H4n соогистленмя Лр, , Л;,.,,,. Элемент И 95 блока 6 управляет выдачей результата сравнения на выход 42 блока 6. Блоки элементов И 9 и 10 и ИЛИ 1 устройства служат для управления передачей адреса считываемой из блока 12 памяти микрокоманды с выхода регистра 7 адреса или с выхода счетчика 4 в рабочем режиме и в режи ме контроля соответственно. Блок 12 памяти предназначен для хранения микрокоманд микропрограмм. При поступлении, импульса на тактовый вход 43 блока 12 памяти происходит считывание микрокоманды по адресу, поступающему на адресный вход блока памяти с выхода блока 11 элементов ИЛИ. В формате микрокоманды, записанной в блоке памяти, можно выделить следующие зоны: зону логических усло вий, в которой задаются коды проверяемых логических условий; зону адре са, предназначенную для задания неизменяемой части адреса очередной микрокоманды; зону метки Конец микропрограммы, которой помечается Iмикрокоманда, являющаяся последней в микропрограмме; зону метки Замыка ние цикла, которой помечаются микро команды, при реализации которых воз можен переход к повторному выполнению уже реализованного участка микро программы; зону микроопераций, в ко рой задается код микроопераций; зону контрольных разрядов, в которой коди рованием единицей первого разряда дополняется до нечетного количества число единиц в микрокоманде, а кодированием единицей второго разряда этой зоны задается соответствие микрокоманды адресу, по которому произIводилось ее считывание; зону метки Начало ожидания, которой помечаетс микрокоманда, задающая состояние естественного ожидания; зону метки Конец участка, которой помечаются микрокоманды, завершающие линейные участки микропрограммы. Блок 13 формирования адреса микро команды (фиг. 5) предназначен для формирования рабочего адреса, т.е. адреса очередной микрокоманды, подлежащей реализации. Информация в блок 13 поступает на его информаци онный вход с поля 16 регистра 14, 15fi где зрписывается содержимое зоны яцЬеса и зоны логических условий микрокоманды. Содержимое зоны адреса подается с входа блока 13 на блок элементов И 76, управляютцих передачей адреса из блока 13. Модифицируемая часть адреса формируется блоком 75 мультиплексоров, осуществляющим проверку значений тех логических условий считанной микрокоманды, и поступает на вход 45 блока 13. Сформированная блоком 75 мультиплексоров модифицируемая часть адреса присоединяется к,неизменяющейся части в качестве младщих разрядов. Выдача сформированного адреса на выход блока 13 разрешается только при наличии единичного сигнала на его управляющем входе,т.е. только в рабочем режиме. Регистр 14 микрокоманд устройства предназначен для хранения микрокоманды, считанной из блока 12 памяти, В регистре 14 можно выделить два поля: поле 15 управления и поле 16 адреса и логических условий. В поле 16 хранится содерж1гмое зоны адреса и зоны логических условий микрокоманды. Эта информация используется для формирования рабочего адреса Ар;4, , т.е. адреса очередной микрокоманды, под,лежащей реализации. В поле 15 управ1ления хранится содержимое зон меток I Конец микропрограммы, Начало ожидания, Замыкание цикла, Конец участка, а также зоны микроопераций и зоны контрольных разрядов. Эта информация используется при формировав НИИ сигналов управления работой устройства, а также сигналов микроопераций. Кроме того, информация с выходов полей 15 и 16 регистра 14 поступает в блок 17 контроля для проверки. Блок 17 контроля предназначен для проверки отсутствия ошибок в микрокоманде, записанной на регистре 14, и проверки ее соответствия адресу, по которому она считывается из блока 12 памяти. Работа блока 17 контроля в рабочем режиме запрещается нулевым сигналом, поступающим на управляющий вход с выхода триггера 33 режима работы. В качестве одного из возможных вариантов реализации блока контроля может быть использована схема (фиг.2), в которой сумматор 62 по модулю 2 с инверсным выходом предназначен для проверки соответствия проверяемой 17И микрокоманды тому адресу, по производится ее считывание. Сумматор 63 по модулю 2 с инверсным выход предназначен для контроля четности микрокоманды, записанной в регистре 14. Элемент ИЛИ 64 блока 17 контроля предназначен для формирования сигнала об обнаружении ошибки. Элемент И 65 блока 17 управляет выдачей сигнала об обнаружении ошибки .на выход 48 блока. Блок 17 работает следующим образом. Сумматор 63 производит контроль четности микрокоманды, записанной в регистре 14. Дополнение кода микро команды с четным количеством единиц до нечетного осуществляется записью при кодировании единицы в первом разряде ее зоны контрольных разрядов (на фиг. 2 обозначен символом 15-). При нечетном количестве единиц в коде микрокоманды в этом разряде записывается нуль. Если в коде микрокоманды, поступившей для проверки, количество единиц оказывается четным, то на выходе сумматора 63 появляется единичный сигнал, свидетельствующий об ошибке в микрокоманде. В сумматоре 62 происходит суммирование по модулю 2 коли ества единиц кода контрольного адреса и значе ния второго разряда зоны контрольных разрядов микрокоманды (на фиг.2 этот разряд обозначен символом 15 - (+1) Кодирование этого разряда осуществляется в зависимости .от количества единиц в коде адреса этой микрокоман ды. Если количество единиц в этом коде и во втором разряде зоны контрольных разрядов микрокоманды оказывается четным, то на выходе сумматора 62 по модулю 2 появляется сигнал, свидетельствующий о несоответствии микрокоманды адресу, по которому она была считана. Вьодача сигналов о результатах контроля с выходов сумматоров .62 и 63 через элемент И 64 на выход 48 блока разрешается только при нали1ии единичного сигнала на входе 60 блока, т.е. при работе устройства в режимах контроля. Блок 18 формирования микроопераций устройства предназначен для формирования сигналов управления устрой ством и объектом управления. Пример конкретного исполнения блока 18 приведен на фиг. 3. На вход 46 блока поступает с поля 15 управления регистра микрокоманд содержимое следую 8щнх чон NfliKpoKOMannM; зоны 19 метки Конец MHKponporpaMNfbi, зоны 20 метки Замыкание цикла, зоны 21 микроопераций, зоны 22 метки Начало ожидания и зоны 23 метки Конец S acTKa. Элемент И 66 блока 18 предназначен для управления выдачей сигнала о наличии в микрокоманде метки Конец микропрограммы, элемент И 67 сигнала о наличии метки Замыкание иикла. Блок 68 элементов И предназначен для управления выдачей сигналов управления объектом управления. Элемент И 69 блока 18 предназначен для управления вьщачей на выход 52 блока сигнала о наличии метки Начало ожидания в микрокоманде. Вьщача сигналов управления устройством на выходы 49 - 51 и 53 и объектом управления на выход 51 устройства в режимах контроля запрещается нулевым сигналом с выхода 61,триггера 33 (фиг. 1), поступающим на вход 61 блока 18. Элемент ИЛИ 70 блока 18 предназначен для формирования сигнала на перевод устройства в рабочий режим при контроле микрокоманды, содержащей в зоне 22 метку Начало ожидания или в зоне 23 метку Конец участка. I Элемент ИЛИ 24 устройства служит для формирования сигнала, раэрешаю щего перепись рабочего адреса А pi из регистра 7 адреса в счетчик 4 в случае поступления с выхода 42 блока 8 сравнения сигнала на введение режима принудительного контроля и по сигналу метки Замыкание цикла, поступающему с выхода 50 блока 18 формирования микроопераций. . Элемент ИЛИ 25 слудит для формирования сигнала на перевод устройства в режим контроля в случае поступления с выхода 42 блока 8 сра внения сигнала на введение режима принудительного контроля и по сигналу с выхода 52 блока 18 формирования на перевод устройства в состояние естественного ожидания при реализации микрокоманды, содержащей метку Начало ожидания. Этим обеспечивается постоянное опережение процесса контроля микрокоманд по отношению к процессу их реализации. Триггер 26 режима естественного ожидания служит для задания состоя1911

ПИЯ естестненного ожидания устройства. Перевод триггера в единичное состоя ие , соответствующее состоянию естественното ожидания, осуществляется подачей на его S-вход единичного сигнала с выхода 52 блока 18 при реализации микрокоманды, задающей состояние естественного ожидания Установка триггера 26 в нулевое состояние, соответствующее рабочему режиму устройства, осуществляется по сигналу Конец ожидания с входа 55 уотройства.

Элемент 27 задержки служит для исключения подачи сигнала метки Начало ожидания с выхода 53 блока 18 на нулевые входы триггеров 26 и 33 при введении режима -контроля в состоянии естественного ожидания. Время Cj, задержки сигнала на перевод устройства в режим контроля определяется временем перехода устройства в состояние естественного ожидания, т.е. временем ITjg установки триггера 26 0 единичное состояние, причем.

.

27

Элемент И 28 устройства служит для формирования- сигнала на перевод устройства из режима принудительного контроля в рабочий режим по сигналам Начало ожидания или Конец участка.

Элемент ИЛИ 29 служит для формирования сигнала на прекращение работы устройства цри появлении на выходе. 48 блока 17 контроля единично го сигкала, свидетельствующего об обнаружении ошибки в контролируемой микрокоманде, или о несоответствии ее адресу,- по которому она была считана, а также при появлении сигнала с выхода 49 блока 18 при реализации последней микрокоманды микропрограммы (по метке Конец микропрограммы) Единичным сигналом с выхода этого элемента устанавливается в нулевое состояние триггер 71 блока 32 синхронизации (фиг. 4), нулевым сигналом с выхода которого запрещается работа устройства 8 сравнения и выдача блоком тактовых импульсов.

Элемент задержки 30 служит для задержки сигнала на передачу адреса из регистра 7 адреса в счетчик 4 на время t JQ, необходимое для формирования () рабочего адреса, т. адреса очередной микрокоманды, к реализации которой необходимо перейти

15-Ч

и временем L , «го передачи в регистр адреса. При этом справедливо

-16

Элемент ИЛИ 31 служит для формирования сигнала на перевод устройства из режима контроля в рабочий режим при поступлении с выхода элемента И 28 сигнала на перевод устройства в рабочий режим из режима принудительного контроля, а также при поступлении на вход 55 устройства сигнала Конец ожидания..

Блок 32 синхронизации (фигг 4) предназначен для формирования тактовых импульсов рабочей и контрольной частоты. Кроме того, сигналом с его выхода 57 разрешается работа блока 8 Блок 32 работает в двух режимах: рабочем и контрольном. Работа блока в этих режимах разрешается с приходом на вход устройства 54 импульса Пуск, который устанавливает в единичное состояние триггер 71, которьй разрешает, в зависимости от разрешающего сигнала на входах 60 или 61 блока, генерацию управляемыми генераторами 71.1 или 74.2 тактовых импульсов контрольной или рабочей частоты соответственно. Одновременное появление сигналов на управляющих входах 60 и 61 исключается, так как они поступают с единичного и нулевого выходов триггера 33 режима работы. Кроме того, сигналом с единичного выхода триггера 71 блока 32, поступающим на его выход 57, разрешается работа блока 8 сравнения.

Триггер 33 служит для задания режима работы устройства. Его единичному состоянию соответствует, режим контроля, а нулевому состоянию - рабочий режим.

Устройство функционирует следующим образом..

В работе устройства выделяются следующие режимы: рабочий режим, в котором осуществляется реализация микрокоманд микропрограммы; режим контроля в состоянии естественного ожидания, вводимый при простоях устройства, обусловленньгх затратами времени на формирование значений логических условий, обработку микрокоманд, поданных на объекты управле-ния и т.д.; режим принудительного контроля, вводимый принудительно для осуществления опережающего контроля микрокоманд путем их контрольного считывания. 21 В режимах контроля осушестиляртся контгольное сшттывание микрокоманд, в процессе которого считываемтяе микрокоманды проверяются на отсутствие в них искажений, не поступая на выход устройства. Для процесса контроля микрокоманд в предлагаемом устройстве характерно опережение процесса их реализации, а также избирательность. Первое означает, что при выполнении микропрограммы каждая микрокоманда реализуется лишь при условии, что она уже проверена в ходе выполнения этой микропрограммы. Второе-означает что из числа контролируемых могут исключаться те микрокоманды выполняемой микропрограммы, которые не могут войти в число реализованных. Опережающий характер контроля микрокоманд по отношению к процессу их реализации обеспечивается блоком 8 сравнения, который в случае невыполнения условий опережения переводит устройство в режим принудительного Контроля с целью устранения отставания койтроля, Избирательный характер контроля микрокоманд обеспечивается тем, что при переходе к вьтолнению нового линейного участка микропрограммь в случае отставания процесса контроля микрокоманд от процесса их реализации контроль микрокоманд начинается с начала именно этого участка. Непроверенные же микрокоманды других линейных участков, которые не реализуются, тем самым исключаются из числа контролируемых;. Режим работы устройства задается триггерами 26 и 33. llx нулевому состоянию соответствует рабочий режим, единичному состоянию- - режим контроля в состоянии естественного ожидания. Нулевон1 состоянию триггера 26 и единичному .состоянию триггера 33 соответствует режим принудительного контроля. В исходном состоянии в регистре микрокоманд записывается нулевой код а в счетчике 4 и регистре 7 - адрес А начальной микрокоманды выполняемой микропрограммы На выходах 58 и 59 блока 32 тактовые импульсы отсутствуют, т.е. его триггер 71 управления (фиг. 4) находится в нуле вом состоянии. Триггеры 33 и 26 устройства находятся в единичном и нулевом состояниях соответственно. 1522 что соответствует pemtitfy прир1Удитель-ного контроля. При.этом кулевым сигналом с выхода 61 триггера 33 за-1 прещается работа блока синхронизации 32 в рабочем режиме, выдача )Ормации блоком 18 формирования микрооперацт на выходы 49, 50 и 52 блока и выход 51 устройства, выдача адреса, формируемого блоком 13, закрывается блок 9 элементов И, в результате чего запрещается поступление адреса из регистра 7 на вход блока 12 памяти и вход блока 8. Единичным сигналом с выхода 60 триггера 33 режима работы разрешается работа блока 17 контроля и открывается блок 1 элементов И, в результате разрешается передача адреса из регистра 7 адреса в счетчик 4. Кроме того, этот же сигнал разрешает работу блока 32 в режиме контроля и открывает блок 10, вследствие чего р азрешается поступление адреса микрокоманды, контроль которой производит|ся с выхода 37 счетчика 4 на вход блока контроля и вход блока 12 памяти. Работа блока 8 при этом запрещается нулевыми сигналами с выхода 57 блока 32 и выхода 61 триггера 33. Цепи начальной установки указаннь1х элементов устройства на фиг. 1 условно не показаны. По импульсу Пуск, поступающему с входа 54 устройства на вход блока 32, устройство начинает работу в режиме принудительного контроля. При этом триггер 71 устанавливается в единичное состояние (фиг.4), разрешая выдачу тактовых импульсов контрольной частоты на выход 58. Сигналом с выхода 57 блока 32 разрешается работа блока 8, но при этом выдача результата сравнения на его выход 42 запрещается нулевым сигналом с выхода 61 триггера 33. При поступлении тактового импульса контрольной частоты на тактовый вход 43 блока 12 памяти происходит считывание микрокоманды по адресу, поступающему на его адресный вход из счетчика 4. Считанная микрокоманда запоминается в регистре 14. Тем же тактовым импульсом, по которому производится считывание микрокоманды из блока 12 памяти для проверки, но задержанным на элементе 2,на время, необходимое для считывания и контроля микрокоманда:, увеличивается на единицу код, установленный в счетчике 4, т.е. в счетчике устанавливается адрес Ац. , по которому считывается для контроля очередная- микрокоманда. Блок 17 контроля осуществляет проверку четности считанной микроко манды, а также проверку ее соответс вия адресу , по которому она счи тывается. Если в результате контроля микрокоманды блоком 17 обнаруживается ошибка или несоответствие ее адоесу, по которому производится считывание, то сигналом Не норма с .выхода 48 блока 17, поступающим через элемент ИЛИ 29 на управляющий вход (останов ) 56 блока 32 синхрон зации, триггер 71 блока устанавлива ется в нулевое состояние. Этим запр щается генерация тактовых импульсов Устройство прекращает работу. При отсутствии ошибок с приходом очередного тактового импульса контрольной частоты устройство функционирует в режиме принудительного кон роля аналогично описанному. Если для контроля из блока 12 па мяти считывается микрокоманда, содержащая метку Начало ожидания ил метку Конец участка, то сигналом с выхода 53 блока 18 формирования микроопераций открывается эле- мент И 28, на остальные входы которого в этот момент подаются разреша щие сигналы с нулевого и единичного выходов триггеров 26 и 33 соответст венно. Сигналом с выхода этого элемента через элемент ИЛИ 31 триггер устанавливается в нулевое состояние Тем самым устройство переводится в рабочий режим, т.е. режим реализа ции микропрограммы. При этом единичньм сигналом с вы хода 61 триггера 33 режима работы разрешается работа блока 32 синхрон зации в рабочем режиме, выдача результата сравнения рабочего адреса Ар-, (т.е. адреса микрокоманды, подлежащей реализации), с контрольным адресом , (т.е. адресом микрокоманды, подлежащей контролю в следующем контрольном такте), на выход 42 блока 8 сравнения, вьщача информации блоком 18 формирования микроопераций и формирователем 13 адреса. Кроме того, открывается блок 9 для передачи рабочего адреса Api + 1 из регистра 7 на вход блока 12 и вход блока 8 сравнения. Нулевым сигналом с выхода 60 три гера 33 режима работы запрещается 15 работа блока 17 контроля и закрыва-ется блок 10, в результате чего запрещается поступление контрольного адреса А((т,е. адреса, по которо-му считывается для контроля очередная микрокоманда) из счетчика 4 на адресный вход блока 12 памяти и вход блока 8 сравнения. При поступлении тактового импульса рабочей частоты с выхода 59 блока 32 синхронизации через элемент ИЛИ 3 на тактовьгй вход 43 блока 12 происходит считывание микрокоманды, начиная с которой продолжается реализация микропрограммы Адрес этой микропрограммы поступает на адресный вход блока 12 памяти из регистра 7 адреса через блок 9. Считанная микрокоманда записывается в регистр 14. Содержимое поля 15 управления регистра 14 подается на информационный вход блока 18 формирования микроопераций, так как сигналом с выхода 60 триггера 33 разрешается вьщача информации на выходы 49 - 53 блока 18 (фиг. 3), то с выхода 21 микроопераций микрокоманды сигналы микроопераций вьщаются на выход 51 устройства для реализации их объектом управления. Содержимое поля 16 адреса и логических условий регистра 14 поступает на информационный вход формирователя 13 адреса, где с учетом значения проверяемых логических условий, подаваемых на вход 45 устройства, формируется адрес Ар-+1 микрокоманды, подлежащей реализации в следукяцем рабочем такте . Сформированньй адрес записывается в регистр 7, с выхода которого поступает на адресный вход блока 12 и информационный вход блока 8 сравнения. В блоке 8 сравнения сформированный рабочий адрес Ар;+1 сравнивается с контрольным адресом А, поступающим с выхода 37 счетчика 4. Если в результате сравнения оказывается, что очередная микрокоманда, подлежащая реализации, является проверенной, т.е. выполняется неравенствоApi., - . то эта микрокоманда по приходу очередного тактового импульса рабочей частоты считывается из блока 12 для реализации. Устройство работает аналогично описанному. 251 Если же в результате сравнения гадресов оказывается, что очередная микрокоманда, подлежащая реализации, еще не проверялась т.е, выполняется неравенство ТО на выходе 42 блока 8 сформируется сигнал, по которому через элемент ИЛИ 25 и элемент задержки 27 устанавливается в единичное состояние триггер 33. Тем самым устройство переводится в описанный режим принудительного контроля, которому соответствует нулевое и единичное состоя ния триггеров 26 и 33 соответственно При этом тем же сигналом через элемент ИЛИ 24 и элемент задержки 30 открывается блок 1 элементов И, в результате чего в счетчик 4 из регистра 7 записьгоается адрес Ар i.i очередной микрокоманды, подлежащей реализации и являющейся непроверенной. С этой микрокоманды и начинается дальнейший контроль микрокоманд. Этим достигается избирательность контроля микрокоманд, так как запись нового рабочего адреса из регистра 7 в счетчик 4 по сигналу с выхода блока 8 сравнения позволяет исключить из числа проверяемых те микрокоманды которые не входят в реализуемую ветв микропрограммыi Далее устройство раб тает в режиме принудительного контро ля так же, как в начале реализации микропрограммы. Если в процессе принудительного контроля в счетчике 4 устанавливается максимально возможное значение адреса, определяемое верхней границе области используемых ячеек памяти, то на выходе элемента И 5 появляется сигнал, который, поступая на вход останова 36 счеТчик 4, запрещает подсчет тактовых импульсов контрольной частоты, поступающих на его счет ный вход 35. .Тем самым исключается повторная проверка уже проверенных и реализованных микрокоманд из-за об нуления счетчика 4, в результате пере полнения. Кроме того, меткой Конец участка, которая обязательно проставляется в соответствующей зоне микро команды, имеющей максимально возможное значение адреса, устройство переводится в рабочий режим как описано. Если в рабочем режиме в микрокоманде, подлежащей реализации и запиiсанной в регистре 14, оказывается 1526 метка Начало ожиданття, то на выходе 52 блока 18 формирования микро,операций появляется сигнал, которым триггер 26 режима естественного ожидания устанавливается в единичное состояние. Тем же сигналом через элемент ИЛИ 25 и элемент задержки 27 устанавливается в единичное состояние триггер 33. Время задержки этого сигнала определяется соотношениемv - 2т 2Ь где - длительность срабатывания триггера 26. Задержка сигнала на время позволяет исключить подачу сигнала метки Начало ожрщания на нулевые входы триггеров 33 и 26 с выхода 53 блока 18 формирования микроопераций через элементы 28 и 31, так как к моменту появления единичного сигнала на выходе 60 триггера 33 элемент И 28 закрьгоается нулевым сигналом с нулевого выхода триггера 26. I С переходом триггера 26 и 33 в единичное состояние устройство переходит в режим контроля в состояние естественного ожидания. Переход в этот режим и функционирование в нем осуществляется так же, как и в режиме принудительного контроля, с отличием в том, что нулевым сигналом с нулевого выхода триггера 26 закрывается элемент И 28, вследствие чего запрещается прохождение сигналов меток Начало ожидания или Конец участка с выхода 53 блока 18 на нулевой вход триггера 33. Тем самым исключается перевод устройства из режима контроля в состоянии естественного ожидания в рабочий режим до окончания естественного ожидания. Кроме того, если в процессе контроля в состоянии естественного ожидания .в счетчике 4 устанавливается максимально возможное значение адреса микрокоманды, то на выходе элемента И 5 появляется единичный сигнал, который, поступая через элемент НЕ 6 на вход 36 счетчика 4, запрещает подсчет тактовых импульсов контрольной частоты, поступающих на его счетный вход 35, в результате чего до окончания режима контроля в состоянии естественного ожидания в каждом такте проверяется микрокоманда, имеющая максимальный возможный адрес. Этим исключается повторная проверка (Е ре.4yjTbTaTP обчу.челгия счетчика при его переполнении) ууке проверенных мккрсукоманд.

Перевод устройства пз режима контроля в состоянии естественного ожидания в рабочий режим осуществляется по сигналу Конец ожидания. Он формируется либо объектом управления по окончании выполнения микрокоманды, либо таймером, задающим время вьтолнения микрокоманды объектом управления. Сигнапом Конец ожидания, поступающим на вход 54 устройства, через элемент ИЛИ 31 устанавливаются в нулевое состояние триггеры 26 и 33, вследствие чего устройство переводится в рабочий режим.

Если в процессе реализации микропрограммы в рабочем режиме из блока 12 памяти считывается микрокоманда, содержащая метку Замыкание цикла, то сигналом с выхода 50 блока 18 формирования микроопераций через элемент ИЛИ 24 и элемент 30 задержки открывается блок 1 элементов И, вследствие чего в счетчик 4 из регистра 7 адреса записывается адрес Ар микрокоманды, подлежащей реализации в следукяцем рабочем такте Время ТЗР задержки элемента 30 определяется временем формирования адреса Ар.очередной микрокоманды, к выполнению которой необходимо перейти, и временем т

ег-о зячисп в регистр адреса 7 ,в

го

Запись нового рабочего адреса из регистра 7 в счетчик U по метке Замыкание цикла позволяет возобновить контроль микрокоманд, начиная с той, которая задается этим адресом, и за счет этого избежать реализации непроверенных микрокоманд в процессе дальнейшего выполнения микропрограммы. Очевидно, что по окончании реализации микрокоманды, Помеченной указанной меткой по сигналу с выхода 42 блока 8, устройство переходит

в режим принудительного контроля.

Если в рабочем режиме из блока 12 памяти в регистр 14 микрокоманд считывается для реализации микрокоманда, содержащая метку Конец микропрограммы, то на выходе 49 блока 18

формирователя микроопераций появляется сигнал, который, поступая через элемент ИЛИ 29 на вход останова 56 блока 32 синхронизации, запрещает

вьщачу им тактовых импульсов. Устройство прекращает работу.

Таким образом, изобретение является более надежным, чем известное устройство, так как устраняется возможность вьщачи потребителю недостоверных (непроверенных) микрокомавд.

Повьппение быстродействия достигается путем исключения из контроля микрокоманд, не участвуюп1их в данный момент в вычислительном процессе.

( 5s

е61 7

ФигА

39

& 76

45

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для дифференцирования широтно-модулированных сигналов | 1975 |

|

SU543949A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-23—Публикация

1983-02-08—Подача