Изобретение относится к авТомати ке и вычислительной технике и может быть использовано при реализации средства тестового диагностирования блоков дискретной техники.

Цель изобретения - повьшение достоверности контроля путем обеспечения проверки цепей блокировки младших разрядов старшими.

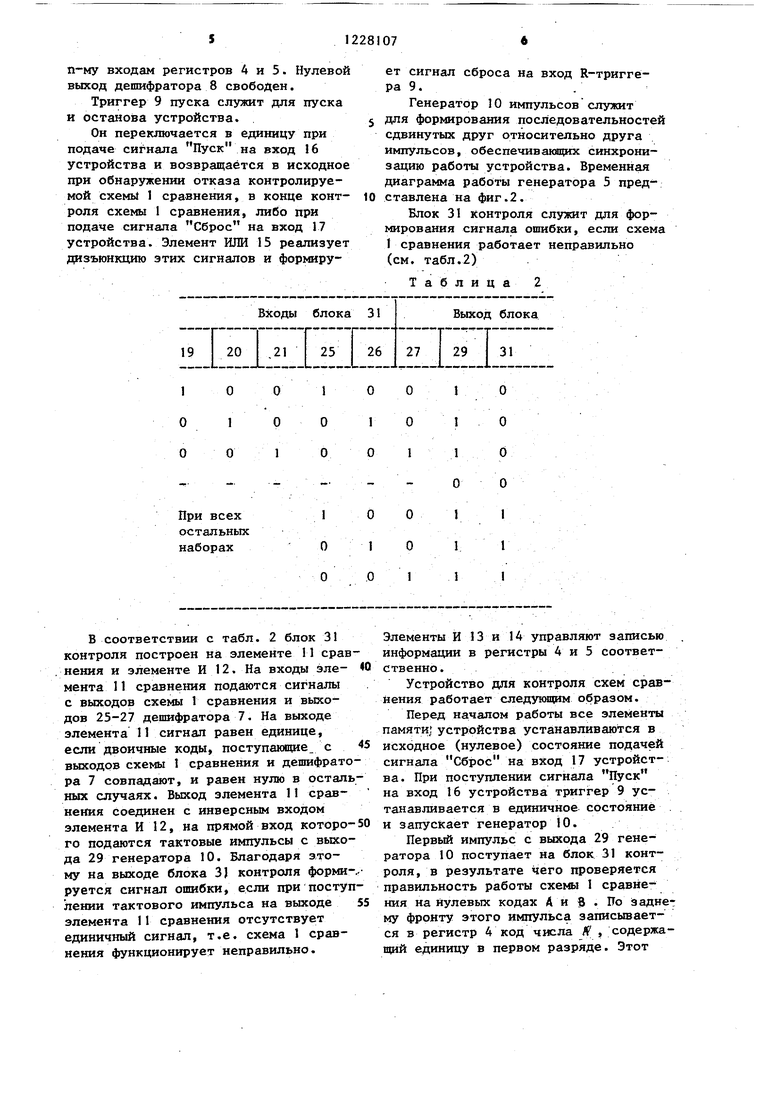

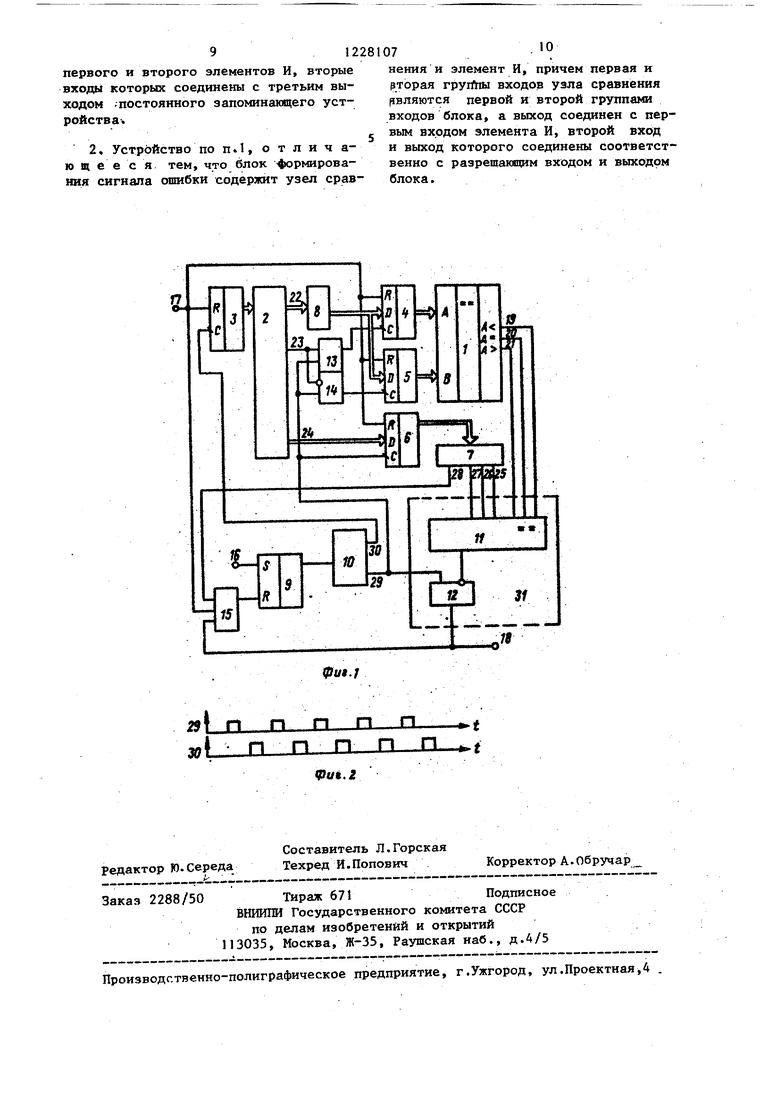

Устройство для контроля схем сравнения (фиг.1) содержит схему 1 сравнения, постоянный запоминающий блок

2281072

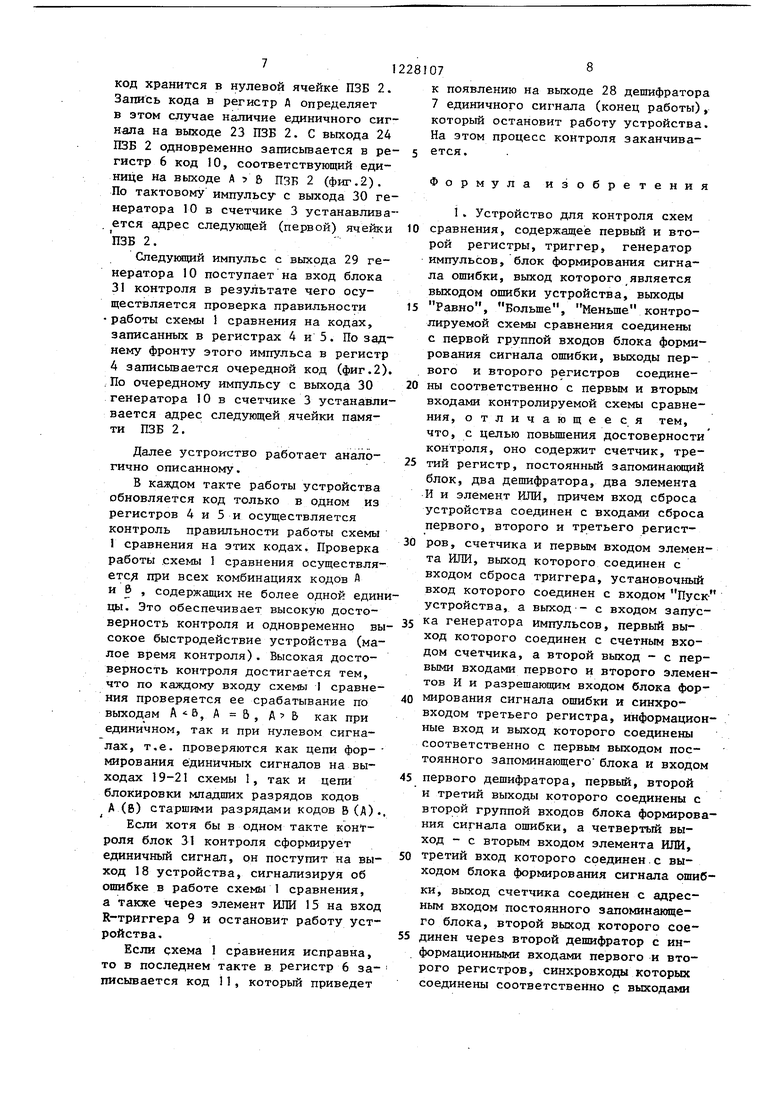

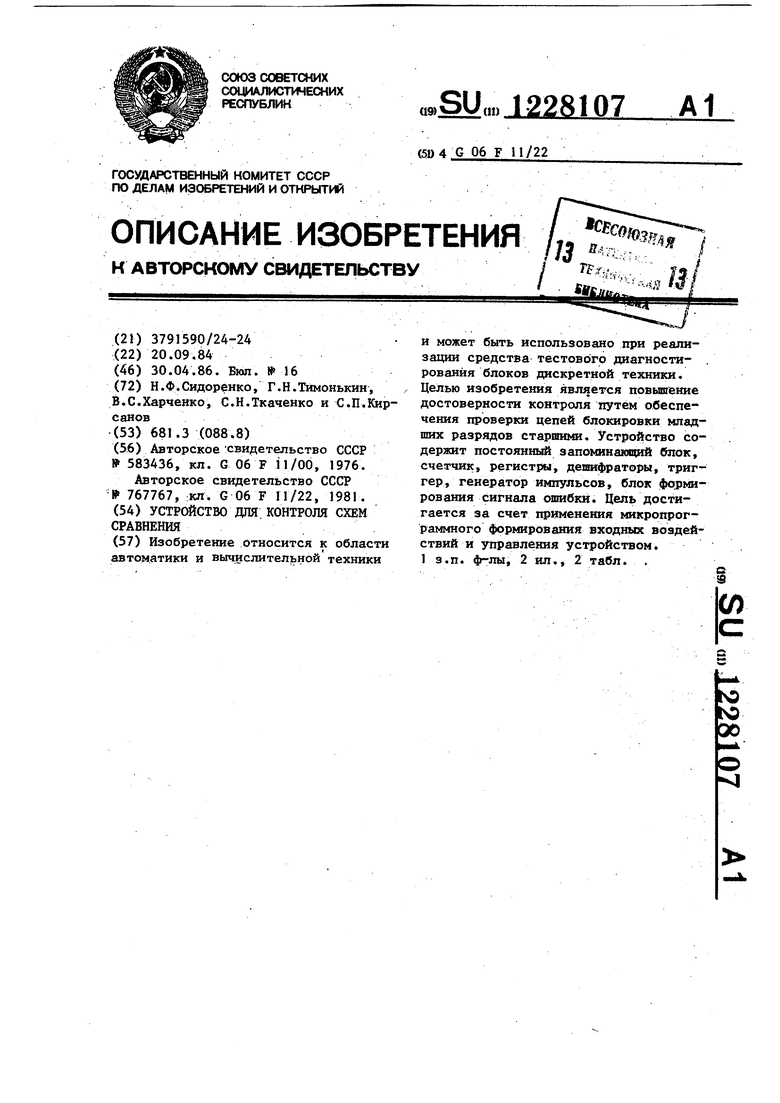

На фиг. 1 изображена функциональная схема предлагаемого устройства для контроля схем сравнения; на фиг. 2 - временная диаграмма импуль- 5 сов, формируемых генератором.

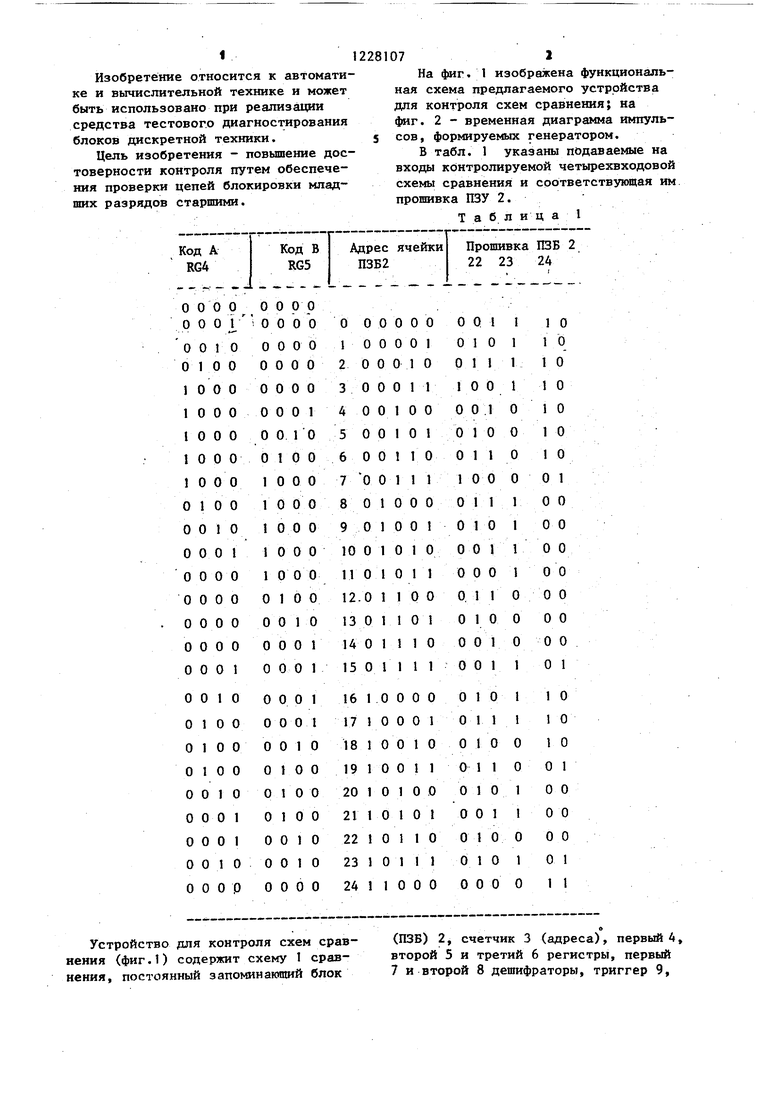

В табл. 1 указаны подаваемые на входы контролируемой четырехвходовой схемы сравнения и соответствующая им прошивка ПЗУ 2.

Т а б л и ц а I

(ПЗБ) 2, счетчик 3 (адреса), первый 4, второй 5 и третий 6 регистры, первый 7 и второй 8 дешифраторы, триггер 9,

генератор 10 импульсов, блок формирования сигнала ошибки, содержащий элемент 11 сравнения и элемент И 12, первьй 13 и второй 14 элементы И, элемент ИЛИ 15. Кроме того, устройство содержит входы 16 и 17 пуска и сброса устройства, выход 18 ошибки устройства, выходы 19-21 Меньше Равно и Больше схемы 1 сравнения второй, третий, первый выходы 22-24 ПЗУ 2, выходы 25-28 дешифратора 7, второй и первый выходы генератора 10 импульсов, блок 31 формирования сигнала ошибки.

Рассмотрим назначение элементов .предлагаемого устройства для контроля схем сравнения.

Схема I сравнения является объектом контроля. Она предназначена для .сравнения п-разрядных двоичных чисел ,и формирования rto результатам сравнения одного из трех возможных сигналов: А Б -на выходе 19, А 6 - на выходе 20 или А В - на выходе 2I. При правильной работе схемы 1 сравнения иа ее выходах должен присутствовать один и только один еди- :ничный сигнал.

Постоянный запоминающий блок (ПЗБ) 2 предназначен для хранения кодов микрокоманд, обеспечивающих проверку схемы. 1 сравнения, информация ПЗБ 2 представляет собой ПЗБ статичекого типа, т.е. информация на его выходах соответствует той ячейке памяти, адрес которой присутствует на входе ПЗБ 2, и держится на выходе до тех пор, пока на вход ПЗБ 2 подаеся соответствующий ей адрес. Микрокоманды, хранящиеся в ПЗБ 2, содержат каждая номер единичного разряда кода А и В (считьшается на выходе 22 ПЗБ 2), разряд.управляющий запись информации в регистры 4 или 5 (считывается на выходе 23 ПЗБ 2) и номер выхода схемы 1 сравнения, на котором должен присутствовать единичный сигнал в данном такте контроля, либо код конца работы устройства (считывается на выходе 24 ПЗБ 2). Для микрокоманд, хранящихся в ПЗБ 2, принято следуннцее кодирование. Нулевой код на выходе ПЗБ 2 соответствует нулевому коду регистра А (6), код 00....01 -коду 00....01 регистра А

(В), код 00010 - коду П. ...010,

код 00011 - коду 000100 и

т.д. Дпя кодов на выходе 24 ПЗБ 2 принято следующее соответствие:

Код 00Выход ПЗБ 2, А В Код 01 , А В Код 10 , А В

Код 11Конец работы устройства

Счетчик 3 адреса служит для формирования, хранения и вьщачи адреса очередной микрокоманды, считываемой из ПЗБ 2. Он представляет собой двоичный суммирукиций счетчик, изменения состояний которого происходят по заднему фронту тактовых импульсов, поступающих на его счетный вход. Установка счетчика 3 в исходное состояние происходит при подаче

на его вход R импульса сброса, который поступает на вход 17 сброса устройства.

Регистры 4 и 5 служат для приема, хранения и вьщачи кодов А и Б соот-

ветственно, подаваемых на входы схемы 1 сравнения при контроле. Запись информации в регистры 4 и 5 осуществляется по заднему фронту синхроимпульсов, поступающих на входы С..

Сброс регистров 4 и 5 в ноль осуществляется по сигналу, подаваемому на вход R.

Регистр 6 предназначен для приема, хранения и записи номера выхода

схемы 1 cpaвнeнияJ на которо должен быть единичный сигнал в данном такте контроля, либо кода конца работы устройства. Запись осуществляется по заднему фронту Импульса, поступаю

щего на вход С , а сброс регистра 6 - при постуштении KMnyjjbca на вход R.

Дешифратор 7 предназначен для дешифрации кодов номера выхода схемы 1 сравнения, на котором в данном

такте контроля должен присутствовать единичный сигнал, либо кода конца работы устройства. На вход дешифратора 7 подается двухразрядный двоичный код с выхода 21 ПЗБ 2. При

коде 00 единица присутствует на выходе 24, при коде 01 - на выходе 25, при коде 10 - на выходе 26 и при коде II - на выходе 27 дешифратора 7. Дешифратор 8. служит для де.шифрации номера раз ряда кода А или В , который должен быть равен единице. Первый - п-й выходы дешифратора 8 подключены соответственно к первому n-му входам регистров 4 и 5. Нулевой выход дешифратора 8 свободен.

Триггер 9 пуска служит для пуска и останова устройства.

Он переключается в единицу при подаче сигнала Пуск на вход 16 устройства и возвращается в исходное при обнаружении отказа контролируемой схемы 1 сравнения, в конце контроля схемы 1 сравнения, либо при подаче сигнала Сброс на вход 17 устройства. Элемент ИЛИ 15 реализует дизъюнкцию этих сигналов и формируВ соответствии с табл. 2 блок 31 контроля построен на элементе 11 сравнения и элементе И 12. На входы эле- 0 мента 11 сравнения подаются сигналы с выходов схемы 1 сравнения и выходов 25-27 дешифратора 7. На выходе элемента II сигнал равен единице, если двоичные коды, поступающие, с 45 выходов схемы 1 сравнения и дешифратора 7 совпадают, и равен нулю в остальных случаях. Выход элемента 11 сравнения соединен с инверсным входом элемента И 12, на прямой вход которо-50 го подаются тактовые импульсы с выхода 29 генератора 10. Благодаря этому на выходе блока 3J контроля форми-.-- руется сигнал ошибки, если при поступлении тактового импульса на выходе 55 элемента 11 сравнения отсутствует единичный сигнал, т.е. схема 1 сравнения функционирует неправильно.

ет сигнал сброса на вход R-тригге- ра 9.

Генератор 10 импульсов служит для формирования последовательностей сдвинутых друг относительно друга импульсов, обеспечивающих синхронизацию работы устройства. Временная диаграмма работы генератора 5 пред- ставлена на фиг.2.

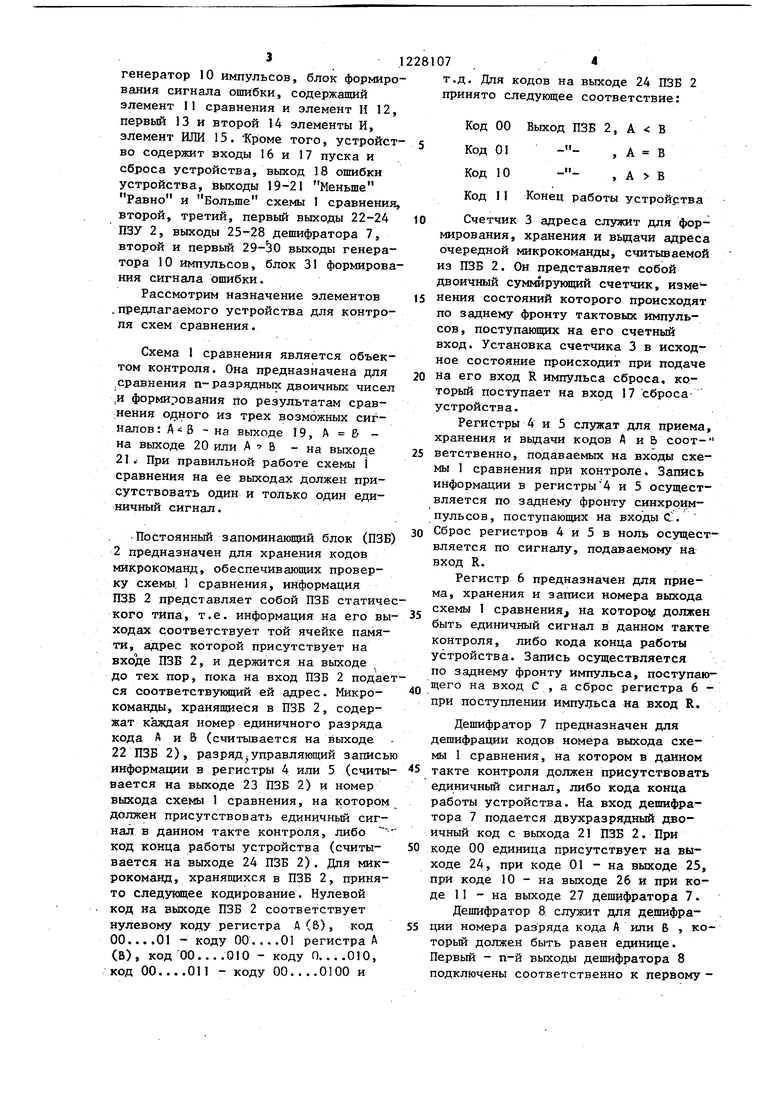

Блок 31 Контроля служит для формирования сигнала ошибки, если схема 1 сравнения работает неправильно (см. табл.2)

Таблица 2

Элементы И 13 и 14 управляют записью информации в регистры 4 и 5 соответственно.

Устройство для контроля схем сравнения работает следующим образом.

Перед началом работы все элементы памяти} устройства устанавливаются в исходное (нулевое) состояние подачей сигнала Сброс на вход 17 устройства. При поступлении сигнала Пуск на вход 16 устройства триггер 9 устанавливается в единичное состояние и запускает генератор 10.

Первый импульс с выхода 29 генератора 10 поступает на блок 31 контроля, в результате чего проверяется правильность работы схемы 1 сравнения на Нулевых кодах Аи 8 . По аадне му фронту этого импульса записывается в регистр 4 код числа К , содержащий единицу в первом разряде. Этот

712281

од хранится в нулевой ячейке ПЗБ 2. апись кода в регистр Д определяет этом случае наличие единичного сигала на выходе 23 ПЗБ 2. С выхода 24 ЗБ 2 одновременно записьгаается в ре- s гистр 6 код 10, соответствующий едиице на выходе А В ПЗБ 2 (фиг.2). о тактовому импульсу с выхода 30 геератора 10 в счетчике 3 устанавливатся адрес следующей (первой) ячейки 10 ЗБ 2.

Следукяций импульс с выхода 29 генератора 10 поступает на вход блока 31 контроля в результате чего осуществляется проверка правильности 15 работы схемы 1 сравнения на кодах, записанных в регистрах 4 и 5. По заднему фронту этого импульса в регистр 4 записьюается очередной код (фиг.2). По очередному импульсу с выхода 30 20 генератора IО в счетчике 3 устанавливается адрес следующей ячейки памяти ПЗБ 2,

Далее устройство работает анало- 25 гично описанному.

В каждом такте работы устройства обновляется код только в одном из регистров 4 и 5 и осуществляется контроль правильности работы схемы 1 сравнения на этих кодах. Проверка работы схемы 1 сравнения осуществля- етсд при всех комбинациях кодов А и В , содержащих не более одной единицы. Это обеспечивает высокую достоверность контроля и одновременно вы- 5 сокое быстродействие устройства (малое время контроля). Высокая достоверность контроля достигается тем, что по каждому входу схемы I сравнения проверяется ее срабатывание по выходам А- В, А &, А & как при единичном, так и при нулевом сигналах, т.е. проверяются как цепи фор- мирования единичных сигналов на выходах 19-21 схемы 1, так и цепи блокировки младших разрядов кодов А (в) старшими разрядами кодов Б (Л)..

Если хотя бы в одном такте контроля блок 31 контроля сформирует единичный сигнал, он поступит на вы- ход 18 устройства, сигнализируя об ошибке в работе схемы 1 сравнения, а также через элемент ИЛИ 15 на вход R-триггера 9 и остановит работу устройства.55

Если схема 1 сравнения исправна, то в последнем такте в регистр 6 за- письшается код 11, который приведет

30

45

07°

к появлению на выходе 28 дешифратора 7 единичного сигнала (конец работы), который остановит работу устройства. На этом процесс контроля заканчивается.

Формула изобретения

1. Устройство для контроля схем сравнения, содержащее первый и второй регистры, триггер, генератор импульсов, блок формирования сигнала ошибки, выход которого является выходом ошибки устройства, выходы Равно, Больше, Меньше контролируемой схемы сравнения соединены с первой группой входов блока формирования сигнала ошибки, выходы первого и второго регистров соединены соответственно с первым и вторым входами контролируемой схемы сравнения, отличающееся тем, что, с целью повьщ1ения достоверности контроля, оно содержит счетчик, третий регистр, постоянный запоминающий блок, два дешифратора, два элемента И и элемент ИЛИ, причем вход сброса устройства соединен с входами сброса первого, второго и третьего регистров, счетчика и первым входом элемента ИЛИ, выход которого соединен с входом сброса триггера, установочный вход которого соединен с входом Пуск- устройства, а выход - с входом запуска генератора импульсов, первый выход которого соединен с счетным входом счетчика, а второй выход - с первыми входами первого и второго элементов И и разрешакяцим входом блока формирования сигнала ошибки и синхро- входом третьего регистра, информационные вход и выход которого соединены соответственно с первым выходом постоянного запоминающего блока и входом первого дешифратора, первый, второй и третий выходы которого соединены с второй группой входов блока формирования сигнала ошибки, а четвертый выход - с вторым входом элемента ИЛИ, третий вход которого соединен.с выходом блока формирования сигнала ошибки, выход счетчика соединен с адресным входом постоянного запоминающего блока, второй выход которого соединен через второй дешифратор с информационными входами первого и второго регистров, синхровходы которых соединены соответственно с выходами

первого и второго элементов И, вторые входы которых соединены с третьим выходом постоянного запоминающего устройства.

2, Устройство по п.1,отлича- ю щ е ее я тем, что блок Армирования сигнала ошибки содержит узел сравнения и элемент И, причем первая и рторая rpyiftnj входов узла сравнения рвляются первой и второй группами входов блока, а выход соединен с первым входом элемента И, второй вход и выход которого соединены соответственно с разрешаищим входом и выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программ и микропрограмм | 1983 |

|

SU1176334A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1651289A1 |

| Устройство для контроля управляющих сигналов микропроцессора | 1989 |

|

SU1656536A1 |

| Устройство для контроля резервированного генератора | 1980 |

|

SU907887A1 |

| Устройство для тестового диагностирования | 1982 |

|

SU1045230A1 |

| Устройство для измерения мощности | 1990 |

|

SU1751685A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

Изобретение Относится к области автоматики и вычислительной техники и может быть использовано при реализации средства тестового диагностирования блоков дискретной техники. Целью изобретения является повьшение достоверности контроля путём обеспечения проверки цепей блокировки младших разрядов старшюш. Устройство содержит постоянный запоминающий блок, счетчик, регистры, дешифраторы, триггер, генератор импульсов, блок формирования сигнала ошибки. Цель достигается за счет применения микропрограммного формирования входных воздействий и управления устройством. 1 з.п. ф-лы, 2 ил., 2 табл.

S-

gjot.f 29 f n n n n П t

n n n П П ..

Vuit.2

редактор Ю.Середа

Составитель Л.Горская Техред И.Попович

2288/50

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.А/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4 .

Корректор А.Обручар

| Устройство для проверки схем сравнения | 1976 |

|

SU583436A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля схем сравнения | 1978 |

|

SU767767A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-30—Публикация

1984-09-20—Подача