(54) УСТРОЙСТВО МАЖОРИТАРНОГО ДЕКОДИРОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| Устройство декодирования зеркальных кодов | 1982 |

|

SU1104685A1 |

| Мажоритарное декодирующее устройство | 1975 |

|

SU538502A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Декодер циклического кода с исправлением ошибок и стираний | 1980 |

|

SU1083387A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Устройство для коммутации сообщений | 1984 |

|

SU1247879A1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1983 |

|

SU1099397A2 |

Изобретение относится к техннке связи и может использоваться в устройствах для передачи цифровой информации.

Известно устройство мажоритарного декодирования, содержащее блок управления, выходы которого соответственно подключены к иервым входа.м буферного блока с обратными связями, блока ячеек памяти и выходного блока 1J ..

Однако такое устройство не обеспечивает достагочной точности декодироваиия.

Цель изобретения - повышение точности декодирования.

Для этого в с тройство мажоритарного декодироваиия, содержащее блок унравления, выходы которого соответственно подключены к первым входам буферного блока с обратны.ми связями, блока ячеек памяти и выходного блока, введены блок дешифраторов и дополнительный блок ячеек памяти, причем выходы буферного блока с обратными связями через последовательно соединенные блок ячеек памяти, блок деишфраторов и Д011оли11тельнь1 блок ячеек памяти подключены ко вторы,м входам блока ячеек памяти и выходного блока, при этом дополнительные вых()ды блока управления подключены к другим входам олока дешифраторов и.дополнительного блока ячеек памяти.

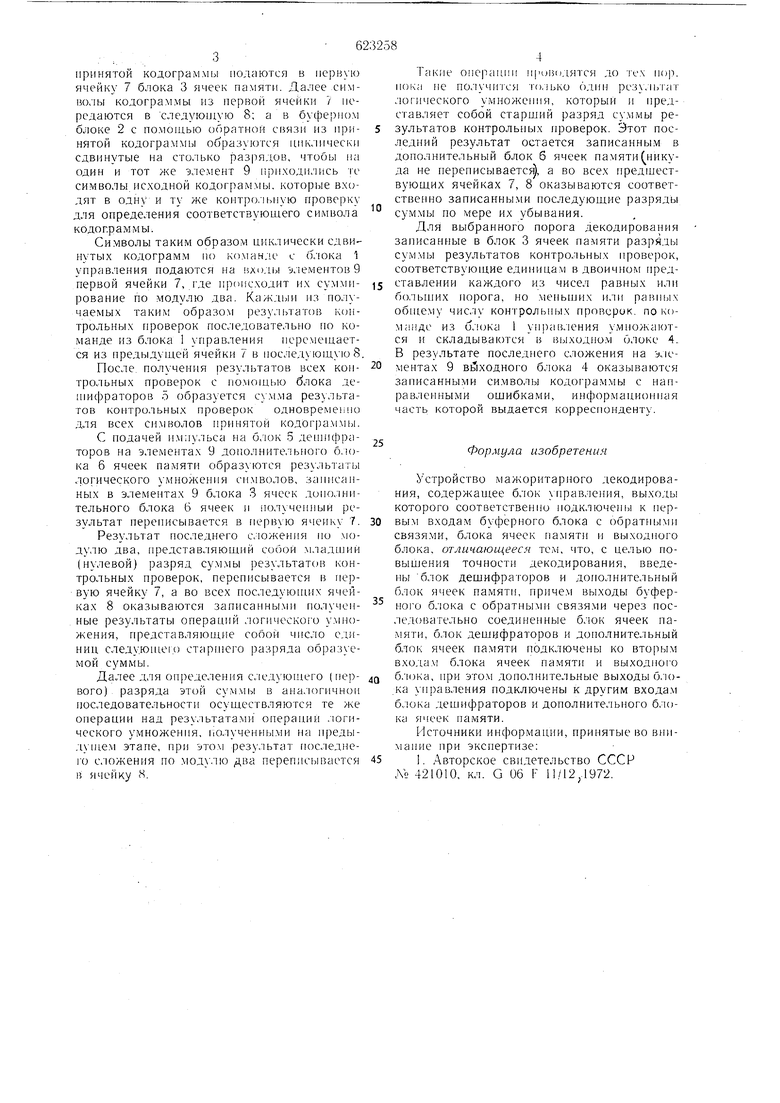

На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство мажоритарного декодирования содержит блок 1 управления, выходы которого соответственно подключены к первым входам буферного блока 2 с обратными связями, блока 3 ячеек памяти и выходного блока 4, а также блок 5 дешифраторов и дополнительный блок G ячеек памяти, причем выходы буферного блока 2 с обратными связями через последовательно соединенные блок 3 ячеек памяти, блок 5 дешифраторов и дополнительный блок b ячеек памяти подключены ко вторым вхолт ам блока 3 ячеек памяти и выходного блока 4, при этом дополнительные выходы бюка 1 управления подключены к другим входам блока 5 дешифраторов и дополнительного блока ,6 ячеек памяти.

Устройство работает следуюш,им образом.

Первоначально по команде блока 1 управления, из буферного блока 2 символы принятой кодограммы подаются в первую ячейку 7 блока 3 ячеек памяти. Далее символы кодограммы из первой ячейки 7 передаются в следуюи1ую 8; а в буферном блоке 2 с ПОМОИ1ЫО обратной связи пз примятой кодограммы образуются Ц1П лическп сдвинутые па столько разрядов, чтобы па один и тот же элемент 9 приходились те символы псходпой кодограммы. KOTOpi ie BXCJдят в одну и ту же коптро.-|ьпую проверку для определения соответствующего символа кодограммы. Символы таким образом циклически сдвинутых кодограмм по команде с б.юка 1 управления подаются на входы .1емептов9 первой ячейки 7, где происходит их суммированпе по модулю два. Каждьш из получаемых таким образом резу.ил атов К(Л1трольных проверок последовательно по команде из блока 1 управления иеремещается из предыдущей ячейки 7 в последующую 8 После, получения результатов всех контрольных проверок с помощью блока деН1ифраторов о образуется сумма результатов контрольных проверок одновремеипо для всех сп.мволов принятой кодогра.хпп;. С подачей импульса па блок 5 депп1фраторов па элементах 9 дополнительного блока 6 ячеек памяти образуются результаты логического умноженпя символов, записанных в элементах 9 блока 3 ячеек допол1-н1тельного блока 6 ячеек п по, ченныи результат переписывается в первую ячейку 7. Результат последнего c,Ioжe пIя по модулю два, представляющий собой м,пад1пиП (пулевой) разряд су.м.мы резуль татов контрольных проверок, переписывается в первую ячейку 7, а во всех последуюнио: ячейках 8 оказываются записапны.мп получеппые результаты операцпй логического умпожения, представляюп.и1е собой число единиц следуюн1е1.о cTapniero разряда образуемой суммы. Далее для онределення следуюн1его (первого) разряда этой суммы в апа.югпчноп последовательности осуществляются те же операции над результата.ми операции .югического умножения, полученными на предыдуп1ем этапе, при этом результат носледпеIo сложения по модулю два переписьп ается в ячейку . Такие операппп проводятся до тех пор. пока пе получится только 6л.пп .1Ыат .логического умножеппя, который и представляет собой старший разряд суммы результатов контрольпых проверок. Этот последний результат остается записанным в дополнительный блок б ячеек па.мятп(пикуда не переписывается), а во всех предшествующих ячейках 7, 8 оказываются соответствеппо записанны.ми последующие разряды сум.мы по мере их убывания. Для выбранного порога декодирования записанные в блок 3 ячеек памяти разрйды су.ммы результатов контрольных проверок, соответствующие единицам в двоичном представлении каждого из чисел равных пли болыиих иорога, но меиьщих или рави1)1х общему чис,|у коптролып:,1х проверок, по команде из бл(жа 1 упра лепия умпожаются и складываются в i lJIxoднo.i блоке 4. В результате последпего сложения на элементах 9 вйходного блока 4 оказываются записанными си.мволы кодограммы с направлеппыми ощибками, информационная часть которой выдается корреспонденту. Формула изобретения Устройство мажоритарного декодирования, содержащее блок управления, выходы которого соответствеппо подк,пючеп1)1 к первым входам буферпого блока с обратпымп связями, блока ячеек па.мяти и выходиого блока, отличающееся тем, что, с целью повышения точности декодирования, введеиы блок дешифраторов и дополнительный блок ячеек памяти, приче.м выходы буферHoio блока с обратными связями через последовательно соединенные блок ячеек памяти, блок дещифраторов и дополнительный блок ячеек памяти подключены ко вторым входам блока ячеек памяти и выходпого б.юка, прн это.м дополнительные выходы блока управления подключены к другим входам блока дешифраторов и дополнительпого блока ячеек памяти. Источники информации, принятые во внпмапне при экспертизе: 1. Авторское свидетельство СССР АО 421010, кл. G 06 F И/12,-1972.

Авторы

Даты

1978-09-05—Публикация

1976-07-27—Подача