(54) УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ; С ИСПРАВЛЕНИЕМ ПАКЕТНЫХ ОШИБОК

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство для исправления пакетных ошибок | 1985 |

|

SU1293845A1 |

| Устройство для исправления пакетов ошибок | 1975 |

|

SU562931A1 |

| СИСТЕМА ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 1991 |

|

RU2007042C1 |

| Кодирующее устройство линейного корректирующего кода | 1972 |

|

SU443389A1 |

| Устройство для преобразованиядВОичНОгО КОдА B избыТОчНыйциКличЕСКий КОд | 1978 |

|

SU798797A1 |

| Устройство защиты от ошибок внешней памяти | 1981 |

|

SU1018119A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Устройство обнаружения и исправления ошибок в кодах Рида-Соломона | 1986 |

|

SU1381719A1 |

| Устройство для кодирования линейных полиномиальных кодов | 1989 |

|

SU1711338A1 |

| Устройство для умножения по модулю 2 @ -1 @ | 1985 |

|

SU1304018A1 |

Изобретение относится к электронным дискретным устройствам автоматики, те-, лемеханики, вычислительной техн1гки и связи. Оно предназначено для использования в системах передачи и хранения дискретной информатши в качестве устройства для кодирования двоичной информации и исправлением пакетовошибок.

Известны устройства код1фования, используемые для борьбы с пакетными ошибками пЛ . Эти устройства содержат регистры сдвига, схемы сложения, схемы умножения.

Недостатком таких устройств является то, что их можно применять для ограниченных областей значений скорости передачи Т (т -отношение числа двоичных (№формационных символов, поступающих на вход кодирующего устройства, к. общему числу информационных и проверочных, передаваемых с выхода устройства в единицу времени) и параметров 5 и Ь где б - максимЬльная длина защитного интервала (двоичных символов), необходимого для исправления любого пакета

ощибок длины Ь двоичных символов или, меньше.;

Наиболее близким к пвнпому изобретению по технической сущности является устройство кодирования 2., содержшдве два блока регистров сдвига и два блока сумматоров по модулю два, выходы которых соединены соответственно со входами блоков регистров сдвига.

Недостатком этого устройства является ограниченность области его применени

Целью изобретения является расширение области применения i устройства за счет устранения жесткой связи мвжпу параметрами.

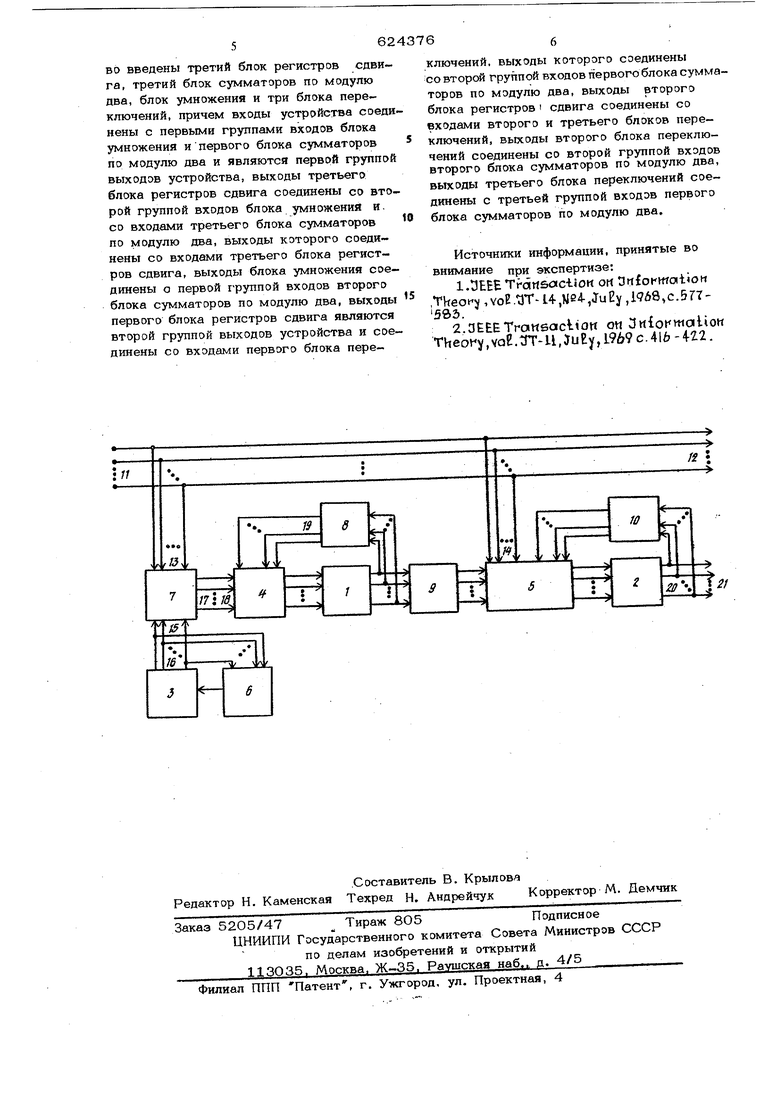

Это достигается тем, что в предлагаемое устройство введены третий блок, регистров сдвига, третий блок сумматоров по модулю два, блок умножения и три блока переключений,причем входы устройства соединены с первыми группами входов блока умножения и первого блока сумматоров по модулю два и являются первой группой выходов устройства, выходы третьего блока регистров сдвига соединены со второй группой входов блока умножения и со входами третьего блока сумматоров ПО модулю два, выходы которого . соепинены со входами третьего блока регистров сдвига, выходы блока умножения соединены впервой группой вхоцов второ ел t f tf rv тт ъ.л п-тк а гч,. блока (сумматоров по модулю два, выхо ды первого блока регистров сдвига являются второй группой выходов устройства и соединены со входами первого блока переключений, выходы которого соединены со второй группой входов первого блока сумматоров по модулю два, выходы второго блока регистров сдвига соедине ны со входами второго и третьего блоков переключений, выходы второго блока переключений соединеш 1 со второй группой входов второго блока сумматоров по модулю два, вькоды третьего блока переклю чений соединены.; с третьей группой входов первого блока сумматоров по модулю два. На чертеже показана блок-схема устройства. Устройство кодирования содержит три блока регистров сдвига 1, 2, 3, три блока сумматоров по модулю два 4, 5, 6, блок умножения 7, три блока переключений 8, 9, Ю. .Перед началом работы блоки переключений 8, 1О замкнуты (входы блока соедннены соответственно с выходами), блок переключений 9 разомкнут, блоки регист ров 1, 2, состоящие каждый из Hit-раз рядных регистров сдвига (, где fjjf- произвольные натуральные числа) содержат нули, блок регистров 3, содержащий ttt -разрядный регистр сдвига, находится в состоянии 1,0,.,,, О (одна единица и Ж-1 нулей). Далее, в течение К о тактов времени (KpSKglc ;С -произвольное натуральное число,) двоичные символы, подлежащиекодированию, посту: пают на W входов 11 устройства кодирования (по одному символу Б такт времени на каждый изш входов). СМ входов 11 информационные символы поступают на первую группу выходов 12, на первую группу входов 13 блока умножения, на первую группу входов 14 блока сумматоров 5, На BTOpjTo группу входов 15 блока умножения поступают сигналы с с выходов 16 блока регистров 3, Блок регистров 3 и блок сумматоров б функци нируют так, что в первые из этих Кд тактов времени на ш выходах 16 ПОЯБ ляется последовательность 1,О,..,,0 (одна единица иШ-1 нулей), в следующие тактов-последовательность, являющаяся щ . двоичными коэффициента 1и полиномаб2(х), (х)-остаток от приведения полинома р. (Х) )( по модулю р{ Ч ){р/х) -неприводимый полином степени ги с двоичными коэффициентами), следукшше тактовполинома6(х), остатка от приведения г, /х У по модулюр(х) , и т. д. На Ш . i«. ... выходах 17 блока умножения в j -и из этих KO тактод времени ( ) появляются W двоичных символов, коэффициентов полинома С j (х), гдеС;(() -остаток от пpивeдeнияdj (х) (х)б (х) по модулюр()() ,а(Х) -полином, rtt двоичными коэффициентами которого являются in двоичных символов информации, поступившие в этот такт на входы устройства кодирования. С выходов 17 сигналы поступают на входы 18 блока сумматоров по модулю два, где суммируются с сигналами, поступающими с выходов 19 блока переключений 8 и записываются далее в блок регистров 1, По истечении первых X g тактов времени блоки переключений 8, Ю размьпсаются, блок 9 замыкается и в течение rg последующих тактов символы информации на входы 11 не поступают, содержимое регистров блоков 1 и 2 сдвигается вправо на г разрядов,1(,iff двоичных символов (проверочные символы) поступают с выходов 2О на вторую группу выходов 21 устройства кодирования. По истечении этих Кд тактов времени регистр блока 3 снова принимает состояние 1,О, .,,,0 (одна единица и W -1 нулей), блоки 8, 1О замьпсаются, блок 9 размыкается. Снова в течение Kg тактов на входы 11 поступают информационные символы и т,д. Параметры К . Ь , И этого устройства равны (),b KoW-w+i, 2(г, Отношенией/Ь близко к (1+1)/(1-Т ), при этомТГ,Ь и не связаны между собой жесткой опально и связью, т,е. устройство имеет более щирокую область применения, чем прототип. Формула изобретения Устройство для кодирования с исправлением пакетных ошибок, содержащее два блока регистров сдвига и два блока сумматоров по модулю два, выходы которых соединены соответственно со входами блоков регистров сдвига, отличающееся тем, что, с целью расширения области применения, в устройст-

во введены третий блок регистров сдвига, третий блок сумматоров по модулю два, блок умножения и три блока переключений, причем входы устройства соединены с первыми группами входов блока умножения ипервого блока сумматоров по модулю два и являются первой группой выходов устройства, выходы третьего блока регистров сдвига соединены со второй группой входов блока умножения и. со входами третьего блока сумматоров по модулю два, выходы которого соединены со входами третьего блока регистров сдвига, выходы блока умножения соединены с первой группой входов второго блока сумматоров по модулю два, выходы первого блока регистров сдвига являются второй группой выходов устройства и соединены со входами первого блока переключений, выходы которого соединены со второй группой входов первого блока сумматоров по модулю два, выходы второго блока регистров сдвига соединены со входами второго и третьего блоков переключений, выходы второго блока переключений соединены со второй группой входов второго блока сумматоров по модулю два,

выходы третьего блока переключений соединены с третьей группой входов первого блока сумматоров по модулю два.

Источники информации, принятые во внимание при экспертизе:

l.tJEEETmtisactioM ort tJnfoHUToitiort

,,YoE.3T-L4,№4-,0u2y,W68,c.5n5в5.

Авторы

Даты

1978-09-15—Публикация

1976-11-16—Подача