1

Изобретение относится к технике связи и может.использоваться в системах передачи данных, информационный сигнал которых образован реккурентннми последовательностями.

Известно устройство для приема синхронизирующей реккурентной последовательности, содержащее последовательно соединенные блок умножения на порождающий полином, блок деления на порождающий полино.м и блок мажоритарной обработки {l Однако это устройство имеет большое время приема синхронизирующей реккурентной последовательности.

Цель изобретения - сокращение времени приема синхронизирующей реккурентной последовательности при наличии одиночных и двойных ошибок и при чередовании полярности импульсов входной последовательности.

Для этого в устройство для приема синхронизирующей реккурентной последовательности, содержащее последовател| но.соединенные блок умножения на порождающий полином, блок деления на порождающий полином и блок мажоритарной обработки, введены регистр сдвига, два блока обнаружения ошибок, два элемента ИЛИ, инвертор

и дешифратор нулевой последовательности, при этом выходблока умножения на поролодающий полином подключе ко входу регистра сдвига и к одному из входов первого блока обнаружения ошибок непосредственно и через инвертор - к одному из входов второго блока обнаружения ошибок, выходы которого через первый элемент ИЛИ подключены к единичному входу блока деления на порождающий полином, к нулевому входу, которого подключены выходы первого блока обнаружения ошибок через второй элемент ИЛИ, к соответствующему входу которого подключены дополнительные выходы блока умножения на порождающий полином через дешифратор нулевой последовательности, причем к другим входам первого и второго блоков обнаружения ошибок подключены соответственно ;Прямые:и инверсные выходы регистра сдвига.

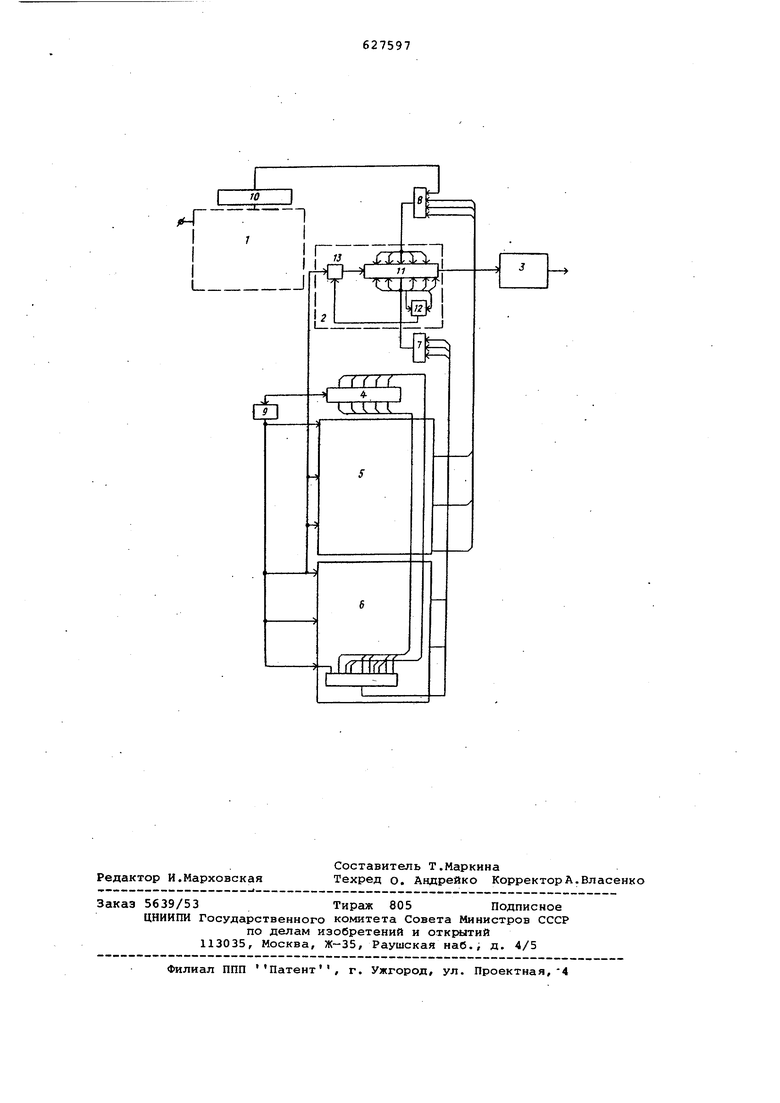

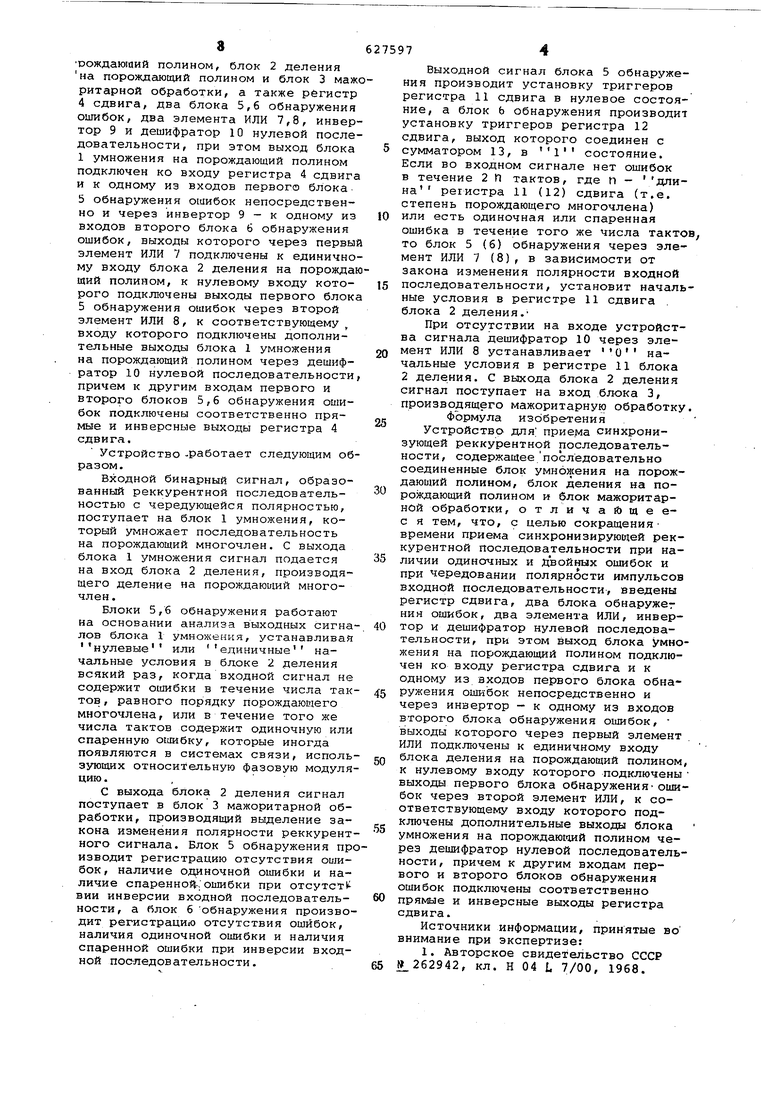

На чертеже изображена структурная электрическая схемапредложенного устройства.

Устройство для приема синхронизирующей реккурентной последовательности, содержащее последовательно соединенные блок 1 умножения на порождаюший полином, блок 2 деления на порождаюи;ий полином и блок 3 мажоритарной обработки/ а также регистр

4сдвига, два блока 5,6 обнаружения ошибок, два элемента ИЛИ 7,8, инвертор 9 и дешифратор 10 нулевой последовательности, при этом выход блока

1 умножения на порождающий полином подключен ко входу регистра 4 сдвига и к одному из входов первого блока

5обнаружения ошибок непосредственно и через инвертор 9 - к одному из входов второго блока 6 обнаружения ошибок, выходы которого через первый элемент ИЛИ 7 подключены к единичному входу блока 2 деления на порождающий полином, к нулевому входу которого подключены выходы первого блока 5 обнаружения ошибок через второй элемент ИЛИ 8, к соответствующему , входу которого подключены дополнительные выходы блока 1 умножения

на порождающий полином через дешифратор 10 нулевой последовательности, причем к другим входам первого и второго блоков 5,6 обнаружения ошибок подключены соответственно прямые и инверсные выходы регистра 4 сдвига.

Устройство -работает следующим образом.

Входной бинарный сигнал, образованный реккурентной последовательностью с чередующейся полярностью, поступает на блок 1 умножения, который умножает последовательность на порождающий многочлен. С выхода блока 1 умножения сигнал подается на вход блока 2 деления, производящего деление на порождающий многочлен.

Блоки 5,6 обнаружения работают на основании анализа выходных сигналов блока 1 умнохчения, устанавливая нулевые или единичные начальные условия в блоке 2 деления всякий раз, когда входной сигнал не содержит ошибки в течение числа тактов, равного порядку порождающего многочлена, или в течение того же числа тактов содержит одиночную или спаренную ошибку, которые иногда появляются в системах связи, использующих относительную фазовую модуляцию .

С выхода блока 2 деления сигнал поступает в блок 3 мажоритарной обработки, производящий выделение закона изменения полярности реккурентного сигнала. Блок 5 обнаружения производит регистрацию отсутствия ошибок, наличие одиночной ошибки и наличие спаренно} -ошибки при отсутст ВИИ инверсии входной последовательности, а блок 6 обнаружения производит регистрацию отсутствия ошибок, наличия одиночной ошибки и наличия спаренной ошибки при инверсии входной последовательности.

Выходной сигнал блока 5 обнаружения производит установку триггеров регистра 11 сдвига в нулевое состояние, а блок 6 обнаружения производит установку триггеров регистра 12 сдвига, выход которого соединен с сумматором 13, в состояние. Если во входном сигнале нет ошибок в течение 2 И тактов, где п - длирегистра 11 (12) сдвига (т.е.

на

степень порождающего многочлена) или есть одиночная или спаренная

ошибка в течение того же числа тактов, то блок 5 (6) обнаружения через элемент ИЛИ 7 (8), в зависимости от закона изменения полярности входной последовательности, установит начальные условия в регистре 11 сдвига . блока 2 деления.

При отсутствии на входе устройства сигнала дешифратор 10 через элемент ИЛИ 8 устанавливает О начальные условия в регистре 11 блока 2 деления. С выхода блока 2 деления сигнал поступает на вход блока 3, производящего мажоритарную обработку.

Формула изобретения Устройство для; приема синхронизующей реккурентной последовательности, содержащеепоследовательно соединенные блок умножения на порождающий полином, блок деления на порождающий полином и блок мажоритарной обработки, отличайте ес я тем, что, с целью сокращениявремени приема синхронизирующей реккурентной последовательности при наличии одиночных и двойных ошибок и при чередовании полярности импульсов входной последовательности, введены регистр сдвига, два блока обнаружат НИН ошибок, два элемента ИЛИ, инвертор и дешифратор нулевой последовательности, при этом выход блока умножения на порождающий полином подключен ко входу регистра сдвига и к одному из входов первого блока обнаружения ошибок непосредственно и через инвертор - к одному из входов второго блока обнаружения ошибок, выходы которого через первый элемент ИЛИ подключены к единичному входу блока деления на порождающий полином, к нулевому входу которого подключены выходы первого блока обнаружения-ошибок через второй элемент ИЛИ, к соответствующему входу которого подключены дополнительные выходы блока умножения на порождающий полином через дешифратор нулевой последовательности, причем к другим входам первого и второго блоков обнаружения ошибок подключены соответственно прямые и инверсные выходы регистра сдвига.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР №.262942, кл. Н 04 L 7/00, 1968.

to

п

Л

13

№-t

п

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемник синхронизирующей рекуррентной последовательности | 1982 |

|

SU1083391A1 |

| Способ выделения ошибок из испытательного псевдослучайного сигнала в виде м-последовательности и устройство для его осуществления | 1975 |

|

SU571917A1 |

| Устройство обнаружения расфазированияпРи пЕРЕдАчЕ иСпыТАТЕльНОй M-пОСлЕ-дОВАТЕльНОСТи | 1979 |

|

SU809612A1 |

| Устройство для обнаружения ошибок дискретного канала передачи информации | 1990 |

|

SU1777245A1 |

| СПОСОБ И ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ДВУХ ОШИБОК В ПРИНИМАЕМОМ КОДЕ | 2006 |

|

RU2336559C2 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| Корректор ошибок | 1989 |

|

SU1810909A1 |

| Устройство мажоритарного декодирования кода Рида-Соломона по k-элементным участкам кодовой комбинации | 2015 |

|

RU2613760C2 |

| Устройство для обмена информацией | 1982 |

|

SU1131035A1 |

| Декодер циклического кода с исправлением ошибок и стираний | 1980 |

|

SU1083387A1 |

f f f f (

L I I t. I

hrfMf

Авторы

Даты

1978-10-05—Публикация

1976-05-11—Подача