ч

ч|

VI

S3

fa

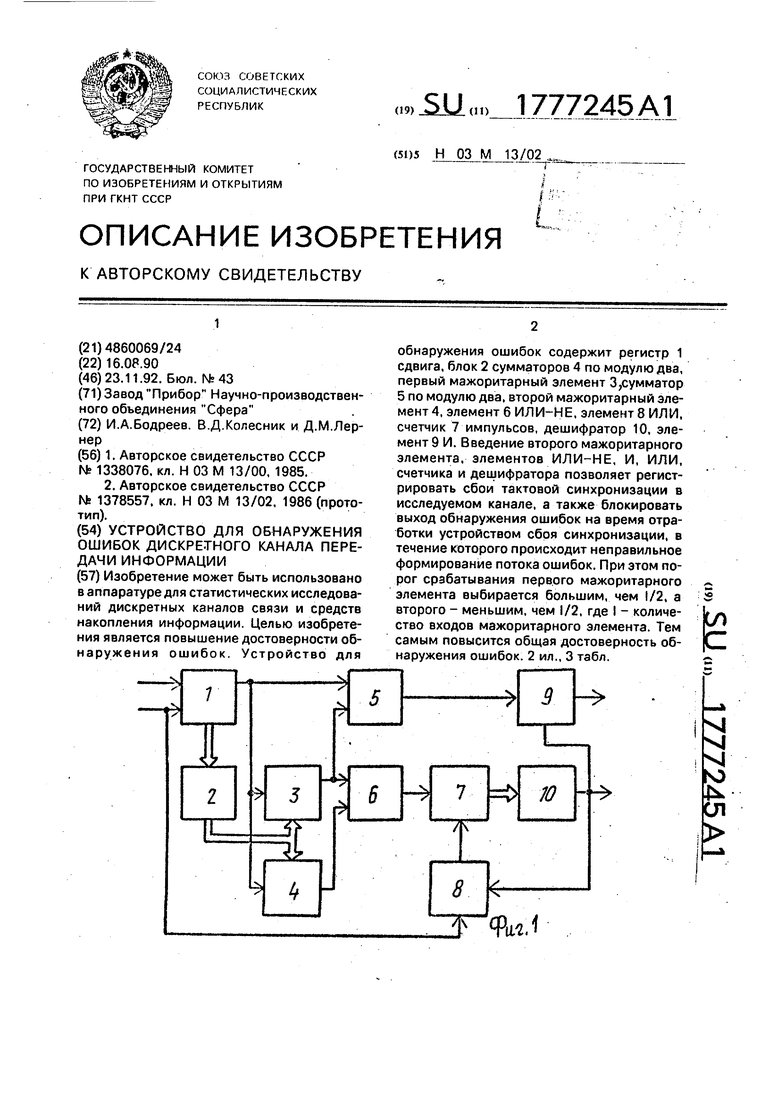

Изобретение относится к технике электросвязи и магнитной записи и может использоваться в аппаратуре для статистических исследований дискретных каналов связи и средств накопления инфор- мации.

Известно устройство для обнаружения и регистрации потока ошибок дискретного канала связи, содержащее блок обнаружения ошибок, регистр сдвига, 5лок ключей, схему ИЛИ, блок промежуточной памяти, блок управления и регистр 1.

Блок обнаружения ошибок данного устройства не позволяет определить сбой тактовой синхронизации в канале связи, что снижает достоверность обнаружения ошибок.

Из известных устройств наиболее близким к предлагаемому является устройство для обнаружения и регистрации ошибок ди- скретного канала передачи и накопления ошибок, содержащее блок обнаружения ошибок, регистр сдвига, элементы И, счетчики, блок промежуточной памяти, элемент ИЛИ, формирователь импульсов, регистра- тор и блок управления 2.

Однако данное устройство обладает недостаточной достоверностью обнаружения ошибок в связи с тем, что не позволяет регистрировать сбои тактовой синхронизации в исследуемом канале, проявляющиеся во вставке или выпадении символов в информационном потоке.

Целью изобретения является повышение достоверности обнаружения ошибок.

Указанная цель достигается тем, что в устройство для обнаружения ошибок дискретного канала передачи информации, содержащее регистр сдвига, элемент ИЛИ, элемент И и счетчик импульсов, введены блок сумматоров по модулю два, первый и второй мажоритарные элементы, элемент ИЛИ-НЕ. сумматор по модулю два и дешифратор, выход которого подключен к первым входам элемента И и элемента ИЛИ и явля- ется первым выходом устройства. Первый выход регистра сдвига подключен к первым входам первого и второго мажоритарных элементов и сумматора по модулю два, выход которого подкл ючен к второму входу элемента И, выход которого является вторым выходом устройства. Информационный вход регистра сдвига является информационным входом устройства, тактовый вход регистра сдвига объединен с вторым входом элемента ИЛИ и является тактовым входом устройства. Вторые выходы регистра сдвига подключены к соответствующим входам сумматоров по модулю два блока, выходы которых подключены соответственно к вторым входам первого и второго мажоритарных элементов, выход второго мажоритарного элемента подключен к первому входу элемента И Л И-НЕ, выход первого мажоритарного элемента подключен к вторым входам сумматора по модулю два и элемента ИЛ И-НЕ, выход которого подключен к входу сброса счетчика импульсов, счетный вход и выходы которого подключены соответственно к выходу элемента ИЛИ и входам дешифратора.

Введение блока сумматоров по модулю два, первого и второго мажоритарных элементов, элемента ИЛИ-НЕ, сумматора по модулю два и дешифратора позволяет регистрировать сбои тактовой синхронизации в исследуемом канале и, кроме того, блокировать выход обнаружения ошибок на время обработки устройством сбоя синхронизации, в течение которого происходит неправильное формирование потока ошибок. Таким образом повышается достоверность обнаружения ошибок.

Порог срабатывания первого мажоритарного элемента выбирается больше, чем I/2, а второго-меньше, чем I/2, где I - количество входов мажоритарного элемента.

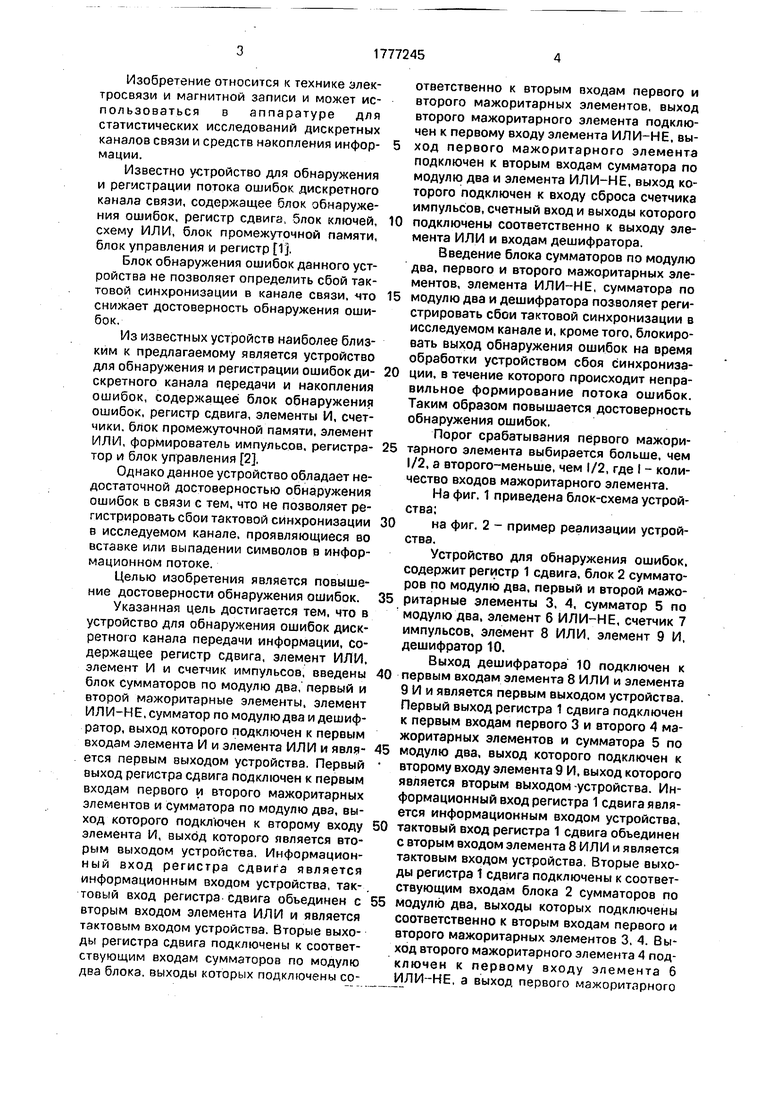

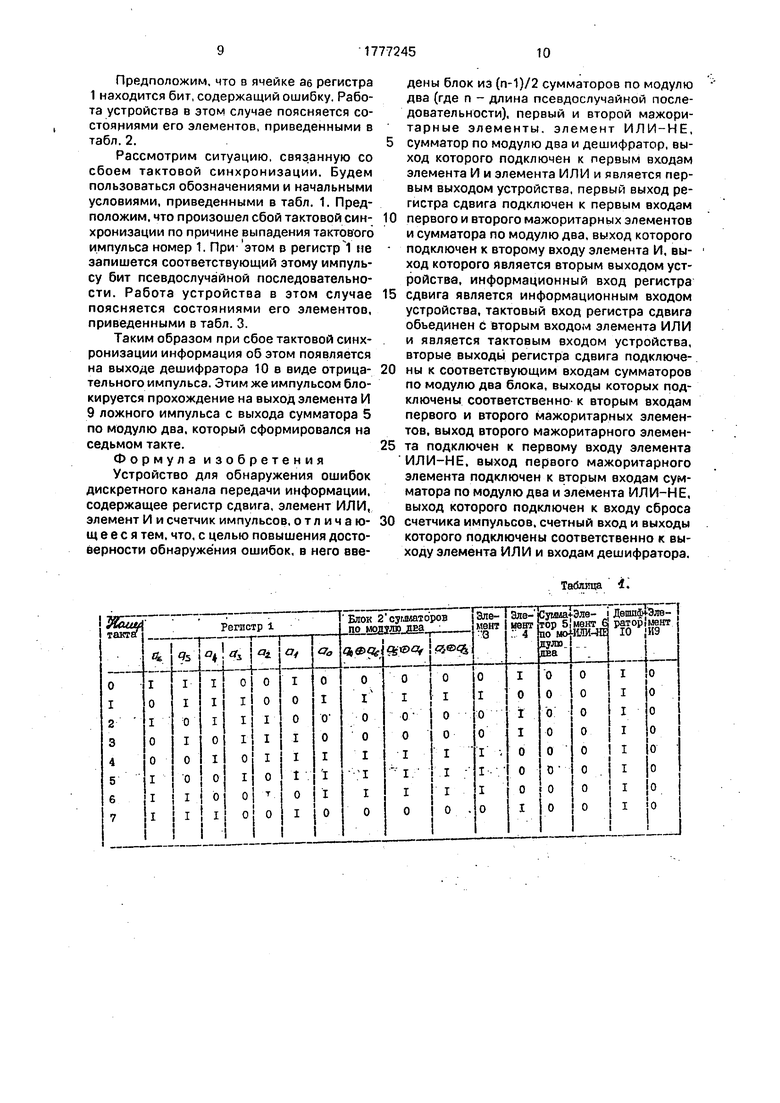

На фиг. 1 приведена блок-схема устройства;

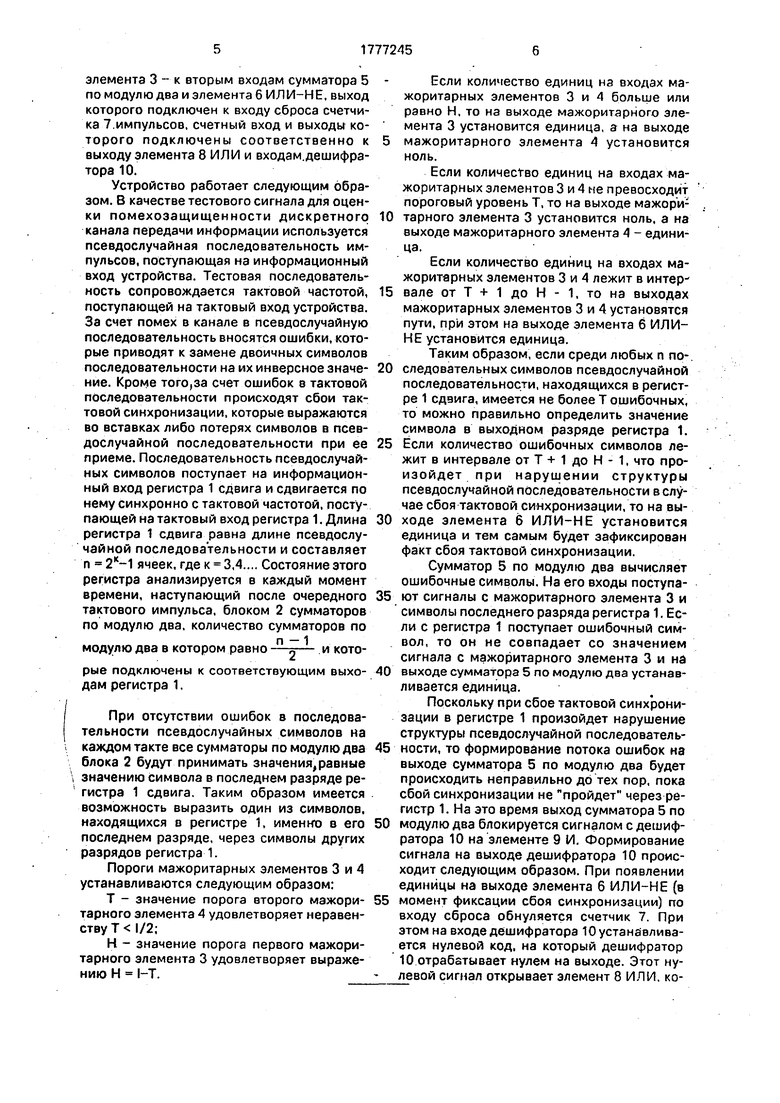

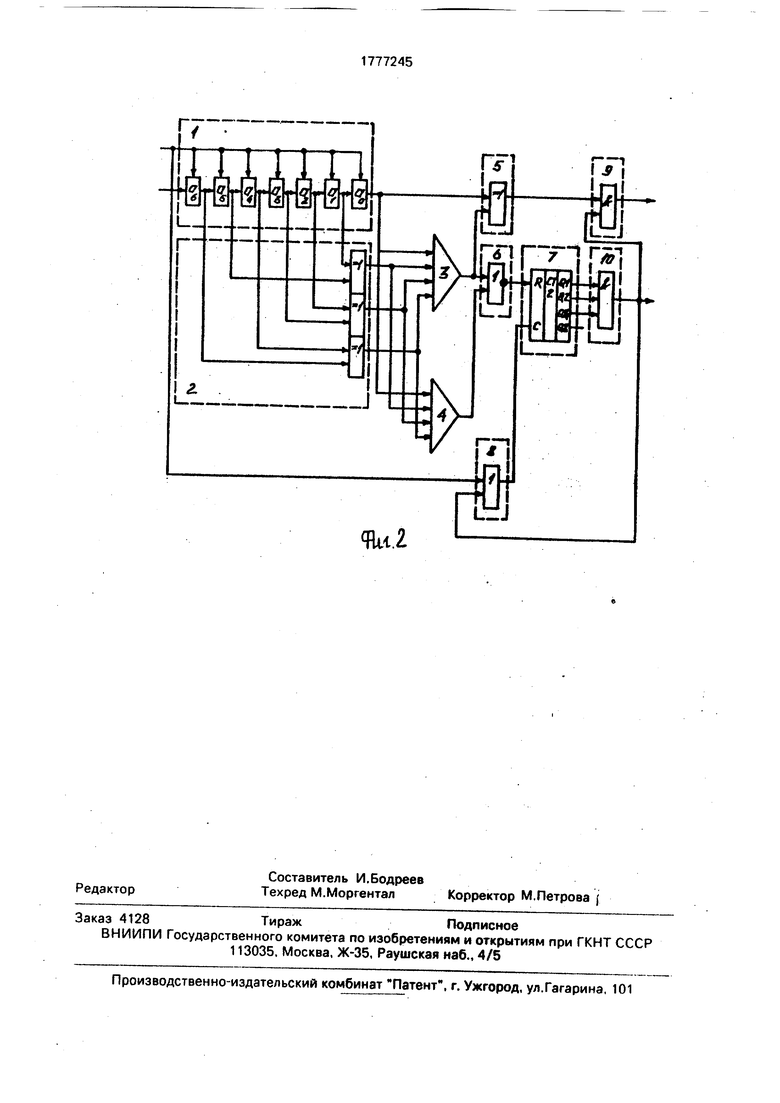

на фиг. 2 - пример реализации устройства.

Устройство для обнаружения ошибок, содержит регистр 1 сдвига, блок 2 сумматоров по модулю два, первый и второй мажоритарные элементы 3, 4, сумматор 5 по модулю два, элемент 6 ИЛИ-НЕ, счетчик 7 импульсов, элемент 8 ИЛИ, элемент 9 И, дешифратор 10.

Выход дешифратора 10 подключен к первым входам элемента 8 ИЛИ и элемента 9 И и является первым выходом устройства. Первый выход регистра 1 сдвига подключен к первым входам первого 3 и второго 4 мажоритарных элементов и сумматора 5 по модулю два, выход которого подключен к второму входу элемента 9 И. выход которого является вторым выходом -устройства. Информационный вход регистра 1 сдвига является информационным входом устройства, тактовый вход регистра 1 сдвига объединен с вторым входом элемента 8 ИЛИ и является тактовым входом устройства. Вторые выходы регистра 1 сдвига подключены к соответствующим входам блока 2 сумматоров по модулю два, выходы которых подключены соответственно к вторым входам первого и второго мажоритарных элементов 3, 4. Выход второго мажоритарного элемента 4 подключен к первому входу элемента 6 ИЛИ-НЕ, а выход первого мажоритарного

элемента 3 - к вторым входам сумматора 5 по модулю два и элемента 6 ИЛ И-НЕ, выход которого подключен к входу сброса счетчика 7.импульсов, счетный вход и выходы которого подключены соответственно к выходу элемента 8 ИЛИ и входам.дешифра- тора 10.

Устройство работает следующим образом. В качестве тестового сигнала для оценки помехозащищенности дискретного канала передачи информации используется псевдослучайная последовательность импульсов, поступающая на информационный вход устройства. Тестовая последовательность сопровождается тактовой частотой, поступающей на тактовый вход устройства. За счет помех в канале в псевдослучайную последовательность вносятся ошибки, которые приводят к замене двоичных символов последовательности на их инверсное значение. Кроме того,за счет ошибок в тактовой последовательности происходят сбои тактовой синхронизации, которые выражаются во вставках либо потерях символов в псевдослучайной последовательности при ее приеме. Последовательность псевдослучайных символов поступает на информационный вход регистра 1 сдвига и сдвигается по нему синхронно с тактовой частотой, поступающей на тактовый вход регистра 1. Длина регистра 1 сдвига равна длине псевдослучайной последовательности и составляет п 2к-1 ячеек, где к 3,4.... Состояние этого регистра анализируется в каждый момент времени, наступающий после очередного тактового импульса, блоком 2 сумматоров по модулю два, количество сумматоров по

п -1 модулю два в котором равно -я- и которые подключены к соответствующим выходам регистра 1.

При отсутствии ошибок в последовательности псевдослучайных символов на каждом такте все сумматоры по модулю два блока 2 будут принимать значения,равные значению символа в последнем разряде ре- гистра 1 сдвига. Таким образом имеется возможность выразить один из символов, находящихся в регистре 1, именно в его последнем разряде, через символы других разрядов регистра 1.

Пороги мажоритарных элементов 3 и 4 устанавливаются следующим образом:

Т - значение порога второго мажоритарного элемента 4 удовлетворяет неравен- ству Т I/2;

Н - значение порога первого мажоритарного элемента 3 удовлетворяет выражению Н I-T.

Если количество единиц на входах мажоритарных элементов 3 и 4 больше или равно Н, то на выходе мажоритарного элемента 3 установится единица, а на выходе

мажоритарного элемента 4 установится ноль.

Если количество единиц на входах мажоритарных элементов 3 и 4 не превосходит пороговый уровень Т, то на выходе мажори:

0 тарного элемента 3 установится ноль, а на выходе мажоритарного элемента 4 - единица.

Если количество единиц на входах мажоритарных элементов 3 и 4 лежит в интер5 вале от Т + 1 до Н - 1, то на выходах мажоритарных элементов 3 и 4 установятся пути, при этом на выходе элемента 6 ИЛИ- НЕ установится единица.

Таким образом, если среди любых п по0 следовательных символов псевдослучайной последовательности, находящихся в регистре 1 сдвига, имеется не более Т ошибочных, то можно правильно определить значение символа в выходном разряде регистра 1.

5 Если количество ошибочных символов лежит в интервале от Т + 1 до Н - 1, что произойдет при нарушении структуры псевдослучайной последовательности в случае сбоя тактовой синхронизации, то на вы0 ходе элемента 6 ИЛИ-НЕ установится единица и тем самым будет зафиксирован факт сбоя тактовой синхронизации.

Сумматор 5 по модулю два вычисляет ошибочные символы. На его входы поступа5 ют сигналы с мажоритарного элемента 3 и символы последнего разряда регистра 1. Если с регистра 1 поступает ошибочный символ, то он не совпадает со значением сигнала с мажоритарного элемента 3 и на

0 выходе сумматора 5 по модулю два устанавливается единица.

Поскольку при сбое тактовой синхронизации в регистре 1 произойдет нарушение структуры псевдослучайной последователь5 ности, то формирование потока ошибок на выходе сумматора 5 по модулю два будет происходить неправильно до тех пор, пока сбой синхронизации не пройдет через регистр 1. На это время выход сумматора 5 по

0 модулю два блокируется сигналом с дешифратора 10 на элементе 9 И. Формирование сигнала на выходе дешифратора 10 происходит следующим образом. При появлении единицы на выходе элемента 6 ИЛИ-НЕ (в

5 момент фиксации сбоя синхронизации) по входу сброса обнуляется счетчик 7. При этом на входе дешифратора 10 устанавливается нулевой код, на который дешифратор 10 отрабатывает нулем на выходе. Этот нулевой сигнал открывает элемент 8 ИЛИ. который пропускает на счетный вход счетчика 7 тактовую частоту с тактового входа устройства. Счетчик считает до тех пор, пока на его выходе не установится число п (в двоичном виде). При этом на выходе дешифратора 10 устанавливается единица, которой закрывается элемент 8-ИЛ И. После чего состояние счетчика 7 и дешифратора 10 остаются без изменения до прихода следующего положительного импульса с выхода элемента 6 ИЛИ-НЕ. Таким образом, при сбое синхронизации на выходе дешифратора 10 вырабатывается отрицательный импульс, длительность которого достаточна для блокирования второго выхода устройства на время прохождения через регистр 1 сбоя синхронизации.

В качестве счетчика 7 можно использовать двоичный счетчик, например типа 155 НЕ7.

Дешифратор 10 представляет собой совокупность логических элементов, реализующих следующую зависимость: на выходе дешифратора 10 имеется единица при наличии на выходе счетчика 7 числа п, и нуль-во всех остальных случаях.

Мажоритарные логические элементы 3 и 4 могут быть реализованы любым способом, например с использованием сумматоров по модулю два.

Следует отметить, что при работе устройства количество единиц на входах мажоритарных элементов, равное значениям от Т + 1 до Н -1, возникает не только при сбоях синхронизации, но и в ситуации, когда на длине п имеется .более Т ошибок. Чтобы снизить вероятность принятия неверного решения в подобном случае, необходимо выбирать п достаточно большим, при этом имеется возможность присваивать Т большие значения.

Например, для двоичного канала без памяти с вероятностью ошибки на символ Ро и пороге Т п/4,

где х -- целая часть числа х,

для разных п вероятность Р (п) того, что на длине п покажется более Т ошибочных символов составит

p(n)S+CnPo(1 -Ро)

,п - 1

1)п 15, Т 3, Р(15) 0.125. 2) п 63, Т 15, Р (63) 0,24-Ю;17 Таким образом по сравнению с прототипом в предлагаемом устройстве за счет введения блока сумматоров по модулю два, элемента ИЛИ-НЕ, сумматора по модулю два. дешифратора, первого и второго мажоритарных элементов имеется возможность определить сбои тактовой синхронизации. Информация об этом вырабатывается на первом выходе устройства. При наличии сбоя синхронизации, за счет нарушения структуры псевдослучайной последовательности в регистре 1 сдвига, устройство будет неверно формировать поток ошибок в течение времени прохождения сбоя синхронизации через регистр 1. На это время второй

выход устройства (выход последовательности ошибок) блокируется сигналом сбоя синхронизации. Тем самым повышается общая достоверность обнаружения ошибок. Предлагаемое устройство для обнаружения ошибок дискретного канала передачи информации может быть реализовано на серийно выпускаемых элементах 564, 133, 533, 1533 серий.

В качестве примера рассмотрим построение и работу устройства для случая К 3, следовательно, п 7. Порождающий полином последовательности и систему проверок находим из литературы.

Порождающий многочлен рассматриваемой псевдослучайной последовательности будет иметь следующий вид

(х7-1)/(х4 + х2 + xf + 1) х3 + х + 1 а система проверок

Эо Эо

a0 ai@a5 а0 а2©аз а

где ©операция суммирования по модулю два.

В соответствии с порождающим многочленом порождаемая им последовательность символов запишется следующим образом

... 111X110011101001110... Г-

п 7

Блок-схема устройства будет иметь вид,

приведенный на фиг. 2. Количество входов

мажоритарных элементов 3 и 4 равно 4. Зададим пороги элементов 3 и 4 следующим

образом:

Т 1, тогда Н 1-Т 4-Т 3.

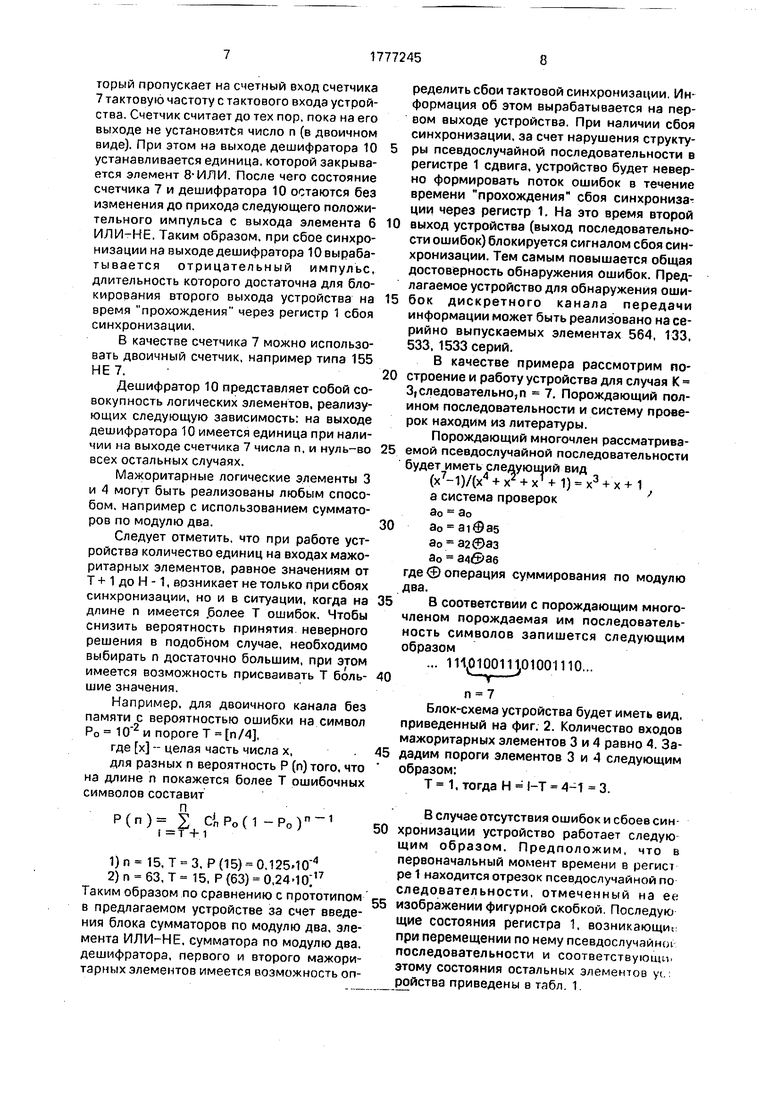

В случае отсутствия ошибок и сбоев син- хронизации устройство работает следую щим образом. Предположим, что в первоначальный момент времени в регист ре 1 находится отрезок псевдослучайной по следовательности, отмеченный на ее изображении фигурной скобкой. Последую щие состояния регистра 1, возникающи1 при перемещении по нему псевдослучайна последовательности и соответствуют. этому состояния остальных элементов yt ройства приведены в табл. 1

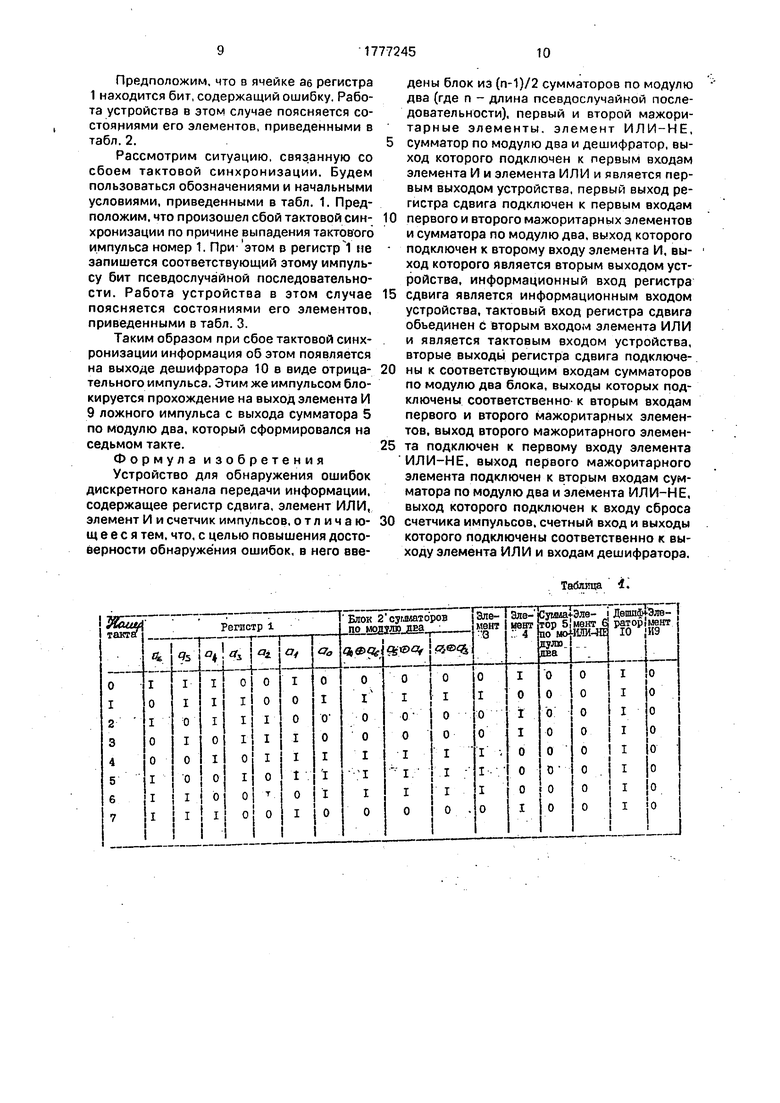

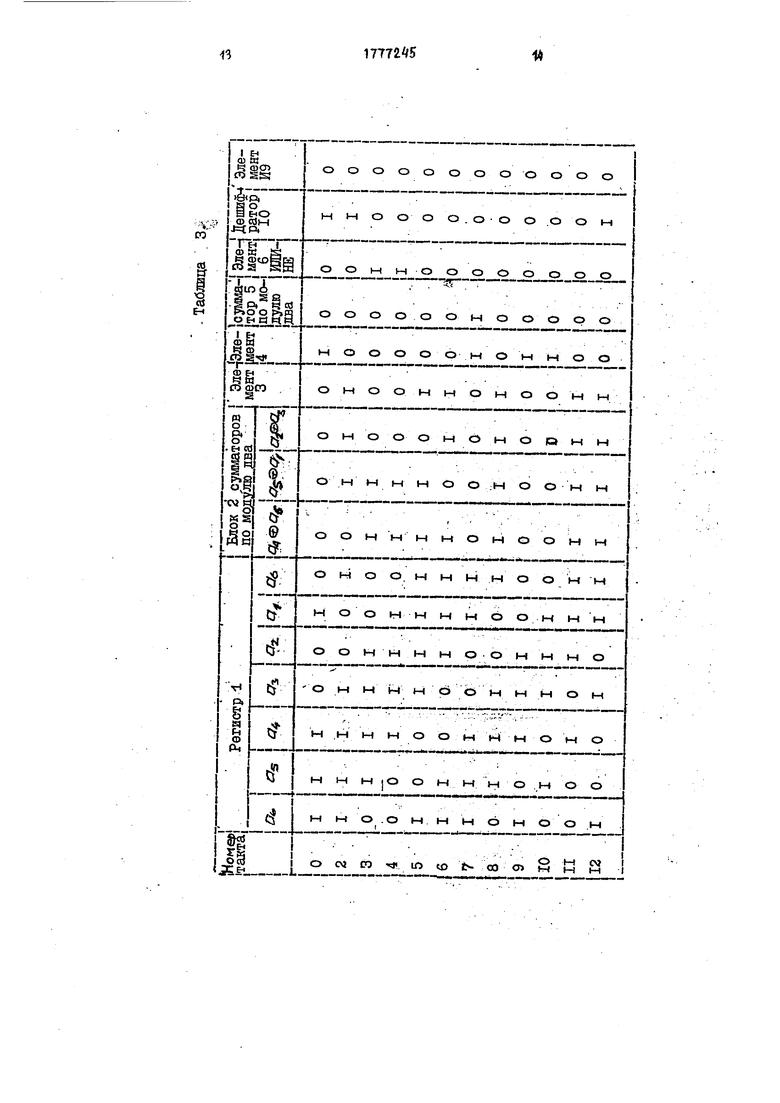

Предположим, что в ячейке ае регистра 1 находится бит, содержащий ошибку. Работа устройства в этом случае поясняется состояниями его элементов, приведенными в табл.2.

Рассмотрим ситуацию, связанную со сбоем тактовой синхронизации. Будем пользоваться обозначениями и начальными условиями, приведенными в табл. 1. Предположим, что произошел сбой тактовой син- хронизации по причине выпадения тактового импульса номер 1. При- этом в регистр не запишется соответствующий этому импульсу бит псевдослучайной последовательности. Работа устройства в этом случае поясняется состояниями его элементов, приведенными в табл. 3.

Таким образом при сбое тактовой синхронизации информация об этом появляется на выходе дешифратора 10 в виде отрица- тельного импульса. Этим же импульсом блокируется прохождение на выход элемента И 9 ложного импульса с выхода сумматора 5 по модулю два, который сформировался на седьмом такте.

Формула изобретения

Устройство для обнаружения ошибок дискретного канала передачи информации, содержащее регистр сдвига, элемент ИЛИ, элемент И и счетчик импульсов, отличаю- щ е е с я тем, что, с целью повышения достоверности обнаружения ошибок, в него введены блок из (п-1)/2 сумматоров по модулю два (где п - длина псевдослучайной последовательности), первый и второй мажоритарные элементы, элемент ИЛИ-НЕ, сумматор по модулю два и дешифратор, выход которого подключен к первым входам элемента И и элемента ИЛИ и является первым выходом устройства, первый выход регистра сдвига подключен к первым входам первого и второго мажоритарных элементов и сумматора по модулю два, выход которого подключен к второму входу элемента И, выход которого является вторым выходом устройства, информационный вход регистра сдвига является информационным входом устройства, тактовый вход регистра сдвига объединен с вторым входом элемента ИЛИ и является тактовым входом устройства, вторые выходы регистра сдвига подключены к соответствующим входам сумматоров по модулю два блока, выходы которых подключены соответственно- к вторым входам первого и второго мажоритарных элементов, выход второго мажоритарного элемента подключен к первому входу элемента ИЛИ-НЕ, выход первого мажоритарного элемента подключен к вторым входам сумматора по модулю два и элемента ИЛИ-НЕ, выход которого подключен к входу сброса счетчика импульсов, счетный вход и выходы которого подключены соответственно к выходу элемента ИЛИ и входам дешифратора.

Таблица 4.

flit.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

| Пороговый декодер сверточного кода | 1989 |

|

SU1667264A1 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| Устройство синхронизации с М-последовательностью | 1985 |

|

SU1312750A2 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1983 |

|

SU1172056A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2008 |

|

RU2390943C1 |

| Устройство для контроля ошибок аппаратуры многоканальной магнитной записи | 1988 |

|

SU1580438A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И РЕГИСТРАЦИИ ОШИБОК ДИСКРЕТНОГО КАНАЛА ПЕРЕДАЧИ И НАКОПЛЕНИЯ ИНФОРМАЦИИ | 1985 |

|

SU1378757A1 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

Изобретение может быть использовано в аппаратуре для статистических исследований дискретных каналов связи и средств накопления информации. Целью изобретения является повышение достоверности обнаружения ошибок. Устройство для обнаружения ошибок содержит регистр 1 сдвига, блок 2 сумматоров 4 по модулю два, первый мажоритарный элемент 3,сумматор 5 по модулю два, второй мажоритарный элемент 4, элемент 6 ИЛИ-НЕ, элемент 8 ИЛИ, счетчик 7 импульсов, дешифратор 10, элемент 9 И. Введение второго мажоритарного элемента, элементов ИЛИ-НЕ, И, ИЛИ, счетчика и дешифратора позволяет регистрировать сбои тактовой синхронизации в исследуемом канале, а также блокировать выход обнаружения ошибок на время отработки устройством сбоя синхронизации, в течение которого происходит неправильное формирование потока ошибок. При этом порог срабатывания первого мажоритарного элемента выбирается большим, чем I/2, а второго - меньшим, чем I/2, где I - количество входов мажоритарного элемента. Тем самым повысится общая достоверность обнаружения ошибок. 2 ил., 3 табл. &

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для определения необнаруживаемых ошибок линейных кодов | 1985 |

|

SU1338076A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 1378557, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1992-11-23—Публикация

1990-08-16—Подача