Иаобрегение относигея к обласги вычислительной техники и может быть иопользовано в сгохасгических вычислигельиных машинах для возведения в К степень чисел, представленных в двоичной. форме.

Известно множительное устройство, содержащее регистры числа, логические элемен1Ы, работ ающие по вероятностно-импульсному принципу Flj . Однако точность этого устройства ограничена.

Наиболее близким техническим решением к данному изобретению является устройство для возведения двоичных чисел Б квадрат, содержащее счетчик, счетный

вход которого через элемент И соединен с выходами блока элементов ИЛИ, первая и вторая группы входов которого соединены с выходами первого и второго коммутаторов соответственно, першае группы входов которых соединены с выходами регистра числа соответственно 2J .

В этом устройстве двоичное число преобразуется в К случайных последовбнтельностей с вероятностями появления

импульса, пропорциональными исходному числу. Указанный метод кодирования позволяет применить К-входовый элемент И для возведения двоичного числа в К-ю степень, что существенно упрощает схему множительного устройства. Однако при представлении двоичного числа случайнв ми последовательностями точность вычислений находится в зависимости от длинц декодируемой с помощью счетчика последовательности, представляющей результат вычислений. Поэтому достижение высокой точности вычислений приводит к значительному снижению быстродействия устройства.

Целью изобретения является повышение быстродействия устройства.

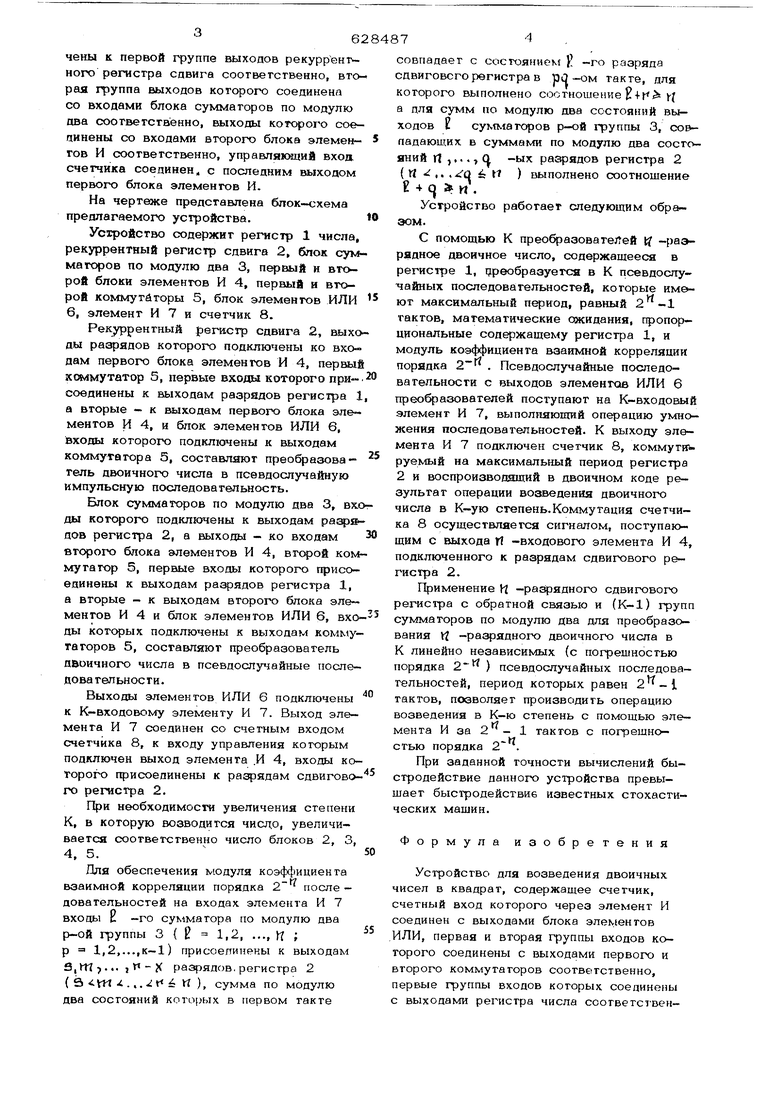

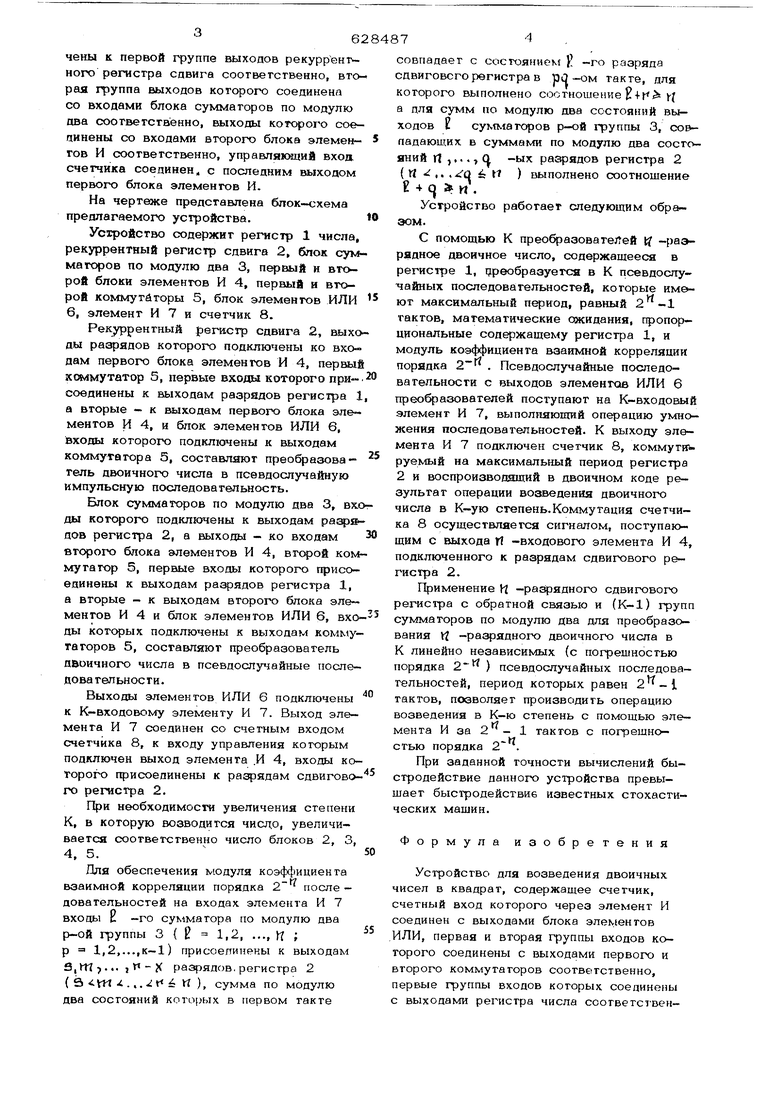

Пля достижения поставленной цели предлагаемое устройство содержит рекуррентный регистр сдвига, блок сумматоров по модулю два, первый и второй блоки элементов И, выходы которых пгодключены ко вторым группам входов первого и вгорого коммутаторов соответственно, входы первого блока элементов И подключены к первой группе выхопов рекурр ент ного регистра сдвига соогвегсгвенно, вто рая группа выходов которого соединена со входами блока сумматоров по модулю два соогветственно, выходы которого соединены со входами второго блока элеменгов И соответственно, управляющий вход счетчика соединен, с последним выходом первого блока элементов И. На чертеже представлена блок-схема предлагаемого устройства. Устройство содержит регистр 1 числа, рекуррентный регистр сдвига 2, блок сум маторов по модулю два 3, первый и второй блоки элементов И 4, первый и вгорой коммутаторы 5, блок элементов ИЛИ 6, элемент И 7 и счетчик 8. Рекуррентный регистр сдвига 2, выхо ды разрядов которого подключены ко входам первого блока элементов И 4, пер шл коммутатор 5, первые входы которого присоединены к выходам разрядов регистра 1 а вторые - к выходам первого блока элементов И 4, и блок элементов ИЛИ 6, входы которого подключены к выходам коммутатора 5, составляют преобразователь двоичного числа в псевдослучайную импульсную последовательность. Блок сумматоров по модулю два 3, вх ды которого подключены к выходам раар дов регистра 2, а выходы - ко входам второго блока элементов И 4, второй ком мутат-ор 5, первые входы которого npvico- единены к выходам разрядов регистра 1, а вторые - к выходам второго блока эле ментов И 4 и блок элементов ИЛИ 6, вхо ды которых подключены к выходам комму таторов 5, составляют преобразователь двоичного числа в псевдослучайные после- дова тепьносги. Выходы элементов ИЛИ 6 подключены к К-входовому элементу И 7. Выход элемента И 7 соединен со счетным входом счетчика 8, к входу управления которым подключен выход элемента .И 4, входы ко торого присоединены к разрядам сдвигово го регистра 2. При необходимости увеличения степени К, в которую возводится чисдо, увеличивается соответственно число блоков 2, 3 4, 5. Для обеспечения модуля коэф41ициента взаимной корреляции порядка 2 после довательностей на входах элемента И 7 входы В -го сумматора по модулю два р-ой группы 3 (2 1, ; р 1,2,...,к-1) присоепипекы к выходам S,nt ... J - X . регистра 2 (..- К ), сумма по модулю два состояний которых в первом такте совпадает с состоянием Н -го разряда двигового регистра в ро-ом такте, для которого выполнено соотношение Е + 1 Ц а для сумм по модулю гша состояний выходов Е cyivfMaторов р-ой группы 3, совпадающих Б суммами по модулю два состояний rt ,,.., О -ых разрядов регистра 2 ( W ,. .о ir t7 ) выполнено соотношение Н 9 Устройство работает следующим образом, С помощью К преобразователей Vt -раэрядное двоичное число, содержащееся в регистре 1, цреобразуется в К псевдослу чайных последовательностей, которые имеют максимальный период, равный 2-1 тактов, математические ожидания, пропорциональные содержащему регистра 1, и модуль коэффициента взаимной корреляции порядка 2 . Псевдослучайные последовательности с выходов элементхав ИЛИ 6 преобразователей поступают на К-входовый элемент И 7, выполняющий операцию умножения последовательностей. К выходу элемента И 7 подключен счетчик 8, коммутируемый на максимальный период регистра 2 и воспроизводящий в двоичном коде результат операции возведения двоичного числа в К-ую степень.Коммутация счетчика 8 осуществляется сигналом, поступающим с выхода Ц -входового элемента И 4, подключенного к разрядам сдвигового регистра 2. Применение П -разрядного сдвигового регистра с обратной связью и (К-1) групп сумматоров по модулю два для преобразования 1 -разрядного двоичного числа в К линейно независимых (с погрешностью порядка 2 ) псевдослучайных последовательностей, период которых равен тактов, позволяет производить операцию возведения в К-ю степень с помощью эле- мента И за 1 тактов с по грешно- стью порядка 2 При заданной точности вычислений быстродействие данного устройства превышает быстродействие известных стохастических машин. ула изобретения Устройство для возведения двоичных чисел Б квадрат, содержащее счетчик, счетный вход которого через элемент И соединен с выходами блока элементов ИЛИ, первая и вторая группы входов которого соединены с выходами первого и второго коммутаторов соответственно, первые группы входов которых соединены с выходами регистра числа соответствен

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностное суммирующее устройство | 1975 |

|

SU737948A1 |

| Стохастическое устройство для деления двоичных чисел | 1978 |

|

SU769550A1 |

| Стохастическое устройство для деления и умножения | 1975 |

|

SU741275A1 |

| Вероятностное устройство для выполнения математических операций | 1980 |

|

SU932494A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1980 |

|

SU940168A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Псевдостохастический сумматор | 1981 |

|

SU982003A1 |

| Псевдостохастическое устройство для выполнения математических операций | 1983 |

|

SU1233151A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Генератор псевдослучайных последовательностей | 1981 |

|

SU1023325A1 |

Авторы

Даты

1978-10-15—Публикация

1975-03-07—Подача