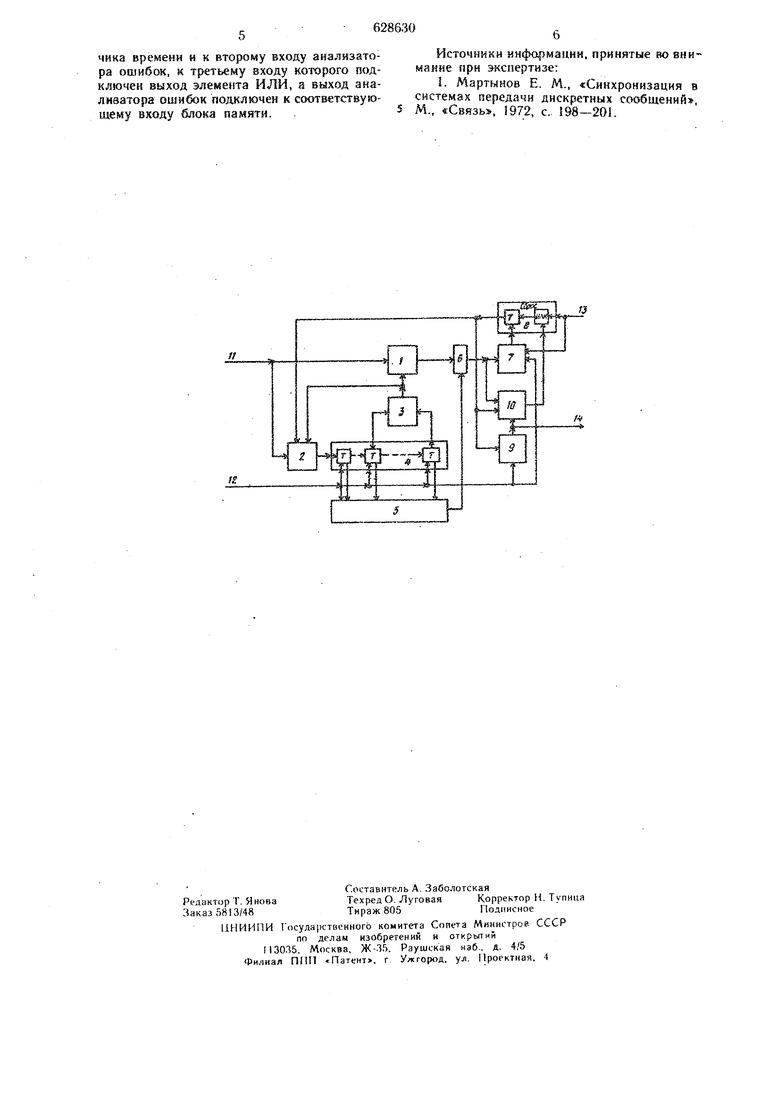

ющих разрядов которого подключены через элемент запрета 5 к первому входу элемента ИЛИ 6, к второму входу последнего подключен выход первого блока сравнения 1, а выход элемента ИЛИ 6 через последовательно соединенные счетчик 7, блок памяти 8 и коммутатор 2 подключен к входу регистра сдвига 4, причем на соответствующие входы разрядов регистра сдвига 4, элемента запрета 5 и счетчика 7 поданы тактовые импульсы, а на соответствующие входы блока памяти 8 и счетчика 7 - импульсы «Исходное состояние, последовательно соединенные датчик 9 времени, и анализатор ошибок 10, при этом выход блока памяти 8 подключен к входу датчяка 9 времени и к второму входу анализатора ошибок 10, к третьему входу которого подключен выход элемента ИЛИ 6, а выход анализатора ошибок 10 подключен к соответствующему входу блока памяти 8, кроме того, предлагаемый анализатор содер жнт информационный вход II, шину 12 тактовых импульсов, шину 13 импульсов «Исходное состояние и выход 14 устройства. Анализатор рекуррентного сигнала фазевого пуска работает следующим образом. На элемент памяти В и счетчик 7 по шиме 13 импульсов исходное состояние поступает импульс, устанавливающий их в исходное состояние, кроме того, соответствующие входы регистра сдвига 4, счетчика 7 и датчика 9 времени прнсоединяются к шине 12 тактовых импульсов. В исходном состоянии вход регистра сдвига 4 через коммутатор 2, управляемый элементом памяти 8, подключается к инфор.мационному входу 11, счетчик 7 начинает счет, а анализатор ошибок 10 и датчик 9 времени устанавливаются элементом памяти 8 в исходное состояние и удерживается в нем. Блок сравнения 3 по информации, записываемой в регистр сдвига 4 с внформационного входа 11, формирует последовательность импульсов, с которой в блоке срапнения I, сравнивается сигнал, приходящий на информационный вход 11. При отсутствии сигнала на информационном входе I срабатывает элемент запрета 5 и через элемент ИЛИ 6 возвращает счетчик 7 к началу счета. При появлении во входном сигнале неискаженного участка, минимальное число символов в этом участке может равняться удвск нному числу разрядов регистра сдвига 4, счетчик 7 формирует на

своем выходе импульс, опрокидывающий элемент 8, который при помощи коммутатора 2 замыкает обратную связь регистра сдвига 4, Г1роходящую через блок сравнения 3. Одновременно элемент памяти 8 разрешает работу анализатора 10 ошибок и датчика 9 времени.

С замыканием обратной связи регистра сдвига 4 на выходе блока сравнения 3 начинается автономное формирование опорной

щие входы, разрядов регистра сдвига, элемента запрета и счетчика поданы тактовые импульсы, а на соответствующее входы блока памяти и счетчика поданы импульсы «Исходное состояние, отличающийся тем, что, с целью сокращения времени анализа рекуррентного сигнала .при наличии помех, в него введены последовательно соединенные датчик времени и анализатор ошибок, при этом выход блока памяти подключен к входу датпоследовательности на основе символов выявленного неискаженного участка. В то же время анализатор ошибок 10 начинает подсчет несовпадаюплих символов, выявленных блоком .сравнения I, а датчик 9 времени начинает отсчет времени. Если за время,определяемое датчиком 9 времени, число несовпадающих снмваюв не превыщает порог анализатора 10 ошибок, то датчик времени 9 вырабатывает импульс, запрещающий работу анализатора 10 ошибок и поступающий на выход 14 анализатора рекуррентного сигнала. Если до срабатывания датчика 9 времени анализатор 10 ошибок выявляет превышение допустимого порога ошибок количеством несовпадающих символов, то элемент памяти 8 сразу возвращается в исходное состояние. Тем самым запрещается работа анализатора 10 и датчика 9, они возвращаются в исходное состояние. Одновременно размыкается обратная связь регистра сдвига 4 коммутатором 2, и счетчик 7 начинает вновь выявление неискаженного участка. Введение в анализатор рекуррентного сигнала фазового пуска анализатора ошибок и датчика времени позволяет уменьшить время выявления рекуррентного сигнала при сохранении той же защиты, что и в известном устройстве от ложного выявления рекуррентного сигнала из помех и посторон„его псевдослучайного сигнала. Благодаря этому сокращается общее время вхождения в синхронизм, т.е. повышается ожративность работы систем синхронизации. Формула изобретения Анализатор рекуррентного сигнала фазового пуска, содержащий объединенные по информационному входу первый блок срявнения и коммутатор, к вторым в,ходам которых подключен выход второго блока сравнения, к входам которого подключены выходы соответствующих разрядов регистра сдвига, другие выходы соответствующих разрядов которого подключены через элемент запрета, к первому входу 31 1емента ИЛИ, к второму входу которого подключен выход первого блока сравнения, а выход элемента ИЛИ через последовательно соединенные счетчик, блок памяти и коммутатор подключен к входу регистра сдвига, причем на соответствуючика времени и к второму входу анализатора ошибок, к третьему входу ко1Х)рого подключен выход элемента ИЛИ, а выход аналиватора ошибок подключен к соответствующему входу блока памяти.

Источники ннфо|)мацнн, принятые во внимание при экспертизе;

1. Мартынов Е. М., «Синхронизация в системах передачи дискретных сообщений М., «С8язь. 1972, с.. 198-201.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазового пуска приемника дискретной информации | 1976 |

|

SU570212A1 |

| Анализатор рекуррентного сигнала фазового пуска | 1981 |

|

SU995361A2 |

| Устройство для выделения рекуррентного синхросигнала | 1983 |

|

SU1116547A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Устройство для измерения проскальзываний цифровых сигналов | 1989 |

|

SU1674388A1 |

| Датчик случайных чисел | 1984 |

|

SU1229760A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙКОМБИНАЦИИ | 1971 |

|

SU293243A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО для ЭКСПЕРИМЕНТАЛЬНОГО ИССЛЕДОВАНИЯ | 1971 |

|

SU297963A1 |

| Устройство для синхронизации двоичной линейной рекурентной последовательности | 1972 |

|

SU445993A1 |

//

Авторы

Даты

1978-10-15—Публикация

1977-04-06—Подача